# SR11000 向け実行資源均等化命令スケジューリング

## 橋本 博幸 本川 敬子 久島 伊知郎

## (株) 日立製作所システム開発研究所

スーパーテクニカルサーバ SR11000 モデル J1 に搭載されている POWER5 プロセッサでは、数命令ずつグループ化して グループ単位で命令の発行・完了などを行っている。POWER5 ではこのグループ内の位置(スロット)により利用する実行資源が固定されている。このため、ロード/ストアや浮動小数点演算などの実行資源は2個ずつ実装されているが、ある実行資源を利用する命令がグループ内の特定のスロットにのみ存在する場合、2 つのうち一方の実行資源だけを使うため、もう一方の実行資源が利用されず、最大性能が引き出せないという問題が生じる。そこで、グループ内の命令配置位置を考慮する 実行資源均等化命令スケジューリングを開発した。実数型の基本演算プログラムに適用した結果、総和計算で約21%、加算計算で約16%の性能向上が得られた。

# Execution resource equal-ized instruction scheduling for SR11000

# Hiroyuki Hashimoto, Keiko Motokawa and Ichiro Kyushima Systems Development Laboratory, Hitachi, Ltd.

In POWER5 processor mounted in super technical server SR11000 model J1, instruction issue, completion, etc. are performed per group which consists of some instructions. In POWER5, the execution resources used with the position(slot) in this group are fixed. For this reason, although two execution resources such as load/store and a floating point arithmetic, are mounted, when the instruction using a certain execution resource exists only in a specific slot in a group, another execution resources are not used, and the problem that the maximum performance cannot be pulled out arises. To solve this problem, the execution resources equal-ized instruction scheduling which considers the instruction arrangement position in a group was developed. As a result of applying to a series of basic floating-point arithmetic programs, about 21% of improvement in a performance was obtained for summation, and about 16% of improvement for addition calculation.

#### 1. はじめに

近年のRISC プロセッサは1マシンサイクルで複数の命令実行が可能なスーパースカラ機能を搭載しており、コンパイラにおける命令スケジューリングでは並列実行可能な命令をなるべく同一サイクルにスケジュールするという手法が用いられてきた。この手法では、並列実行できる命令を見つけることが重要であって、並列実行できる命令間の静的な順序関係は特に考慮する必要がなかった。しかし、SR11000 モデルJ1 に搭載しているPOWER51プロセッサでは、1マシンサイクルで実行する複数の命令をグループという単位で管理しており、グループ単位で命令の発行・完了を行っている1<sup>12</sup>。このとき、グループ内の位置(スロット)により利用できる実行資源が固定されているため、ある実行資源を使用する命令が常に特定のスロットに配置されていた場合、常に同

じ実行資源だけを利用することになる。そのため、他の実行 資源に空きができてしまい、プロセッサの持つ能力を使い切 ることができないという問題が発生する。つまり、POWER5 プロセッサを搭載したシステムで実行資源を最大限に利用 するためには、同時実行可能な命令を見つけることだけでな く、それらの命令をグループ内でどのように配置するかを考 慮できるスケジューラが必要になる。

そこで、グループ内の命令配置を考慮できるスケジューリングとして、実行資源均等化命令スケジューリング手法の検討と開発を実施した。本稿では、今回開発した命令スケジューリング手法およびその評価結果について述べる。

## 2. POWER5 の命令発行機構

## 2.1 命令発行機構

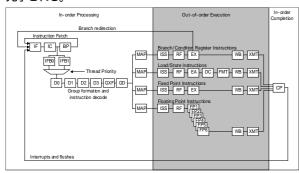

まずPOWER5 での命令発行機構について説明する。 図 1 に POWER5 プロセッサの実行パイプラインを示す。

<sup>1</sup> POWER5 は米国 IBM Corp.の商標です。

図中の小さな箱がパイプラインのステージを示している。命令はIF ステージによりフェッチされた後、D0~D3 ステージでグループの形成が行われる。分岐命令があるとそこでグループが区切られる。その結果、グループは 1~5 命令で形成される3。グループ形成後 GD ステージでグループのディスパッチが行われ、MAP ステージで各種別(ロード・ストアユニット、固定小数点ユニット、浮動小数点ユニットなど)の実行資源の割り当てが行われる。実行資源割り当ての済んだ命令はISS ステージで命令発行キューに入れられ、命令発行キューに入った命令は Out-of-order 実行される。自グループより古いすべてのグループが完了し、自グループ内の全命令の実行が終了した時点で CP ステージにより自グループの実行が完了される。

図1 POWER5 の実行パイプライン (<sup>文献2より)</sup>

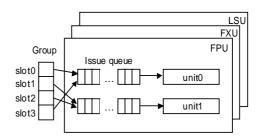

次に図2を用いてグループのディスパッチから実行までの 過程で、ディスパッチされた命令がどのように実行資源を使 用し実行されるかについて説明する。

POWER5 プロセッサでは、ロード・ストアユニット(LSU)、 固定小数点ユニット(FXU)、浮動小数点ユニット(FPU)に対 しそれぞれ 2 個ずつの実行資源(ユニット=unit0/1)を持って おり、それぞれのユニットは同時に実行可能である。また、 FPU は 12 エントリの命令発行キューを 2 個、LSU/FXU は 共有の18エントリの命令発行キューを2個持っている。そ れぞれの命令発行キューは利用するユニットが決まってい る。どちらの命令発行キューに入るかは、ディスパッチされ たグループ内のどの位置に命令が配置されているかによっ て決められている。このグループ内の位置のことをスロット と呼ぶ。スロットは0~4までがあり、通常の命令はスロット 0~3 に配置され、分岐命令は常にスロット 4 に配置される。 スロット0とスロット3に配置された命令は命令発行キュー 0 と unit 0 を、スロット 1 とスロット 2 に配置された命令は 命令発行キュー1 と unit1 を利用する。このように、利用す る実行資源(ユニット等)はディスパッチされるグループ内の

スロット番号によって決まってしまうため、複数ある実行資源を有効利用するためには、命令発行キューに均等に命令を供給することが重要になる。この命令発行キューの使用に偏りがあると、実行資源の利用頻度に偏りが生じ、実行性能が低下するという現象が発生することがある。そのため、この性能低下を回避するために、各命令種別で命令発行キューに命令を均等に供給するための命令スケジューリングが必要になる。

図2 実行資源の利用状態 (対 1,2 より)

#### 2.2 予備調査

グループ内の命令配置状況により性能がどのように変化 するかの予備調査を行った。測定プログラムの最内側ループ の一部を図3に示す。実際に測定を行ったループは、図3に 示した5グループの命令列の後方に同様の命令例で5グルー プ、合計 10 グループからなるものである。測定はこのルー プを持つ関数を複数回呼び出すことによって行った。なお、 実行資源の利用状況と実行性能の関係を調べるため、ループ 内の命令列はレジスタ間の依存が極力少なくなるようにし た。測定プログラムの説明を行う。コード(a)は、スロット 0,3 に FPU を利用する命令を、スロット 1,2 に FXU を利用 する命令を並べたものである。この命令列では、FPUはunit0 だけを、FXU は unit1 だけを利用することになる。 コード(b) は、スロット 0,1 に FPU を利用する命令を、スロット 2,3 に FXU を利用する命令を並べたものである。この命令列で は、FPUとFXUがunit0とunit1を均等に利用することに なる。ただし、FPU はスロット 0.1 だけを、FXU はスロッ ト 2,3 だけを利用している。 コード(c)は、 unit0/1 の均等利用 だけでなく、FPU、FXU が使用するスロットも均等になるよ うに命令を並べたものである。

表1にそれぞれのコードのSR11000モデルJ1上での実行性能比較結果を示す。表1より、コード(a)の実行性能を1とした場合にコード(b)で1.52倍、コード(c)で1.53倍速く実行できることが分かる。この結果より、実行性能を向上させるためには、実行資源を均等に利用するコードを生成することが重要である。

<sup>&</sup>lt;sup>2</sup> 通常は4命令で1グループを形成する。5命令目に分岐命令がある場合は、5命令で1グループとなる。

<sup>3</sup> このとき、複雑な命令を2つ以上の単純な命令に分割する クラッキング処理も実施される。

<sup>4</sup> コード(c)の後半5 グループの命令配置は、前半5 グループ の fadd/add の位置が反転したものとなる。

| Gro | slot |      | コード(a)         | FF | PU | F) | (U |      | コード(b)         | FF | PU       | Fλ | (U |      | コード(c)         | FF  | PU | FX  | ίU |

|-----|------|------|----------------|----|----|----|----|------|----------------|----|----------|----|----|------|----------------|-----|----|-----|----|

| up  | 5101 |      | ⊐ 1'(a)        | 0  | 1  | 0  | 1  |      | ⊐ - 1·(b)      | 0  | 1        | 0  | 1  |      | J-1-(C)        | 0   | 1  | 0   | 1  |

|     | 0    | fadd | fr0,fr1,fr2    |    |    |    |    | fadd | fr0,fr1,fr2    |    |          |    |    | fadd | fr0,fr1,fr2    |     |    |     |    |

| 1   | 1    | add  | r3,r4,r5       |    |    |    |    | fadd | fr3,fr4,fr5    |    |          |    |    | fadd | fr3,fr4,fr5    |     |    |     |    |

| Ι'  | 2    | add  | r6,r7,r8       |    |    |    |    | add  | r3,r4,r5       |    |          |    |    | add  | r3,r4,r5       | l 1 |    |     |    |

|     | 3    | fadd | fr3,fr4,fr5    |    |    |    |    | add  | r6,r7,r8       |    |          |    |    | add  | r6,r7,r8       |     |    |     |    |

|     | 0    | fadd | fr6,fr7,fr8    |    |    |    |    | fadd | fr6,fr7,fr8    |    |          |    |    | add  | r9,r10,r11     |     |    |     |    |

| 2   | 1    | add  | r9,r10,r11     |    |    |    |    | fadd | fr9,fr10,fr11  |    |          |    |    | add  | r12,r13,r14    |     |    |     |    |

| -   | 2    | add  | r12,r13,r14    |    |    |    |    | add  | r9,r10,r11     |    |          |    |    | fadd | fr6,fr7,fr8    |     |    | . [ |    |

|     | 3    | fadd | fr9,fr10,fr11  |    |    |    |    | add  | r12,r13,r14    |    |          |    |    | fadd | fr9,fr10,fr11  |     |    |     | ,  |

|     | 0    | fadd | fr12,fr13,fr14 |    |    |    |    | fadd | fr12,fr13,fr14 |    |          |    |    | fadd | fr12,fr13,fr14 |     |    |     |    |

| 3   | 1    | add  | r15,r16,r17    |    |    |    |    | fadd | fr15,fr16,fr17 |    |          |    |    | fadd | fr15,fr16,fr17 |     |    |     |    |

| ٦   | 2    | add  | r18,r19,r20    |    |    |    |    | add  | r15,r16,r17    | Ì  | $\sqcap$ |    |    | add  | r15,r16,r17    |     |    |     |    |

|     | 3    | fadd | fr15,fr16,fr17 |    |    |    |    | add  | r18,r19,r20    |    |          |    |    | add  | r18,r19,r20    |     |    |     |    |

|     | 0    | fadd | fr18,fr19,fr20 |    |    |    |    | fadd | fr18,fr19,fr20 |    |          |    |    | add  | r21,r22,r23    |     |    |     |    |

| 4   | 1    | add  | r21,r22,r23    |    |    |    |    | fadd | fr21,fr22,fr23 |    |          |    |    | add  | r24,r25,r26    |     |    |     |    |

| -   | 2    | add  | r24,r25,r26    |    |    |    |    | add  | r21,r22,r23    | Ì  |          |    |    | fadd | fr18,fr19,fr20 |     |    | Ī   |    |

|     | 3    | fadd | fr21,fr22,fr23 |    |    |    |    | add  | r24,r25,r26    |    |          |    |    | fadd | fr21,fr22,fr23 |     |    |     |    |

|     | 0    | fadd | fr24,fr25,fr26 |    |    |    |    | fadd | fr24,fr25,fr26 |    |          |    |    | fadd | fr24,fr25,fr26 |     |    |     |    |

| 5   | 1    | add  | r27,r28,r29    |    |    |    |    | fadd | fr27,fr28,fr29 |    |          |    |    | fadd | fr27,fr28,fr29 |     |    |     |    |

|     | 2    | add  | r30,r31,r0     |    |    |    |    | add  | r27,r28,r29    |    | П        |    |    | add  | r27,r28,r29    | ΙÌ  |    |     |    |

|     | 3    | fadd | fr27,fr28,fr29 |    |    |    |    | add  | r30,r31,r0     |    |          |    |    | add  | r30,r31,r0     |     |    |     |    |

表1 実行性能

| コード | 相対性能 |

|-----|------|

| (a) | 1.00 |

| (b) | 1.52 |

| (c) | 1.53 |

図3 測定プログラム(最内側ループの一部)

## 3 実行資源均等化命令スケジューリング

### 3.1 処理手順

本節では実行資源均等化命令スケジューリングの処理手順について説明する。スケジューリングでは命令の配置順が問題になるため、基本プロックの先頭に配置できる命令から順に探す、いわゆる cycle-based のリストスケジューリング3を行うものとする。つまり、既に配置した命令間に別の命令を配置することはしないものとする。また、命令間の定義-使用に関するレイテンシも必ず考慮する。つまり、資源のバランスを取るために、レイテンシの解消されてない命令を持ってきて配置することはしない。

以下図4を用いてアルゴリズムの詳細説明を行う。

まず始めに、[1]でスケジューリング前の各実行資源利用数をカウントしておく。次に[2]では、スケジューリング対象としている基本ブロック内の命令の依存関係を調べDAG(Directed Acyclic Graphs)と、スケジューリング結果を格納するスケジュール表を作成する。[3]では、現在のスロット番号を保持する変数(slot\_no)の初期化を行う。グループの先頭は必ずスロット番号0なので、初期値は0になる。[4]-[23]でDAG内の全命令に対し、スケジューリングを行う。[5]では、DAG中の未スケジューリング命令のうち、レイテンシが解消され現在のスロットに配置可能な命令の集合を求める。これを、配置可能命令集合と呼ぶ。この集合は、基本ブロック内のすべての命令から候補を探す方法と、スケジュール前にグループ分けを行い、グループ間の移動が発生しない命令から候補を探す方法の2つを今回試した。

[6]-[23]で配置可能命令集合が空になるまで[7]以下の処理を行う。[7]では、現在のスロットに命令を配置した場合に、各命令種別が利用する実行資源のバランスがどうなるかを

```

1: 実行資源利用数のカウント

2: DAG, スケジュール表の作成

3: slot_no=0

4: while (DAG に印の付いてない命令がある) {

5:

配置可能命令集合を求める

while (配置可能命令集合が空になるまで) {

6:

命令種別ごとに優先順位(高/低)を決定する

7:

8:

優先順位ごとに命令種別のソート

9:

for (優先順位高命令種別の数) {

if (配置可能命令集合内に同一種別の命令が存在する) {

10:

スケジュール表に登録

11:

DAG に印を付ける

12:

13:

goto next_slot

14:

for (優先順位低命令種別の数) {

15.

16.

if (配置可能命令集合内に同一種別の命令が存在する) {

17:

スケジュール表に登録

18:

DAG に印を付ける

19:

goto next slot

20:

21: next_slot:

22:

スロット番号(slot_no)の更新

23:

} }

24: スケジュール表から実行資源利用数をカウント

25: if (実行資源バランスが改善された) {

命令の並び換え

27: }

```

図4 スケジューリングアルゴリズム

調べ、命令種別毎に優先順位を決定する。ここで命令種別とは、LSU/FXU/FPUのいずれかである。ここでは、ある実行資源と他方の実行資源との利用数の差を計算し、差が2以上になる場合は、その命令配置により資源利用数パランスが崩れると判断し、その命令種別の優先順位を「低」にセットする。バランスが崩れないと判断した場合は、優先順位を「高」にセットする。スロットに配置可能な命令が複数存在する場合、この命令種別の優先順位に従って配置する命令を選択することになる。バランスを調べる実行資源としては、ユニットとスロットの2つが考えられる。

<sup>&</sup>lt;sup>5</sup> 事前にスロットを意識しない(従来の)命令スケジューリングを行っておく。

[8]では、優先順位が「高」または「低」として登録された 命令種別が複数ある場合、さらにその中での優先順位を決定 する。優先順位は、命令種別ごとに現在のユニット利用最少 数を求め、利用数の少ない命令種別の順位が高くなるように セットする。これは、これ以前に配置された命令列で使用した命令種別のうち、一番少ないものを優先的に割り付けることにより、命令種別ごとのバランスを整えるための処理である。異なる種別で利用数が同じ場合は、あらかじめ決められた優先順に従って並び変える。

[9]-[14]では、[8]でソートされた命令種別の順に、配置可能命令集合内にその種別の命令が存在するかを調べる。命令が存在する場合は、その命令を配置可能としてスケジュール表に登録し、DAG にスケジュール済みという印を付ける。配置可能命令が複数ある場合は、スケジューリング前の命令並びで先に出現するものを選択する。もし配置可能命令がない場合は、[15]-[20]で、優先順位低命令種別の中から配置する命令を探す。

[22]ではグループ内の 1 命令が配置されたため、次の命令 配置のためにスロット番号を更新する。なお、スロット番号 は最大 3 までなので、3 の次の更新値は 0 となる。

すべての命令の配置が終了した後[24]でスケジュール表に配置された命令列から実行資源の利用数をカウントする。そして[25]で、スケジューリングにより実行資源利用数のバランスが改善されたかどうかを調べる。これは、実行資源ごとに利用数の最多のものから最少のものの差を計算し、その差が小さくなったかどうかで判断する。この差が小さくなったか、変わらない場合、バランスが改善されたものとみなし、[26]でスケジュール表に従って命令の並べ変えを行う。なお、バランスが改善されなかった場合は、スケジューリング結果を破棄し、スケジューリング前の命令列を結果として返す。このバランスを調べる実行資源としては、ユニットとスロットが考えられる。

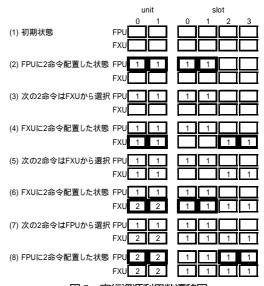

次に、実際のスケジュール手順を図3コード(a)の命令列を使って説明する。この例では、図4[5]の配置可能命令集合を基本プロック内から探し、図4[7]の優先順位決定時の実行資源チェックはユニットとスロットに対して行うものとする。

初期状態(図5(1))の後、基本プロックの先頭(slot0)に配置できる命令を基本プロック内から探す。ここでは、図中の20命令すべてが配置可能命令集合として登録される。次に[7]で、各命令種別のバランスを調べる。例えば、slot0にFPU種別の命令を配置した場合、FPUのunit0とslot0の利用数が1となり、unit0とunit1またはslot0とslot1/2/3との差が1なので、バランスは崩れないと判定され、FPUは優先順位高として登録される。同様にFXUもバランスが崩れないと判定され、優先順位高として登録される。[8]で優先順位高命令種別のソートを行うが、ユニット利用数の最少数が共に0であるので、あらかじめ決めてある優先順にソートする。ここではFPUの優先順が高いとし、FPU,FXUの順で並ぶ

ものとする。[9]-[14]では、優先順の高い FPU 命令(fadd fr0, fr1, fr2)が選択され、スケジュール表に配置される。スケジュール後[22]でスロット番号の更新(slot\_no=1)を行い、次に配置する命令を考える。

slot1に FPU 種別の命令を配置した場合、FPU の unit1と slot1の利用数が 1となる。他の実行資源との差を調べると、unit0と unit1の差は 0で、slot1と slot0/2/3との差は 1となる。そのため、利用数のバランスは崩れないと判定され、FPU が優先順位高として登録される。同様に FXU も優先順位高として登録される。命令の選択では、それぞれの種別の利用最少数が共に 0(まだ slot1へは配置してないため)なので、優先順の高い FPU 命令(fadd fr3, fr4, fr5)が選択されスケジュール表へ配置される(図 5(2))。

次はslot2に配置可能な命令を探す。ここで、FPU種別の命令を配置した場合、FPUのunit1の利用数が2、slot2の利用数が1となる。他の実行資源との差を調べると、unit0とunit1の差は1で、slot2とslot0/1/3との差は1となる。そのため、利用数のバランスは崩れないと判定され、FPUが優先順位高として登録される。同様にFXUも優先順位高として登録される。同様にFXUも優先順位高として登録される。[8]の優先順位高命令種別のソートでは、ユニット利用数の最少数を調べるが、FPUが1で、FXUが0となるので、FXU,FPUの順で並ぶ、[9]-[14]では、優先順の高いFXU命令(add r3, r4, r5)が選択され、スケジュール表に配置される。上記の手順を繰り返し、4命令の配置が終了した状態が図5(4)となる。

次のグループでは、再び slot0 に命令を配置するが、FPU の命令を配置した場合、slot0 の利用数が 2 となり、slot1/2/3 との差が最大 2(slot2/3 の利用数が 0 のため)となるため、利用数のバランスが崩れると判定され FPU は優先順位低として登録され、FXU だけが優先順位高として登録される。そのため、slot0 には FXU 命令(add r6, r7, r8)がスケジュールされる。

図5 実行資源利用数遷移図

この処理の結果、図3コード(c)の命令列を作成することができる。ここで、8命令の配置を終えた時点(図5(8))でユニット・スロットの各資源の利用数の差が0となり、初期状態と同じになるため、これ以降の繰り返しでも同様の命令並びが得られることとなる。

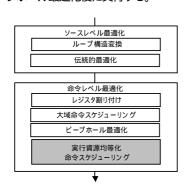

#### 3.2 コンパイラの構成

以上の実験結果を元に実行資源均等化命令スケジューリングを SR11000 用のコンパイラ 455に実装した。コンパイラ最適化部の構成を図6 に示す。実行資源均等化命令スケジューリングでは、基本ブロック内の命令を 1~5 命令の単位でグループ化していくため、本スケジューリング適用後に命令の増減があると、スケジューリング時に想定したグループと実際に実行されるグループとの間に違いが発生する。そのため、命令スケジューリングを適用する位置は、命令レベルの最適化がすべて終了したところで行うものとする。具体的には、図6 に示すようにレジスタ割り付け、大域命令スケジューリングやピープホール最適化後に実行する。

図6 コンパイラ最適化部の構成

次に、本最適化の適用範囲について説明する。今回対象とした POWER5 プロセッサでは、分岐命令で必ずグループが切れるため、分岐命令の飛び先である基本ブロック(途中で分岐や飛び込みのない命令列)の先頭をグループ化の基準点にする。また、適用対象とする基本ブロックは最内側ループに属するものだけとした。ループ本体は複数の基本ブロックから構成されることもあり、その場合は各基本ブロックごとに本最適化を適用する。

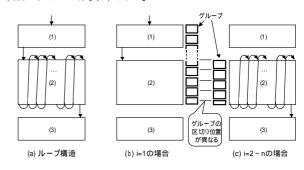

グループ化の基準点を最内側ループの基本ブロックの先頭とすることの妥当性について図7を用いて説明する。通常のループ構造を示したものを図7(a)に示す。ループは、ループプリヘッダ(1)、ループ本体(2)、ループ出口(3)と呼ばれる基本ブロックから構成され、命令はこの順に配置される。ループプリヘッダブロックの最後には分岐命令が存在しないため、ループプリヘッダブロックの命令数によっては、ループ本体の命令と結合されたグループが形成される場合がある(図7(b))。しかし、2回目以降の繰り返しでは図7(c)のように、ループ本体の最後の命令が分岐命令であるため、必ず

ループ本体の先頭からグループが形成される。つまり、ループの最初の1回だけは、グループ形成が想定したものと異なる可能性があるが、2回目以降は最内側ループの基本ブロックの先頭がグループの切れ目となり、ここをグループ化の基準点とすることが妥当である。

図7 ループ構造とグループ区切りについて

#### 4. 評価

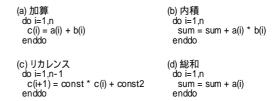

本報告で述べた実行資源均等化命令スケジューリングの 効果を実数型基本演算を対象に評価した。図8に測定に用い たプログラムの一部を示す。

図8 測定プログラムの一部

測定プログラムは図8の4種類加算、内積、リカレンス、総和で、それぞれn回繰り返すループ構造になっており、さらにこのループをm回呼び出して性能測定を行った。なお、測定はSR11000モデルJ1上で実施した。

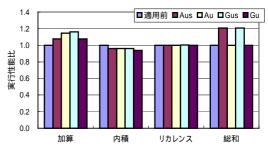

図9が図8の4種類のプログラムに本最適化を適用し、スケジューリング対象ループを16並列で実行した場合の測定結果である。グラフでは、本最適化適用前の実行性能を1とした場合の、適用後の実行性能の相対比を示している。測定は図4[5]で配置可能命令を基本プロック内の全命令から探すパターン(A)と、グループ間の命令移動が生じない範囲から探すパターン(G)の2種類と、図4[7]の優先順位決定時の実行資源としてユニットとスロットの両方を調べるパターン(us)と、ユニットのみを調べるパターン(u)の2種類の組み合わせで合計4種類について実施した。

さらに、表2に本最適化適用前後での最内側ループにおけるそれぞれの実行資源利用数を示す。なお、今回は実行資源均等化命令スケジューリングの評価を行うのが目的であるため、本来はユニット・スロットの利用バランスが改善された場合だけスケジューリング結果を採用するのだが、改善さ

れなかった場合もスケジューリング結果を採用するようようにした。

図 9 の結果より、配置可能命令を同一グループ内で探し、 かつ、優先順位決定時の実行資源としてユニットとスロット の両方を調べるパターン(Gus)において、総和計算で約21%、 加算計算で約16%の性能向上が見られる。総和については表 2 より、LSU/FPU 共にユニットの利用バランスは変わらな いが、スロットの利用バランスが改善されていることが分か る。 具体的にはスケジューリング適用前は、LSU でスロット 0,1 だけしか利用していなかったが、スケジューリング適用 後はスロット 0,1,2,3 すべてを均等に利用するコードになっ ている。また、FPU も同様のことが言える。2.2 の予備調査 ではスロット均等化の効果は見られなかったが、総和につい ては均等化の効果が見られた。加算についても表 2 より、 LSU/FPU のユニット利用バランスが改善されていることが 分かる。逆に内積では約5%の性能劣化が見られる。これは、 スケジューリング適用前は LSU のユニット利用バランスが 均等であったが、スケジューリング適用後にユニット利用バ ランスが崩れたためと考えられる。但し、先程も述べたとお り、我々のコンパイラでは、ユニットやスロットの利用バラ ンスが崩れた場合は、スケジューリング結果を破棄して元の コードをそのまま出力するため、実際のところ性能劣化は発 生しない。

これらの結果から、SR11000 モデルJ1 上で、実行資源を 均等化する命令スケジューリングが有効であることが示さ れた。

#### 5. 関連研究

文献 6)では、命令間に存在するレイテンシを無視し、1 サイクルに利用可能な実行資源に注目したスケジューリング方式を提案している。この方式では、実行資源のうち各命令種別で1 サイクルに完了可能な命令数に注目し、各サイクルに配置する命令を決定している。そして、このスケジューリング方式が Out-of-order 機構を持つプロセッサ(PA-8000)に対し、有効であることを示している。

# 6. まとめ

本稿では、SR11000 モデル J1 に搭載している POWER5 向けに実行資源均等化命令スケジューリング手法の説明と効果を評価した。POWER5 では、複数の命令をグループという単位で管理し、グループ単位で命令の発行・完了を行っている。さらに、グループ内の命令位置により、利用する実行資源が予め決められているため、実行資源の利用バランスによって実行性能に影響が出ることが示された。そこで、本稿で説明した命令スケジューリングを実数型の基本演算プログラムに適用することで、総和演算と加算演算で実行資源の利用バランスが改善し、実行性能がそれぞれ約 21%、約16%向上することが示された。

図9 実行性能比(16並列実行)

表 2 実行資源利用数

| LSU       | ユニット(0/1)<br>スロット(0/1/2/3)                  |                                                    |                                                   |                                                   |                                              |  |  |  |  |  |  |

|-----------|---------------------------------------------|----------------------------------------------------|---------------------------------------------------|---------------------------------------------------|----------------------------------------------|--|--|--|--|--|--|

| LSU       | 適用前                                         | Aus                                                | Аu                                                | Gus                                               | Gu                                           |  |  |  |  |  |  |

| 加算        | 11/13                                       | 13/11                                              | 12/12                                             | 12/12                                             | 11/13                                        |  |  |  |  |  |  |

| 川昇        | 6/7/6/5                                     | 8/6/5/5                                            | 8/8/4/4                                           | 6/6/6/6                                           | 3/6/7/8                                      |  |  |  |  |  |  |

| 内積        | 20/20                                       | 19/21                                              | 19/21                                             | 21/19                                             | 20/20                                        |  |  |  |  |  |  |

| PY作员      | 10/10/10/10                                 | 10/11/10/9                                         | 11/12/9/8                                         | 10/10/9/11                                        | 5/7/13/15                                    |  |  |  |  |  |  |

| リカレンス     | 11/11                                       | 11/11                                              | 11/11                                             | 11/11                                             | 11/11                                        |  |  |  |  |  |  |

| 373 D 3 X | 6/5/6/5                                     | 5/5/6/6                                            | 5/5/6/6                                           | 6/5/6/5                                           | 7/6/5/4                                      |  |  |  |  |  |  |

| 総和        | 10/10                                       | 10/10                                              | 10/10                                             | 10/10                                             | 10/10                                        |  |  |  |  |  |  |

| WO.LH     | 10/10/0/0                                   | 6/6/4/4                                            | 10/10/0/0                                         | 5/5/5/5                                           | 10/10/0/0                                    |  |  |  |  |  |  |

|           | ユニット(0/1)                                   |                                                    |                                                   |                                                   |                                              |  |  |  |  |  |  |

| EDII      |                                             |                                                    |                                                   | 3/                                                |                                              |  |  |  |  |  |  |

| FPU       | 適用前                                         |                                                    | (ロット(0/1/2/                                       |                                                   | Gu                                           |  |  |  |  |  |  |

|           | 適用前                                         | Aus<br>7/9                                         |                                                   | Gus                                               | Gu<br>8/8                                    |  |  |  |  |  |  |

| FPU<br>加算 |                                             | Aus                                                | 、ロット(0/1/2/:<br>Au                                |                                                   | Gu<br>8/8<br>6/4/4/2                         |  |  |  |  |  |  |

| 加算        | 5/11                                        | Aus<br>7/9                                         | ロット(0/1/2/<br>Au<br>7/9                           | Gus<br>8/8                                        | 8/8                                          |  |  |  |  |  |  |

|           | 5/11<br>3/5/6/2                             | Aus<br>7/9<br>5/5/4/2                              | (ロット(0/1/2/<br>Au<br>7/9<br>4/4/5/3               | Gus<br>8/8<br>5/4/4/3                             | 8/8<br>6/4/4/2                               |  |  |  |  |  |  |

| 加算 内積     | 5/11<br>3/5/6/2<br>9/11                     | Aus<br>7/9<br>5/5/4/2<br>10/10                     | Au<br>7/9<br>4/4/5/3<br>10/10                     | Gus<br>8/8<br>5/4/4/3<br>9/11                     | 8/8<br>6/4/4/2<br>10/10                      |  |  |  |  |  |  |

| 加算        | 5/11<br>3/5/6/2<br>9/11<br>5/6/5/4          | Aus<br>7/9<br>5/5/4/2<br>10/10<br>5/5/5/5          | Au<br>7/9<br>4/4/5/3<br>10/10<br>4/4/6/6          | Gus<br>8/8<br>5/4/4/3<br>9/11<br>5/6/5/4          | 8/8<br>6/4/4/2<br>10/10<br>10/9/1/0          |  |  |  |  |  |  |

| 加算 内積     | 5/11<br>3/5/6/2<br>9/11<br>5/6/5/4<br>19/21 | Aus<br>7/9<br>5/5/4/2<br>10/10<br>5/5/5/5<br>20/20 | Au<br>7/9<br>4/4/5/3<br>10/10<br>4/4/6/6<br>20/20 | Gus<br>8/8<br>5/4/4/3<br>9/11<br>5/6/5/4<br>19/21 | 8/8<br>6/4/4/2<br>10/10<br>10/9/1/0<br>19/21 |  |  |  |  |  |  |

### 7. 参考文献

- "The POWER4 Processor Introduction and Tuning Guide", IBM RedBooks(2001), http://www.redbooks.ibm.com/redbooks/pdfs/sg24704

1.pdf

- Advanced POWER Virtualization on IBM eServer p5 Servers Architecture and Performance Considerations", IBM RedBooks Draft(2004).

- Gang Chen, Michael D.Smith: "Reorganizing Global Schedules for Register Allocation", ICS-99, pp.408-416, 1999.

- 4) 青木秀貴, 處雅尋, 本川敬子, 五百木伸洋, 石原 修: "SR11000 モデルH1 のソフトウェアプリフェッチ手法"、電子情報通信学会 2004 年総合大会、D-6-11、2004。

- 5) 本川敬子、伊藤信一、橋本博幸、久島伊知郎: "SR11000 コンパイラにおけるデータキャッシュ向け最適化"、FIT2004、C-028、2004。

- David A Dunn and Wei-Chung Hsu: "Instruction Scheduling for the HP PA-8000", Micro-29, pp.298-307, 1996.