# Partial MaxSAT を用いた低消費電力指向ドントケア割当て法

三澤健一郎<sup>†1</sup> 平間勇貴<sup>†2</sup> 細川利典<sup>†2</sup> 山崎紘史<sup>†2</sup> 吉村正義<sup>†3</sup> 新井雅之<sup>†2</sup>

実速度スキャンテストにおいてテストベクトルの応答がフリップフロップ(Flip-Flop:FF)に格納されると、キャプチャ動作時に発生するスイッチング動作(0から 1 または 1 から 0 への値の遷移)が大きくなるため、キャプチャ時消費電力が大きくなり、過度な電圧降下(1R ドロップ)が発生する。過度な電圧降下(1R ドロップ)は信号遅延を増大させ、タイミング遅延を伴う欠陥を発生させる可能性があるため、大きなキャプチャ時消費電力が発生する実速度スキャンテストは不要な歩留まり損失を引き起こす。キャプチャ時消費電力を削減する方法として、低消費電力指向のドントケア(1X)判定と 1X 割当て手法が有効であることが知られている。従来の低消費電力指向 1X 割当て手法は、テストキューブ内の 1X ビットに論理値を割当て、テスト時の 1F の遷移数を削減している。しかしながら、従来手法では、テスト時の内部信号線の遷移数の削減は考慮していない。本論文では、1Partial MaxSAT ソルバーを用いて、できるだけ多くの内部信号線の遷移数を削減する低消費電力指向 1X 割当て手法を提案する。実験結果は、提案した手法が従来手法と比較して、テスト集合内のキャプチャセーフテストベクトル数とアンセーフ故障数を削減したことを示す。

# A Low Capture Power Oriented X-filling Method Based on Iterative Partial MaxSAT Application

KENICHIRO MISAWA<sup>†1</sup> YUKI HIRAMA<sup>†2</sup> TOSHINORI HOSOKAWA<sup>†2</sup> HIROSHI YAMAZAKI<sup>†2</sup> MASAYOSHI YOSHIMURA<sup>†3</sup> MASAYUKI ARAI<sup>†2</sup>

High power dissipation can occur by high launch-induced switching activity when the response to a test vector is captured by flip-flops(FFs) in at-speed scan testing resulting in excessive IR drop. Since excessive IR-drop significantly increases extra signal delay, and thus might result in timing errors, such testing induces unnecessary yield loss in the deep sub-micron era. It is known that test modification methods using X-identification and X-filling are effective to reduce power dissipation in the capture cycle. Conventional low capture power oriented X-filling methods assign logic values to unspecified bits in test cubes to reduce the number of transitions on FFs. However, our goal is to reduce the number of transitions on internal signal lines. In this paper, we propose a low capture power oriented X-filling method iteratively using a Partial MaxSAT Solver in order to reduce the number of transitions on as many internal signal lines as possible. Experimental results show that our proposed method reduced the numbers of capture-unsafe test vectors and unsafe faults compared with conventional methods.

## 1. はじめに

超大規模集積回路(Very Large Scale Integrated circuits: VLSI)は、回路の高集積、高速化、電源電圧の低下に伴い、微小遅延[1]などのタイミング遅延を伴う欠陥の影響を受ける. Launch-on-capture(LOC)方式[2]における実速度スキャンテストは、高いテスト容易性、高い故障検出率、強力な診断サポート[3]などの点から、タイミング遅延を伴う欠陥を検出するために幅広く使用されている。しかしながら、回路の内部信号線の遷移による過度なキャプチャ時消費電力によって、過度な電圧降下(IR ドロップ)[4]を引き起こす可能性がある。過度な電圧降下は、信号遅延を増加させ、タイミング遅延を伴う欠陥を発生させる可能性があるため、過度なキャプチャ時消費電力が発生するテストは不要な歩留まり損失を引き起こす[5].

LOC 方式における実速度スキャンテストでは、キャプチャ動作時の信号線の遷移数(launch switching activity: LSA)を削減することが非常に重要である。キャプチャ時消費電力削減のための手法は多数提案されており、それらの手法は、回路構造変更による手法[6-9]、テストデータ変更による手法[10-18]に分類される。回路構造変更による手法は、テスト対象回路(circuit under test: CUT)にテスト容易化のためのテスト専用回路を付加する。テストデータ変更による

†1 日本大学大学院 生産工学研究科

Graduate School of Industrial Technology, Nihon University

†2 日本大学 生産工学部

College of Industrial Technology, Nihon University

†3 京都産業大学 情報理工学部

Faculty of Information Science and Engineering, Kyoto Sangyo University

手法は、回路構造を変更せず、テストデータを変更することで、キャプチャ時消費電力を削減する. 本論文では、テストデータ変更を用いて LSA 削減を試みる.

テストデータ変更による手法[10-18]は、X 判定[18]と X 割当て[10-17]から構成される. X 判定は、故障検出率を損失させることなく、初期テストベクトルの故障検出に必要ないビットをXビットに割当てる. よって、テスト集合は、X ビットを含むテストキューブの集合に変更される. X 割当ては、テストキューブの X ビットに論理値(0 または 1)を割当てる. LSA 削減のための X 割当て手法として、J-Fill[16]、P-Fill[11]、JP-Fill[12]、SAT-Fill[17]などの多くの手法が提案されている. これらの従来手法は、フリップフロップ(Flip-flop:FF)の信号線の遷移数を削減することにより、キャプチャ時消費電力を削減している. しかしながら、LSA 削減は、キャプチャ動作時の回路の内部信号線の遷移数を削減することが重要である.

初期テスト集合は、キャプチャ時消費電力の閾値により、キャプチャセーフテストベクトル[10]とキャプチャアンセーフテストベクトル[10]に分類される。キャプチャ時消費電力の閾値を超えるキャプチャアンセーフテストベクトルは、実速度スキャンテストに使用困難であるため、キャプチャアンセーフテストベクトルでのみ検出されるアンセーフ故障[10]の検出は保証されない。よって、実速度スキャンテストの故障検出率を向上させるためには、アンセーフ故障数の削減が重要である。しかしながら、文献[11-17]では、平均 WSA[19]と最大 WSA の削減率のみについて言及している。

近年,充足可能性問題(satisfiability problem: SAT)がテス

ト生成の分野で用いられている[20]. 最大充足可能性問題 (maximum satisfiability problem: MaxSAT)[21]は、SAT を最適化問題に拡張したものある. MaxSAT は、与えられた命題論理式に対して、最大数の節が真となる論理変数の割当てを考える. MaxSAT を拡張した最適化問題が Partial MaxSAT である. Partial MaxSAT は、命題論理式の節がハード節とソフト節に分類され、全てのハード節と最大数のソフト節が真となる論理変数の割当てを考える.

本論文では、Partial MaxSAT を用いた低消費電力指向 X 割当て法を提案する.提案手法は、Partial MaxSAT を用いて回路の内部信号線の遷移数を削減する X 割当てを行う.また、問題を解くための制限時間を増加させながら Partial MaxSAT を繰り返し用いて、初期テスト集合からキャプチャアンセーフテストベクトル数[10]とアンセーフ故障数[10]を削減する.

本論文は以下の通りに構成される。第2章は、キャプチャ時消費電力問題について説明する。第3章は、Partial MaxSAT について説明する。第4章は、提案手法であるPartial MaxSAT を用いた低消費電力指向X割当て法について説明する。第5章は、実験結果について示し、第6章は、本論文のまとめと今後の課題について述べる。

### 2. キャプチャ時消費電力問題

本論文では、消費電力解析において、消費電力の見積もり 手法として広く用いられている重み付き信号線遷移 (Weighted Switching Activity: WSA) [19]を用いる. WSA は、電源電圧、動作周波数、負荷容量などを考慮した厳密 な消費電力計算を行わず、回路内の各ゲートの出力信号線 の遷移数から消費電力の見積もり値を算出する. 式(2.1)に WSA の算出式を示す.

$$WSA(v_j) = \sum_{i=1}^{G} tran(g_i) \times (1 + fanout(g_i)) \quad (2.1)$$

式(2.1)において、 $v_j$ はテストベクトル、Gは回路内に含まれる総ゲート数である。ゲート $g_i$ で遷移が発生する場合、 $tran(g_i)$ は 1 を返す。ゲート $g_i$ で遷移が発生しない場合、 $tran(g_i)$ は 0 を返す。 $fanout(g_i)$ はゲート $g_i$ の分岐信号線数を返す。1 は遷移が発生したゲートの重み付けのために足し込まれる。1 つのテストベクトルに対する回路全体のWSA 値は、回路内の各ゲートの WSA 値の合計として算出される。

実速度スキャンテストにおいて、キャプチャ時消費電力の閾値を超えるキャプチャアンセーフテストベクトルの使用は、誤テストと不要な歩留まり損失を引き起こす可能性が高くなることが考えられる.よって、キャプチャアンセーフテストベクトルは、実速度スキャンテストで使用困難である.したがって、テスト集合のキャプチャセーフテストベクトルで検出されるセーフ故障数を最大にすること、アンセーフ故障数を最小にすることが重要である.

#### 3. Partial MaxSAT

Partial MaxSAT では、与えられた論理和標準形 (Conjunctive Normal Form: CNF) の命題論理式に対して、最大数のソフト節が真となるように命題論理式の各節に含まれる論理変数の真または偽の割当てを考える。命題論理式は、各論理

| a | b | с | SAT/UNSAT | 重み |

|---|---|---|-----------|----|

| 0 | 0 | 0 | SAT       | 10 |

| 0 | 0 | 1 | UNSAT     | -  |

| 0 | 1 | 0 | SAT       | 5  |

| 0 | 1 | 1 | UNSAT     | -  |

| 1 | 0 | 0 | SAT       | 5  |

| 1 | 0 | 1 | UNSAT     | -  |

| 1 | 1 | 0 | UNSAT     | -  |

| 1 | 1 | 1 | SAT       | 10 |

$(a \vee \neg c, \ \varnothing) \cdot (b \vee \neg c, \ \varnothing) \cdot (\neg a \vee \neg b \vee c, \ \varnothing) \cdot (\neg a \vee c, \ 5) \cdot (\neg b \vee c, \ 5)$

#### 図 1. 重み付き Partial MaxSAT の例

積または単項である節で構成され、各節には重みが設定される.無限大の重みが設定される節をハード節、任意の重みが設定される節をソフト節と呼ぶ.また、命題論理式の各ソフト節に設定される重みが異なる場合、重み付けPartial MaxSATでは、真となるソフト節の重みの総和を最大化するように命題論理式の各節に含まれる論理変数に真または偽の割当てを考える.したがって、全てのハード節が真になり、重みを最大化するために適切なソフト節が真になる必要がある.命題論理式の全てのハード節が真となる論理変数の割当てが存在する場合、充足可能(Satisfiability: SAT)と呼ぶ.命題論理式の全てのハード節が真となる論理変数への割当てが存在しない場合、充足不能(Unsatisfiability: UNSAT)と呼ぶ.

図1に重み付き Partial MaxSAT の例を示す。図1において、命題論理式のハード節は、2 入力 AND ゲートの動作を表す。命題論理式のソフト節は、信号線 a と b の論理値が c と同じ論理値になるような条件を表す。図1 の場合、(a,b,c)=(0,0,0),(0,1,0),(1,0,0),(1,1,1)の4 通りの割当てが解となる。また、(a,b,c)=(0,0,0),(1,1,1)の2 通りの割当ては、真のソフト節の重みの合計が10 であり、真のソフト節の重みの合計が最大となるため、最適解となる。

#### 4. 提案手法

本章では、提案手法である Partial MaxSAT を用いた低消費電力指向 X 割当て法について説明する.

#### 4.1 X 割当ての定式化

本節では、X割当ての定式化について説明する. 提案手法の低消費電力指向 X割当て法は,以下の最適化問題として定式化される.

入力:回路,初期テスト集合,WSA 閾値

出力: X割当て後テスト集合,アンセーフ故障集合

制約: X 割当ての試行回数

最適化: X 割当て後テスト集合におけるアンセーフ故障数の最小化

#### 4.2 低消費電力指向 X 割当てのアルゴリズム

本節では、Partial MaxSAT を用いた低消費電力指向 X 割当てのアルゴリズムについて説明する.

本提案手法では、テストキューブ集合を入力として、Partial MaxSAT を用いて低消費電力指向 X 割当てを行い、低消費電力化されたテスト集合を生成する。図 2 に提案手法アルゴリズムを示す。入力は、回路C、初期テストキューブ集合T、試行回数iである。出力はi回目の X 割当て後

```

1. Input: Circuit C, Initial test cube set T, and i-thiteration i

2. Output: i - th test vector set T_i

3. Low_power_X - fill_patial_MaxSAT(C, T, i){

4.

T_i = \varphi;

5.

\Phi_{C} = Generate \ CNF \ from \ C;

6.

for(j = 0; j < |T|; j + +){

7.

\left(\Phi_{const_{j}},\Phi_{tran_{j}}\right) = Logjcsim(C,t_{j});

\dot{\boldsymbol{\Phi}} = \boldsymbol{\Phi}_{\mathcal{C}} \cdot \boldsymbol{\Phi}_{const_i} \cdot \boldsymbol{\Phi}_{tran_i};

8.

9.

t_i = Partial\_MaxSAT(\Phi);

10.

T_i = T_i \cup t_i;

11.

12.

return(T_i);

13. }

```

#### 図 2. 提案手法アルゴリズム

のテスト集合 $T_i$ である. [i] は、何回目の X 割当てを行っ ているかを表す. まず, X割当て後のテストベクトルを格 納するテスト集合 $T_i$ を空に初期化する(行 4). 次に, Cに対 して、Cの各ゲートの動作を表す命題論理式を生成し、 $\Phi_C$ に 格納する(行 5). Tに含まれるテストキューブ $t_i$ に対して, 行7から行10までの処理を実行する(行6). Cに対して,  $t_i$ で 論理シミュレーションを実行する. 論理シミュレーション 後,信号線値がある論理値(0または1)に決定されている信 号線に対して, その論理値を有するための節が生成され,  $\Phi_{const,}$ に格納される.また,信号線値がXである信号線は, X割当てによって、立上り遷移または立下り遷移が発生す る可能性がある.よって, X の信号線に対して, 信号線の 遷移を抑制するための節が生成され、 $\Phi_{tran_i}$ に格納される (行 7).  $\Phi_C$ ,  $\Phi_{const_i}$ ,  $\Phi_{tran_i} \delta t_i$ の命題論理式として,  $\Phi$ に 格納する(行 8). Partial MaxSAT に $\Phi$ を与え,  $t_i$ の X 割当て を行う(行 9).  $t_i$ を $T_i$ に格納する(行 10).  $T_i$ を返し, アルゴ リズムを終了する(行 12).

# 4.3 ハード節

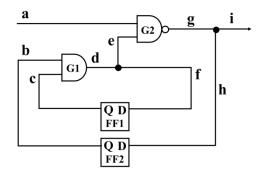

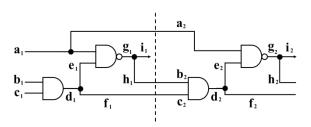

本節では、提案手法で生成されるハード節について説明する。図 3 にフルスキャン設計済み順序回路を示す。図 3 において、FF1 と FF2 はスキャン FF、G0 は AND ゲート、G1 は NAND ゲート、a は外部入力,i は外部出力,b からh は信号線である。また、図 4 に LOC 方式の X 割当てモデルを示す。図 4 において、信号線の添え字は時刻を示す。また、テストキューブまたはテストベクトルは $a_1$ 、 $b_1$ 、 $c_1$ に印加され、テスト応答は $f_2$ 、 $h_2$ で観測される。本提案手法の命題論理式 $\Phi_c$ は、X 割当てモデル内の各ゲートの動作を表すための節で構成される。

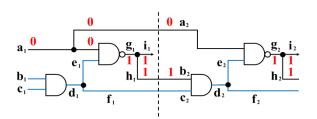

図 5 にテストキューブ $t_j$ =( $a_1$ ,  $b_1$ , c)=(0, X, X)を X割当てモデルに印加した際の論理シミュレーションの結果を示す。図 5 において, $a_1$ ,  $a_2$ は 0,  $g_1$ ,  $h_1$ ,  $i_1$ ,  $b_2$ ,  $g_2$ ,  $h_2$ ,  $i_2$ は 1 である。本提案手法の命題論理式 $\Phi_{const_j}$ は,論理値が決定されている信号線が対応する論理値を有するための節で構成される。式(4.1)に,図 5 における命題論理式 $\Phi_{const_j}$ を示す。

$$\begin{split} \Phi_{const_{j}} &= \begin{pmatrix} \neg a_{1}, & \infty \end{pmatrix} \cdot \begin{pmatrix} \neg a_{2}, & \infty \end{pmatrix} \cdot \begin{pmatrix} g_{1}, & \infty \end{pmatrix} \cdot \\ \begin{pmatrix} h_{1}, & \infty \end{pmatrix} \cdot \begin{pmatrix} i_{1}, & \infty \end{pmatrix} \cdot \begin{pmatrix} b_{2}, & \infty \end{pmatrix} \cdot \\ \begin{pmatrix} g_{2}, & \infty \end{pmatrix} \cdot \begin{pmatrix} h_{2}, & \infty \end{pmatrix} \cdot \begin{pmatrix} i_{2}, & \infty \end{pmatrix} \end{split} \tag{4.1}$$

$\Phi_{c}$ および $\Phi_{const_{j}}$ の全ての節は、ハード節であり、重みは無限大に設定される.

図3. スキャン設計済み順序回路

図 4. X 割当てモデル

図 5. 論理シミュレーションの結果

#### 4.4 ソフト節

本節では、提案手法で生成されるソフト節について説明する. 提案手法では、信号線の遷移を抑制するためにソフト節が生成される. 論理シミュレーション後、ある信号線sの1時刻目論理値または2時刻目論理値がXであるの場合、X割当てによって立上り遷移または立下り遷移が発生する可能性がある. よって、信号線sに対して、遷移を抑制するソフト節を生成する必要がある. 信号線sの論理値によって以下の5種類のソフト節からいずれかのソフト節が生成される. ここで、もし信号線sの1時刻目論理値がX、信号線sの2時刻目論理値が0であった場合、2時刻分の論理値を(X, 0)と表す.

#### (1) (X, 0)

信号線 s が(X, 0)の場合, X 割当てによって, 信号線 s の立下り遷移が発生する可能性があるため, 以下のソフト節を生成し, 信号線 s の立下り遷移を抑制する.

$$(\neg s_1, 1)$$

#### (2) (X, 1)

信号線 s が(X, 1)の場合, X 割当てによって, 信号線 s の立上り遷移が発生する可能性があるため, 以下のソフト節を生成し, 信号線 s の立上り遷移を抑制する.

$$(s_1, 1)$$

#### (3) (0, X)

信号線 s が(0, X)の場合, X 割当てによって, 信号線 s の立上り遷移が発生する可能性があるため, 以下のソフト節を生成し, 信号線 s の立上り遷移を抑制する.

$$(\neg s_2, 1)$$

#### (4) (1, X)

信号線 s が(1, X)の場合, X 割当てによって, 信号線 s の立下り遷移が発生する可能性があるため, 以下のソフト節を生成し, 信号線 s の立下り遷移を抑制する.

$$(s_2, 1)$$

#### (5) (X, X)

信号線 s が(X, X)の場合, X 割当てによって, 信号線 s の立上り遷移または立下り遷移が発生する可能性があるため, 以下のソフト節を生成し, 信号線 s の立上り遷移と立下り遷移を抑制する.

$$(s_1 \lor \neg s_2, 1) \cdot (\neg s_1 \lor s_2, 1)$$

図 5 の場合,信号線 $b_1$ ,  $c_1$ ,  $d_1$ ,  $e_1$ ,  $f_1$ ,  $c_2$ ,  $d_2$ ,  $e_2$ ,  $f_2$ は, X割当 てによって立上り遷移または立下り遷移が発生する可能性がある. b=(X, 1)なので、立上り遷移が発生する可能性がある. また、c=(X, X)、d=(X, X)、e=(X, X)、f=(X, X)なので、立上り遷移または立下り遷移が発生する可能性がある. 命題論理式 $\Phi_{tran_j}$ は、D0 は、D1 における $\Phi_{tran_j}$ を示す。

$$\begin{split} \Phi_{tran_{j}} &= \begin{pmatrix} b_{1}, & 1 \end{pmatrix} \cdot \begin{pmatrix} c_{1} \vee \neg c_{2}, & 1 \end{pmatrix} \cdot \begin{pmatrix} \neg c_{1} \vee c_{2}, & 1 \end{pmatrix} \cdot \\ & \begin{pmatrix} d_{1} \vee \neg d_{2}, & 1 \end{pmatrix} \cdot \begin{pmatrix} \neg d_{1} \vee d_{2}, & 1 \end{pmatrix} \cdot \\ & \begin{pmatrix} e_{1} \vee \neg e_{2}, & 1 \end{pmatrix} \cdot \begin{pmatrix} \neg e_{1} \vee e_{2}, & 1 \end{pmatrix} \cdot \\ & \begin{pmatrix} f_{1} \vee \neg f_{2}, & 1 \end{pmatrix} \cdot \begin{pmatrix} \neg f_{1} \vee f_{2}, & 1 \end{pmatrix} \end{split} \tag{4.2}$$

# 4.5 低消費電力指向 X 割当ての全体アルゴリズム

本章では、提案手法の全体アルゴリズムについて説明す る. 本提案手法では、問題を解くための制限時間を増加さ せながら Partial MaxSAT を用いた低消費電力指向 X 割当て を繰り返し行うことで、最終的な低消費電力化されたテス ト集合を生成する. 図6に全体アルゴリズムを示す. 入力 は、回路C、初期テストキューブ集合T、WSA 閾値 $W_{th}$ 、試 行回数Nである. 出力は、最終テスト集合 $T_{fin}$ 、アンセーフ 故障集合USFである. まず、 $T_{fin}$ を空に初期化する(行 4). 何回目のX割当てかを表す変数iを1で初期化する(行 5). iがN以下である場合,行7から行14の処理が実行される(行 6). Tに対して、Partial MaxSAT を用いた低消費電力指向 X 割当てが実行されi回目のX割当て後、テスト集合 $T_i$ が生成 される(行 7).  $T_i$ の WSA 計算を行い、 $W_{th}$ を用いて、 $T_i$ をキ ャプチャセーフテスト集合 $T_{safe_i}$ とキャプチャアンセーフ テスト集合 $T_{unsafe_i}$ に分類する(行 8).  $T_{unsafe_i}$ が空またはiと Nが等しい場合(行 9)、 $T_{fin}$ に $T_{fin}$ と $T_{safe_i}$ の和集合が格納さ れ(行 10),行 17 へ進む(行 11). $T_{fin}$ に $T_{fin}$ と $T_{safe_i}$ の和集合 が格納される(行 13). Tから $T_{safe_i}$ を削除する(行 14). iを 1 増加させる(行 15).  $T_{fin}$ と $T_{unsafe_i}$ を用いて故障シミュレー ションを実行し、USFを生成する(行 17). ここで、 $T_{fin}$ はキ ャプチャセーフテスト集合であり、USFは $T_{unsafe_i}$ でのみ検 出されたアンセーフ故障集合である.  $T_{fin}$ に $T_{fin}$ と $T_{unsafe_i}$ の和集合が格納される(行 18).  $T_{fin}$ とUSFを返しアルゴリズ ムを終了する(行19).

```

1. Input: Circuit C, Initial test cube set T, Treshold value of WSA W_{th}

and #iteration N

3. Output: Final test set Tfin, Unsafe fault set USF

4. Low_power_X - fill_patial_MaxSAT_IT(C, T, W_{th}, N)

T_{fin} = \varphi;

while(i \leq N){

6.

7.

T_i = Low\_power\_X - fill Partial MaxSAT(C,T,i);

8.

(Tsafe_i, Tunsafe_i) = Calc_WSA(C, T_i, W_{th});

9.

Lif((Tunsafe_i == \varphi)||(i == N)\{

10.

T_{fin} = T_{fin} \cup Tsafe_i;

11.

break:

12.

13.

T_{fin} = T_{fin} \cup Tsafe_i;

14.

T = T - Tsafe_i;

15.

i++;

16.

}

17.

USF = Fault\_sim(C, T_{fin}, Tunsafe_i);

T_{fin} = T_{fin} \cup Tunsafe_i;

return(T_{fin}, USF);

20.}

```

図 6. 提案手法全体アルゴリズム

#### 5. 実験結果

本章では,提案手法である Partial MaxSAT を用いた低消 費電力指向 X 割当て法の実験結果について説明する. 提案 手法は、C 言語で実装された. 実験は、Core i7 4790 (3.6GHz) および8GBメモリのコンピュータを使用して、ISCAS'89 ベンチマーク回路と ITC'99 ベンチマーク回路を対象に行 った. 初期テスト集合は、自動テストパターン生成(Auto Test Pattern Generator: ATPG) ツールである Synopsys 社の TetraMax で生成された. キャプチャセーフテストベクトル とキャプチャアンセーフテストベクトルを分類するために 用いる WSA 閾値は、回路内の遷移が発生する可能性があ る全ての信号線で論理値の遷移が発生した場合の WSA 値 の 20%に設定した. Partial MaxSAT は, Dist[21]を用い, Intel Xeon (R) CPU E51660 v4 (3.2GHz×16) 32GB メモリのコ ンピュータで実行した. 提案手法のX割当ての試行回数は, 11 回に設定した. 1 つのテストキューブおける Partial MaxSAT の制約時間は, i 回目の試行 (1 $\leq$ i $\leq$ 11) に対して, それぞれ 0.1 秒, 1 秒, 2 秒, 3 秒, 4 秒, 5 秒, 6 秒, 7 秒, 8秒,9秒,10秒に設定した.

表 1 は、初期テスト集合の情報について示す。表 1 の場合,「Circuit」は回路名,「#FF」は FF 数,「#TV」は初期テスト集合のテストベクトル数,「FC」は故障検出率,「FE」は故障検出効率,「X-rate」は初期テスト集合の X ビットの割合を示す。

表 2 は、提案手法である Partial MaxSAT を用いた低消費電力指向 X 割当て法の最終的な実験結果を示す. 比較対象は、JP-FILL[12]である. 表 2 の場合、「Circuit」は回路名、「#TC」は初期テストキューブ集合のテストキューブ数、「JP-FILL」は JP-FILL の実験結果、「Proposed」は提案手法の実験結果、「#STV」は X 割当て後のキャプチャセーフテストベクトル数、「#UTV」は X 割当て後のキャプチャアンセーフテストベクトル数、「#USF」は X 割当て後のテスト集合で検出されるアンセーフ故障数、「Time」は X 割当ての実行時間を示す.

表 1. 初期テスト集合の情報

| Circuit | #FF  | #TV  | FC(%) | FE(%)  | X-rate(%) |

|---------|------|------|-------|--------|-----------|

| s5378   | 179  | 160  | 59.41 | 99.69  | 73.79     |

| s9234   | 228  | 319  | 75.47 | 99.55  | 73.16     |

| s13207  | 669  | 310  | 72.77 | 99.90  | 90.70     |

| s15850  | 597  | 199  | 63.93 | 94.25  | 83.17     |

| s35932  | 1728 | 62   | 70.23 | 100.00 | 75.38     |

| s38417  | 1636 | 238  | 96.32 | 99.91  | 77.00     |

| s38584  | 1453 | 412  | 63.68 | 99.63  | 86.15     |

| b14     | 245  | 1185 | 93.61 | 99.96  | 72.65     |

| b15     | 449  | 995  | 84.54 | 97.86  | 66.64     |

| b20     | 490  | 1399 | 92.78 | 99.98  | 66.64     |

| b21     | 490  | 1484 | 92.53 | 99.96  | 68.52     |

| b22     | 735  | 1513 | 92.39 | 99.93  | 72.24     |

提案手法は、JP-FILL と比較して、キャプチャセーフテストベクトル数を平均 52.14%増加させ、キャプチャアンセーフテストベクトル数を平均 54.56%減少させた結果となった。また、アンセーフ故障数を平均 59.41%削減させる結果となった。しかしながら、提案手法の X 割当ての実行時間は大幅に増加する結果となった。

表 3 は、問題を解くための制限時間を増加させながら Partial MaxSAT を用いた低消費電力指向 X 割当てを繰り返 し行った際の詳細な実験結果を示す.表3の場合、「Circuit」 は回路名、「i」は試行回数、「#TC」はX割当ての対象とな るテストキューブ数、「#STV」はX割当て後のキャプチャ セーフテストベクトル数、「#UTV」は X 割当て後のキャプ チャアンセーフテストベクトル数を示す. 提案手法は, JP-FILL と比較して、s38584 ベンチマーク回路を除くすべ てのベンチマーク回路において、Partial MaxSAT の制約時 間が1秒の時点でキャプチャセーフテストベクトス数を増 加させ、キャプチャアンセーフベクトル数を減少させる結 果となった. また, b14 ベンチマーク回路と b15 ベンチマ ーク回路において、提案手法の試行回数を増加させたとし ても、キャプチャアンセーフテストベクトル数を大幅に減 少させることができないと考えられる. また, b20 ベンチ マーク回路と b21 ベンチマーク回路と b22 ベンチマーク回 路において、提案手法の試行回数を増やした場合、キャプ チャアンセーフテストベクトル数を減少させることができ ると考えられる. また, 提案手法は, 試行回数および Partial MaxSAT の制約時間が適切に設定されている場合、キャプ チャアンセーフテストベクトルを減少させ,かつX割当て の実行時間を短縮することが可能であると考えられる.

#### 6. まとめ

本論文では、Partial MaxSAT を用いた低消費電力指向 X 割当てを提案した. 提案手法は、Partial MaxSAT を用いて、テストキューブの X ビットに信号線の遷移を削減させるための論理値を割当てる. また、提案手法は、Partial MaxSAT を繰り返し用いて、テスト集合のキャプチャアンセーフテストベクトルを減少させることができた. 実験結果では、JP-FILL と比較して、キャプチャアンセーフ故障数を平均59.41%、最大 92.13%削減することができた.

#### 参考文献

[1] Y. Sato, S. Hamada, T. Maeda, A. Takatori, Y. Nozuyama and S. Kajihara, "Invisible Delay Quality - SDQM Model Lights Up What Could Not Be Seen," Proc. ITC, Paper 47.1, 2005.

表 2. 提案手法の実験結果

| Circuit | #TC  |      | JP-  | FILL  |         | Proposed |      |       |         |  |

|---------|------|------|------|-------|---------|----------|------|-------|---------|--|

| Circuit |      | #STV | #UTV | #USF  | Time(s) | #STV     | #UTV | #USF  | Time(s) |  |

| s5378   | 160  | 130  | 30   | 545   | 2.1     | 142      | 18   | 316   | 1068.0  |  |

| s9234   | 319  | 187  | 132  | 3831  | 5.5     | 226      | 93   | 2574  | 5279.9  |  |

| s13207  | 310  | 302  | 8    | 261   | 76.0    | 309      | 1    | 43    | 378.0   |  |

| s15850  | 199  | 193  | 6    | 254   | 38.9    | 198      | 1    | 20    | 260.9   |  |

| s35932  | 62   | 18   | 44   | 26243 | 488.2   | 47       | 15   | 3613  | 910.2   |  |

| s38417  | 238  | 90   | 148  | 22963 | 515.6   | 172      | 66   | 12601 | 3903.8  |  |

| s38584  | 412  | 402  | 10   | 3499  | 892.4   | 404      | 8    | 2744  | 1293.2  |  |

| b14     | 1185 | 437  | 748  | 20748 | 20.6    | 717      | 468  | 12232 | 26636.5 |  |

| b15     | 995  | 938  | 57   | 684   | 25.6    | 972      | 23   | 229   | 2215.5  |  |

| b20     | 1399 | 504  | 895  | 28616 | 182.3   | 1022     | 377  | 8556  | 22697.9 |  |

| b21     | 1484 | 662  | 822  | 25857 | 210.6   | 1109     | 375  | 11092 | 22775.4 |  |

| b22     | 1513 | 589  | 924  | 35049 | 606.3   | 1178     | 335  | 8872  | 22529.3 |  |

- [2] J. Savir and S. Patil, "Scan-based transition test," IEEE Trans. Comput. Aided Design Int. Circuits & Syst., vol. 13, no. 8, pp. 1057-1064, 1994.

- [3] L.-T. Wang, C.-W. Wu and X. Wen, VLSI Test Principles and Architectures: Design for Testability, 2006.

- [4] J. Saxena, K. M. Butler, V. B. Jayaram, S. Kundu, N. V. Arvind, P. Sreeprakash and M. Hachinger, "A case study of IR-drop in structured at-speed testing," Proc. ITC, pp. 1098-1104, 2003.

- [5] Y. Zorian, "A Distributed BIST Control Scheme for Complex VLSI Devices," Proc. VTS, pp. 4-9, 1993.

- [6] N. Ahmed, M. Tehranipoor and V. Jayaram, "Transition delay fault test pattern generation considering supply voltage noise in a SOC design," Proc. DAC, pp. 533-538, 2007.

- [7] Y. Bonhomme, P. Girard, L. Guiller, C. Landrault and S. Pravos-soudovitch, "A gated clock scheme for low power scan testing of logic ICs or embedded cores," Proc. ATS, pp. 253-258, 2001.

- [8] P. Rosinger, B. M. Al-Hashimi and N. Nicolici, "Scan architecture with mutually exclusive scan segment activation for shift- and capture-power reduction," IEEE Trans. Comput. Aided Design Int. Circuits & Syst., vol. 23, no. 7, pp. 1142-1153, 2004.

- [9] C. Zhen and X. Dong, "Low-Capture-Power at-speed testing using partial launch-on-capture test scheme," Proc. VTS, pp. 141-146, 2010.

- [10] X. Wen, K. Miyase, S. Kajihara, H. Furukawa, Y. Yamato, A. Takashima, K. Noda, H. Ito, K. Hatayama, T. Aikyo and K. K. Saluja, "A Capture-Safe Test Generation Scheme for At-Speed Scan Testing," Proc. ETS, pp. 55-60, 2008.

- [11] S. Remersaro, X. Lin, Z. Zhang, S. M. Reddy, I. Pomeranz and J. Rajski, "Preferred Fill: A Scalable Method to Reduce Capture Power for Scan Based Designs," Proc. ITC, paper 32.2, 2006.

- [12] X. Wen, K. Miyase, S. Kajihara, T. Suzuki, Y. Yamato, P. Girard, Y. Ohsumi and L. -T. Wang, "A Novel Scheme to Reduce Power Supply Noise for High-Quality At-Speed Scan Testing," Proc. ITC, paper 25.1, 2007.

- [13] X. Wen, K. Miyase, T. Suzuki, Y. Yamato, S. Kajihara, L.-T. Wang and K. K. Saluja, "A Highly-Guided X-Filling Method for Effective Low-Capture-Power Scan Test Generation," Proc. ICCD, pp. 251-258, 2006.

- [14] Y. Yamato, X. Wen, K. Miyase, H. Furukawa and S. Kajihara, "A GA-Based Method for High-Quality X-Filling to Reduce Launch Switching Activity in At-Speed Scan Testing," Proc. IEEE PRDC, pp. 81-86, 2009.

- [15] E. K. Moghaddam, J. Rajski, S. M. Reddy and M. Kassab, "At-Speed scan test with low switching activity," Proc. VTS, pp. 177-182, 2010.

- [16] X. Wen, Y. Yamashita, S. Kajihara, L. -T. Wang, K. K. Saluja and K. Kinoshita, "On Low-Capture-Power Test Generation for Scan Testing," Proc. VTS, pp. 265-270, 2005.

- [17] M. Yoshimura, Y. Takahashi, H. Yamazaki, and T. Hosokawa, "A Don't Care Filling Method for Low Capture Power based on Correlation of FF Transitions Using SAT," IEICE Trans. Fundamentals, Vol. E100-A, no. 12, pp. 2824-2833, 2017.

- [18] K.Miyase, K.Noda, H.Ito, K.Hatayama, T.Aikyo, Y.Yamato, H.Furukawa, X.Wen, and S.Kajihara, "Effective IR-Drop Reduction in At-Speed Scan Testing Using Distribution-Controlling X-Identification," Proc. ICCAD, pp.52-58, 2008.

- [19] I. Pomeranz and S. M. Reddy, "Switching activity as a test compaction heuristic for transition faults," IEEE Trans. VLSI Syst., vol. 18, no. 9, pp. 1357-1361, 2010.

- [20] S. Eggersglüß, "Peak Capture Power Reduction for Compact Test Sets Using Opt-Justification-Fill," Proc. ATS, pp.31-36, 2013.

- [21] S. Cai, C. Luo, J. Thornton, and K. Su, "Tailoring Local Search for Partial MaxSAT," Proc. AAAI Conference on Artificial Intelligence, pp.2623-2629, 2014.

表 3. 提案手法の詳細な実験結果

| Circuit | i    | 1    | 2    | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11 |

|---------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|----|

|         | #TC  | 160  | 60   | 19  | 19  | 19  | 19  | 19  | 18  | 18  | 18  | 1  |

| s5378   | #STV | 100  | 41   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   |    |

|         | #UTV | 60   | 19   | 19  | 19  | 19  | 19  | 18  | 18  | 18  | 18  | 1  |

|         | #TC  | 319  | 226  | 93  | 93  | 93  | 93  | 93  | 93  | 93  | 93  | 9  |

| s9234   | #STV | 93   | 133  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |    |

|         | #UTV | 226  | 93   | 93  | 93  | 93  | 93  | 93  | 93  | 93  | 93  | 9  |

|         | #TC  | 310  | 291  | 2   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |    |

| s13207  | #STV | 19   | 289  | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |    |

|         | #UTV | 291  | 2    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |    |

|         | #TC  | 199  | 187  | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |    |

| s15850  | #STV | 12   | 186  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |    |

|         | #UTV | 187  | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |    |

|         | #TC  | 62   | 62   | 31  | 15  | 15  | 15  | 15  | 15  | 15  | 15  | 1  |

| s35932  | #STV | 0    | 31   | 16  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |    |

|         | #UTV | 62   | 31   | 15  | 15  | 15  | 15  | 15  | 15  | 15  | 15  | 1: |

|         | #TC  | 238  | 238  | 70  | 69  | 68  | 68  | 68  | 68  | 67  | 67  | 6  |

| s38417  | #STV | 0    | 168  | 1   | 1   | 0   | 0   | 0   | 1   | 0   | 1   |    |

|         | #UTV | 238  | 70   | 69  | 68  | 68  | 68  | 68  | 67  | 67  | 66  | 6  |

|         | #TC  | 412  | 412  | 206 | 12  | 8   | 8   | 8   | 8   | 8   | 8   |    |

| s38584  | #STV | 0    | 206  | 194 | 4   | 0   | 0   | 0   | 0   | 0   | 0   |    |

|         | #UTV | 412  | 206  | 12  | 8   | 8   | 8   | 8   | 8   | 8   | 8   |    |

|         | #TC  | 1185 | 1074 | 488 | 481 | 476 | 474 | 472 | 469 | 468 | 468 | 46 |

| b14     | #STV | 111  | 586  | 7   | 5   | 2   | 2   | 3   | 1   | 0   | 0   |    |

|         | #UTV | 1074 | 488  | 481 | 476 | 474 | 472 | 469 | 468 | 468 | 468 | 46 |

|         | #TC  | 995  | 872  | 24  | 23  | 23  | 23  | 23  | 23  | 23  | 23  | 2  |

| b15     | #STV | 123  | 848  | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |    |

|         | #UTV | 872  | 24   | 23  | 23  | 23  | 23  | 23  | 23  | 23  | 23  | 2  |

|         | #TC  | 1399 | 1391 | 497 | 471 | 405 | 390 | 384 | 382 | 380 | 378 | 37 |

| b20     | #STV | 8    | 894  | 26  | 66  | 15  | 6   | 2   | 2   | 2   | 1   |    |

|         | #UTV | 1391 | 497  | 471 | 405 | 390 | 384 | 382 | 380 | 378 | 377 | 37 |

|         | #TC  | 1484 | 1482 | 513 | 476 | 401 | 387 | 383 | 380 | 379 | 378 | 37 |

| b21     | #STV | 2    | 969  | 37  | 75  | 14  | 4   | 3   | 1   | 1   | 2   |    |

|         | #UTV | 1482 | 513  | 476 | 401 | 387 | 383 | 380 | 379 | 378 | 376 | 37 |

|         | #TC  | 1513 | 1513 | 714 | 552 | 441 | 391 | 362 | 355 | 352 | 351 | 34 |

| b22     | #STV | 0    | 799  | 162 | 111 | 50  | 29  | 7   | 3   | 1   | 8   |    |

|         | #UTV | 1513 | 714  | 552 | 441 | 391 | 362 | 355 | 352 | 351 | 343 | 33 |