## テクニカルノート

# CMOS/パス・トランジスタ混在論理の合成とレイアウト

田 出 樹† 克 力 高 敦†, 隆† 昌 宏† 福 冨 黒 木 沼 男† 瀧 和 太

本稿では,論理関数の単純直交分解の結果を表す分解グラフを利用して CMOS 論理とパス・トランジスタ論理を混在させることで,LSI の低消費電力化を実現する合成手法に基づき,多出力回路に対してさらなる論理共有を行い,トランジスタ数を削減する手法を提案する.さらに本手法による合成結果に対して既存ツールによるレイアウトを実現し,実配線を考慮した評価を行うために,CMOS/パス・トランジスタ混在論理用スタンダード・セルライブラリを開発した.このライブラリを用いてベンチマーク回路のレイアウトを行い,実配線を考慮した評価を行った.その結果,CMOS 回路,パス・トランジスタ論理回路,および従来手法で合成した回路に対して,16 例のベンチマーク回路についての平均で,それぞれ 48%,7%,7%の低消費電力化を達成した.

## Synthesis and Layout of Circuits Combining CMOS/Pass Transistor Logic

KENGO TAKATA,††† KAZUKI FUKUOKA,† KATSUYA FUJITA,†

HIRONOBU FUKUTOMI,†• NOBUTAKA KUROKI,† MASAHIRO NUMA,†

KAZUO TAKI† and KEISUKE YAMAMOTO†

We present an improved synthesis method for low power circuits combining CMOS and pass transistor logic (PTL) based on the previous method using decomposition graphs obtained as the result of simple disjunctive decomposition. The proposed method introduces a few techniques for sharing larger part of sub-circuits in a multi-output circuit. In addition, we have developed a standard cell library to evaluate our method based on the layout results using commercial layout tools. This cell library have been applied to the layout design of benchmark circuits, and we have evaluated the results. As the result, power dissipation has been reduced by 48% compared to CMOS, and by 7% to PTL, and by 7% to the previous method in average for 16 circuits.

#### 1. はじめに

携帯機器の急速な普及によるバッテリ持続時間の問題や,動作周波数の高速化による発熱量増加などの点で,LSIの低消費電力化が重要な課題となっている.パス・トランジスタ論理は,トランジスタ数を抑えて負荷容量を減らすことにより低消費電力化を実現する手法として有効である.パス・トランジスタ論理の1つである SPL(Single-rail Pass-transistor Logic) では,MCNCベンチマーク回路のうち多くの回路例

† 神戸大学

Kobe University

†† 日本学術振興会特別研究員

Research Fellow of the Japan Society for the Promotion of Science

現在,奈良先端科学技術大学院大学

Presently with Nara Institute of Science and Technology

に対して,CMOS 論理回路よりも少ないトランジスタ数で実現され,低消費電力となる結果が得られている $^{1)}$ . しかし,すべての回路に対してパス・トランジスタ論理が有利とは限らず,一般に CMOS 論理は AND/OR 回路に,パス・トランジスタ論理はセレクタ回路に有効である $^{2)}$ . そこで,実現すべき関数の種類に応じて CMOS,パス・トランジスタ論理を使い分けて回路を構成することが考えられる $^{2)\sim4}$ ).

我々が提案した  ${\rm CMOS}/{\rm I}$  ス・トランジスタ混在論理合成手法 $^4$ )では,単純直交分解の分解構造を表現する分解グラフ $^{5),6}$ )を利用することで,実現すべき論理関数の性質を考慮して  ${\rm CMOS}$  実現部を選定できる. 文献  $^4$ )では,この分解グラフを利用した  ${\rm CMOS}/{\rm I}$  ス・トランジスタ混在論理合成手法によって合成された回路 ( $0.35\,\mu{\rm m}$  プロセス)に対して,一定の仮想配線容量を付加して回路シミュレーションによる評価を

図 1 提案手法の処理概要 Fig. 1 Overview.

Fig. 2 Extraction of equivalent subgraphs.

行った.その結果,CMOS 回路と比較すると,実験回路40例のうち約半数において遅延時間を短縮,36例において消費電力を低減でき,手法の有用性が確認できた.その一方で,多出力回路に対するさらなる論理共有の可能性検討と,実際にレイアウトを行った後の実配線を考慮した評価が課題として残されていた.

そこで本稿では,文献 4) で提案した従来手法をもとにさらなる論理共有を行う手法を提案する.さらに,本手法によって合成した回路のレイアウトを実現するために,スタンダード・セルライブラリを開発した.本稿では,このセルライブラリを用いたベンチマーク回路のレイアウト結果に対して回路シミュレーションを行い,実配線を考慮した評価を行う.

## CMOS/パス・トランジスタ混在論理 合成手法の改良

本章では,多出力回路に対してさらなる論理共有を行う手法を提案する.処理概要を図1に示す.2つ目の「部分回路とする箇所の選定と置換」を従来手法<sup>4)</sup>に対して追加するとともに,CMOS 実現部の合成方法を変更した.以下,処理概要について簡単に述べる.

まず与えられた論理関数より分解グラフを作成する.次に,部分回路とする箇所の選定と入力変数への置換を行う.この分解グラフより,次に定義する OR サブッリー部分を CMOS 実現部として選定・合成する.

定義 1 OR サブツリー<sup>4)</sup>

分解グラフのある OR ノード $^{5),6)}$  において,その子孫のノードがすべてリテラルノード $^{5),6)}$  か OR ノードであるサブツリーを OR サブツリーと呼ぶ.  $\Box$ この OR サブツリーを除いた部分については,文献

4) と同様の合成手法により , パス・トランジスタ論理 で実現する .

本稿で提案する手法は,従来手法 $^4$ )に対して以下で述べる  $^4$  点を変更している  $^4$  点を変更している  $^4$  に対応し, $^4$  に対応し, $^4$

図3 OR ノードの分解と共有論理の抽出 Fig. 3 Extraction of shared logic via decomposition of OR

Fig. 3 Extraction of shared logic via decomposition of OR node.

が CMOS の合成法に関する変更である.

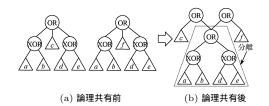

#### (1) 論理が等しい部分グラフの抽出

分解グラフは,論理関数に対して一意に求められ  $\delta^{5),6)}$ . そこで,等しい論理関数より求められる部分 グラフは, 実装上, 複数出力間で共有して保持してい る. 文献 4) では,このような共有された部分グラフ も回路全体の BDD に含めてパス・トランジスタ論理 として合成していたため, BDD の同形部分として重 複して現れる場合があった.この問題を解決するため に,図2に示す XOR ノード<sup>5),6)</sup> のように,ノードを 参照する親ノードが複数存在する場合は,そのノード 以下を分離して独立した部分回路とし,新たな入力変 数(図2ではn)で置換する.この方法によって,複 数の出力間で共通部分関数を共有することが可能とな る. また, 図2のOR ノードのように, 子孫である部 分グラフが新たな入力変数に対応するリテラルノード に置換されることによって,新たに OR サブツリーと なる部分が出現することがある.その場合は,CMOS 実現部として選定可能な OR サブツリーが増える.

(2) OR ノードの分解と共有論理の抽出 分解グラフでは,一意性を保つために OR ノードは 構築可能な限り 1 つにまとめられる $^{5),6)}$ . そのため, 図  $\mathbf{3}$  (a) の 2 つの OR ノードは別個の OR ノードとし て扱われ,そのままでは (1) の操作において,図  $\mathbf{3}$  (b) に示すような共有論理が抽出されない.そこで,(1) の操作中に OR ノード間で互いに重複する複数の子 ノードを抽出することで,図  $\mathbf{3}$  (b) に示すような共有 論理の抽出を可能とする.

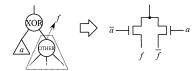

## (3) XOR ノードの子ノードの分離 う解グラフの XOR ノードをパス・トラ

分解グラフの XOR ノードをパス・トランジスタ論理で合成する場合,図 4 に示すように,子ノードについて正負両方の論理(a b  $\overline{a}$ , f b  $\overline{f}$ )を必要とする.そこで,(1) の操作において,XOR ノードの子ノードは必ず複数の親から参照されていると見なし,部分回路として抽出する.子ノードの負論理  $\overline{f}$  は,抽出した部分回路の出力 f をインバータで反転することで生成する.この結果,負論理出力に対応する回路を生

図 4 XOR ノードと対応する回路 Fig. 4 XOR node and its implementation.

成する必要がなくなり、トランジスタ数を削減できる.

#### (4) CMOS 実現部の合成

選定された CMOS 実現部の合成について,文献 4)の実装段階では,限られた種類のゲートへのみマッピングが可能であった.本手法では,多様な CMOS セルライブラリに対応するために,CMOS 実現部はまず論理式として出力し,その論理式より市販の論理合成ツールを用いて合成する.この結果,CMOS 実現部においてライブラリに適したマッピングが行われ,わずかながらトランジスタ数の削減効果も期待できる.

#### 3. 実験評価

本手法による合成結果に対して実配線を考慮した評価を行うために,スタンダード・セルライブラリを開発した.本手法で採用している  $\mathrm{SPL}^1$ )は  $\mathrm{nMOS}$  のみで論理部分を構成するため, $\mathrm{n}$  拡散領域を広くとるセル構成にしている.そのため, $\mathrm{CMOS}$  セルとパス・トランジスタ論理セルが隣接すると設計ルール違反が生じる.そこで境界用セル $^7$ )を用意し, $\mathrm{CMOS}$  セルとパス・トランジスタ論理セルが隣接する場合にはこれらを自動的に移動させて設計ルール違反を解消する.また, $\mathrm{CMOS}$  論理部分とパス・トランジスタ論理部分を同一セル内に格納するセルを用意し,個別にセルを使用する場合より面積を削減可能としている.

MCNC LGSynth91 ベンチマーク回路のうち,レイアウトや回路シミュレーションに要する時間を考慮して 16 例を選択した.それぞれの回路に対して,CMOS回路,SPL 回路,および従来手法 $^4$ )と本手法で合成した CMOS/パス・トランジスタ混在回路の 4 種類のレイアウトを行った.プロセスルールは  $0.35~\mu\mathrm{m}$  ,電源電圧は  $3.3~\mathrm{V}$  とした.CMOS 回路は,スタンダード・セルライブラリを適用して市販の論理合成ツールで合成した.制約条件として最大面積 0 を与えた.SPL 回路は,SPL 用論理合成  $\mathrm{CAD}^{1}$ )を用いて合成した.

#### 3.1 トランジスタ数に関する結果

表 1 にトランジスタ数に関する結果を示す.表 1 より, CMOS 回路に対して平均で 14%の削減効果が得

表 1 トランジスタ数に関する結果 Table 1 Transistor counts.

| 回路名    | CMOS  | SPL   | 従来<br>手法 | 提案<br>手法 | 提案<br>CMOS | <u>提案</u> 提案<br>SPL 従来 |

|--------|-------|-------|----------|----------|------------|------------------------|

| alu2   | 1166  | 546   | 519      | 607      | 0.52       | 1.11 1.17              |

| b1     | 14    | 16    | 15       | 13       | 0.93       | $0.81\ 0.87$           |

| ь9     | 339   | 461   | 429      | 348      | 1.03       | 0.75  0.81             |

| c8     | 342   | 281   | 309      | $^{265}$ | 0.77       | $0.94\ 0.86$           |

| сс     | 170   | 187   | 174      | 185      | 1.09       | 0.99 1.06              |

| cm151a | 70    | 47    | 55       | 47       | 0.67       | $1.00\ 0.85$           |

| cm163a | 134   | 110   | 112      | 136      | 1.01       | $1.24\ 1.21$           |

| cm85a  | 140   | 143   | 157      | 125      | 0.89       | 0.87  0.80             |

| cordic | 196   | 254   | 201      | 202      | 1.03       | 0.80 1.00              |

| cu     | 159   | 166   | 167      | 159      | 1.00       | 0.96  0.95             |

| f51m   | 323   | 213   | 199      | 192      | 0.59       | 0.90  0.96             |

| pcle   | 241   | 245   | 222      | 180      | 0.75       | $0.73\ 0.81$           |

| pm1    | 137   | 180   | 136      | 147      | 1.07       | 0.82 1.08              |

| t481   | 106   | 95    | 113      | 99       | 0.93       | $1.04\ 0.88$           |

| x2     | 147   | 129   | 121      | 133      | 0.90       | $1.03 \ 1.10$          |

| z4ml   | 106   | 94    | 106      | 84       | 0.79       | 0.89  0.79             |

| 幾何平均   | 162.3 | 150.8 | 147.6    | 139.0    | 0.86       | 0.92 0.94              |

られたことが分かる.トランジスタ数が増加した回路は 16 例中 5 例に限られ,トランジスタ数削減に対する有効性が認められる.SPL 回路に対しては 8%の削減効果が得られるとともに,16 例中 11 例について,より少ないトランジスタ数で回路を実現できた.従来手法に対しては 6%の削減効果が得られた.

なお,使用したセルライブラリが異なることや,パス・トランジスタ部分のレイアウトにおいてファンアウトを考慮して入力インバータ数を増やしたことから,文献 4) と同じ回路でもトランジスタ数は異なる.従来手法4) と入力インバータ数に関して同一条件で比較すると,トランジスタ数が平均で 1%削減されており,本稿で提案した手法による改善が見られる.特に,回路例 cordic では 11%,pcle では 17%削減され,効果的に作用している.また,2 章 (1)~(3) の工夫によって,回路例 b9 では分解グラフにおける 29 個のノードが部分回路として抽出され,トランジスタ数を 19%削減できた.さらに回路例 x2 に対して 2 章 (4) の効果を調べると,トランジスタを 4 個削減できる結果が得られた.

### 3.2 遅延時間と消費電力に対する結果

次に,遅延時間と消費電力に対する結果について述べる.遅延時間は PathMill で求め,消費電力はランダムに生成した 100 個の入力パターンを各回路に与え,HSPICE による回路シミュレーションで求めた.表 2 に遅延時間と消費電力に関する結果を示す.遅延時間について,CMOS 回路に対してはほぼすべての回路で遅延時間が増加しており,平均で 87%の増加となった.一方で SPL 回路に対しては,16 例中 9 例の回路において遅延時間が短縮され,平均では 24%短縮できた.従来手法4) に対しては半数の回路で遅延時間

| 表 | 2 | ì | 星延 | 時間 | 間と消費電力 | こに関す | る結果 | ŧ |

|---|---|---|----|----|--------|------|-----|---|

| - | - |   | _  | _  | _      |      |     |   |

Table 2 Delay and power dissipation.

|        | 遅延時間 [ns] |       |          |          |            |           |          | 消費電力 $[\mu W]$ |       |          |          |            |           |          |

|--------|-----------|-------|----------|----------|------------|-----------|----------|----------------|-------|----------|----------|------------|-----------|----------|

| 回路名    | CMOS      | SPL   | 従来<br>手法 | 提案<br>手法 | 提案<br>CMOS | 提案<br>SPL | 提案<br>従来 | CMOS           | SPL   | 従来<br>手法 | 提案<br>手法 | 提案<br>CMOS | 提案<br>SPL | 提案<br>従来 |

| alu2   | 8.19      | 8.15  | 9.27     | 20.08    | 2.45       | 2.46      | 2.17     | 860.6          | 174.7 | 158.5    | 165.0    | 0.19       | 0.94      | 1.04     |

| b1     | 0.38      | 0.68  | 0.71     | 0.72     | 1.91       | 1.05      | 1.00     | 15.3           | 15.1  | 14.8     | 14.7     | 0.96       | 0.97      | 0.99     |

| ь9     | 1.91      | 11.95 | 6.22     | 4.45     | 2.33       | 0.37      | 0.72     | 155.0          | 240.8 | 127.2    | 113.8    | 0.73       | 0.47      | 0.89     |

| c8     | 3.53      | 10.09 | 2.38     | 5.23     | 1.48       | 0.52      | 2.20     | 197.2          | 95.6  | 94.7     | 85.1     | 0.43       | 0.89      | 0.90     |

| сс     | 1.89      | 2.61  | 1.86     | 2.88     | 1.52       | 1.10      | 1.55     | 87.3           | 56.9  | 64.5     | 60.0     | 0.69       | 1.06      | 0.93     |

| cm151a | 1.30      | 1.83  | 2.63     | 1.90     | 1.47       | 1.04      | 0.72     | 43.9           | 21.5  | 23.0     | 21.5     | 0.49       | 1.00      | 0.93     |

| cm163a | 1.56      | 2.72  | 3.21     | 2.55     | 1.64       | 0.94      | 0.79     | 74.7           | 37.2  | 39.9     | 41.1     | 0.55       | 1.10      | 1.03     |

| cm85a  | 2.25      | 6.92  | 3.26     | 6.47     | 2.88       | 0.94      | 1.98     | 93.7           | 38.3  | 42.5     | 36.7     | 0.39       | 0.96      | 0.86     |

| cordic | 1.99      | 17.22 | 7.11     | 4.77     | 2.40       | 0.28      | 0.67     | 113.0          | 48.4  | 53.7     | 107.5    | 0.95       | 2.22      | 2.00     |

| cu     | 1.31      | 4.76  | 2.36     | 7.37     | 5.62       | 1.55      | 3.13     | 74.6           | 47.5  | 50.4     | 37.3     | 0.50       | 0.79      | 0.74     |

| f51m   | 3.96      | 5.15  | 5.77     | 3.58     | 0.90       | 0.69      | 0.62     | 250.4          | 68.2  | 74.6     | 81.8     | 0.33       | 1.20      | 1.10     |

| pcle   | 3.75      | 4.00  | 4.23     | 5.42     | 1.44       | 1.36      | 1.28     | 156.4          | 60.3  | 62.7     | 51.7     | 0.33       | 0.86      | 0.82     |

| pm1    | 1.52      | 3.58  | 2.70     | 1.53     | 1.01       | 0.43      | 0.57     | 53.8           | 44.2  | 44.5     | 43.5     | 0.81       | 0.99      | 0.98     |

| t481   | 1.30      | 14.51 | 3.11     | 2.35     | 1.81       | 0.16      | 0.76     | 60.7           | 107.2 | 60.0     | 37.4     | 0.62       | 0.35      | 0.62     |

| x2     | 1.09      | 2.13  | 2.52     | 3.00     | 2.74       | 1.41      | 1.19     | 66.8           | 36.9  | 64.1     | 42.2     | 0.63       | 1.14      | 0.66     |

| z4ml   | 1.52      | 3.91  | 3.15     | 2.23     | 1.47       | 0.57      | 0.71     | 101.0          | 38.0  | 41.6     | 40.6     | 0.40       | 1.07      | 0.98     |

| 幾何平均   | 1.87      | 4.63  | 3.22     | 3.49     | 1.87       | 0.76      | 1.08     | 98.5           | 54.8  | 54.7     | 51.1     | 0.52       | 0.93      | 0.93     |

を短縮できたが,平均では 8%の増加となった.これは部分回路に付加された出力バッファのためと考えられる.次に消費電力について,CMOS,SPL,従来手法 $^{4)}$  に対して,平均でそれぞれ 48%,7%,7% の低消費電力化を実現できた.特に CMOS 回路に対しては,すべての回路で消費電力を削減できた.

以上の結果より、分解グラフを用いて関数に適した 論理構成方式を採用する提案手法による、低消費電力 化の効果が確認された、従来手法に対しては、トラン ジスタ数において6%の削減効果を得られたことから、 7%の低消費電力化を実現できた。

#### 4. ま と め

分解グラフを利用して適切な論理構成方式を使い分ける従来手法 $^4$ )をもとに,さらなる論理共有を行う手法を提案した.開発したスタンダード・セルライブラリを用いて行ったレイアウト結果に対して回路シミュレーションによる評価を行った結果, ${

m CMOS}$ , ${

m SPL}$ ,従来手法 $^4$ )に対してそれぞれ 48%,7%,7%の低消費電力化を達成した.

開発したセルライブラリではパス・トランジスタ,インバータ,プルアップ用 pMOS トランジスタなど,用途ごとにトランジスタ・サイズを一定にしている.今後の課題としては,個々のトランジスタについてさまざまなサイズへトランジスタ・サイジングを行い,セルライブラリを改良することがあげられる.

謝辞 単純直交分解手法についてご教示をいただい た九州大学松永裕介助教授に深謝します.

本稿の実験評価は,東京大学大規模集積システム設計教育研究センターを通し,ローム(株)および凸版印刷(株)の協力で行われたチップ試作を前提とした

ものである.レイアウトの配置配線は Avant!ツールを用いて行われたものである.なお本研究の一部は, 文部省科学研究費補助金(特別研究員奨励費)による.

### 参考文献

- 1) Konishi, K., Kishimoto, S., Lee, B.-Y., Tanaka, H. and Taki, K.: A logic synthesis system for the pass-transistor logic SPL, *SASIMI* '96, pp.32–39 (1996).

- Yamashita, S., Yano, K., Sasaki, Y., Akita, Y., Chikata, H., Rikino, K. and Seki, K.: Passtransistor/CMOS collaborated logic: The best of both worlds, Symposium on VLSI Circuits, pp.31–32 (1997).

- 3) 岡部直樹,北村清志,瀧 和男:パストランジスタ/CMOS 混在による低消費電力 LSI 設計,第2回システム LSI 琵琶湖ワークショップ,pp.289-291 (1998).

- 4) 高田賢吾,神野元彰,黒木修隆,沼 昌宏,瀧 和男,山本啓輔: CMOS/パス・トランジスタ論 理の混在による低消費電力回路の合成,情報処理 学会論文誌, Vol.42, No.4, pp.967-974 (2001).

- 5) Bertacco, V. and Damiani, M.: The disjunctive decomposition of logic functions, *ICCAD* '97, pp.78–82 (1997).

- 6) Matsunaga, Y.: An exact and efficient algorithms for disjunctive decomposition, *SASIMI* '98, pp.44–50 (1998).

- 7) 田中秀樹, 李 副烈,瀧 和男,宇田研一郎,北 村清志,村田 豊:パストランジスタ論理のため のセル開発とその応用,情報処理学会研究報告, Vol.97, No.DA-86, pp.25-32 (1997).

(平成 13 年 9 月 25 日受付) (平成 14 年 3 月 14 日採録)