# ブリッジ故障対応 IDDQ テストで用いる 近接配線ペアリストの効率的生成手法

## 伊藤俊明<sup>†</sup> 金本俊幾<sup>†</sup> 小谷 憲<sup>†</sup> 清水良浩<sup>†</sup> 寺井正幸<sup>††</sup>

本論文では、IDDQ テストにおけるブリッジ故障候補の絞り込みに用いる近接配線ペアリストの効率的な生成手法を提案する、IFA (Inductive Fault Analysis) における CA (Critical Area) 関数を適用し、ブリッジ故障を引き起こす異物粒子の直径とブリッジ故障発生確率の関係について実際の LSI 製造プロセスから抽出した統計データへこの関数をフィッティングする、次に、各配線ペアごとに CA 関数に基づきブリッジ故障確率を計算し、これに従って優先度をつけた近接配線ペアリストを作成する、後の IDDQ テスト故障診断において、このリストを故障検出率の高いテストパターン作成とテストのフェイル結果から実チップの故障箇所を推定するのに利用する、評価結果から、提案手法が生成した近接配線ペアリストを用いることによりブリッジ故障診断はその処理時間が大幅に短縮され、5M ゲート規模のシステム LSI に適用可能となることを示す。

### Method of Extracting Pairs of Adjacent Wires for Diagnosing Bridging Faults Based on IDDQ Testing

Toshiaki Ito,† Toshiki Kanamoto,† Satoshi Kotani,† Yoshihiro Shimizu† and Masayuki Terai††

This paper proposes a new method of extracting pairs of adjacent wires from the mask layout of LSIs and efficiently calculating the probability of a bridging fault that a short between each pair of adjacent wires is caused in the fabrication process. The information produced by the method can greatly reduce the number of fault candidates handled in IDDQ testing. Therefore, it improves the efficiency of IDDQ test pattern generation and diagnosis very much. In order to improve the accuracy of the probability, we apply a critical area model function of IFA (Inductive Fault Analysis) and fit the function into process statistics data of relation between diameter x of a particle and the probability of the event that a short is caused by a particle having diameter x. The application results show that the proposed method has greatly reduced the time spent on the diagnosis of IDDQ testing and enables the diagnosis to be applied to 5M-gate LSIs.

### 1. はじめに

CMOS 大規模集積回路 LSI の製造プロセスでの random defect (異物欠陥)により引き起こされるブリッジ故障 (短絡故障)や酸化膜欠陥によるトランジスタリーク故障に対する有効なテスト手法として IDDQ テストが行われている $^{1)}$  . IDDQ テストとは静的な電源電流 (IDDQ) を測定するテスト手法であり,故障のない正常な CMOS ディジタル回路では IDDQ がほ

とんど流れないため,IDDQ を測定することによって 故障の有無を調べることができる.IDDQ テストは論 理値が不確定となるブリッジ故障も検出することができ,また故障検出のために故障の影響を外部出力まで 伝播させる必要がないためテスト生成も容易になると いう特長がある.IDDQ テストの時間は印加するテストベクトル数に依存するが,過渡的な動的電流がなく なった後に,IDDQ を測定しなければならないためテスト時間が長くなる.近年の微細化技術による VLSI では回路規模とともに大規模になるテストベクトル数の がり込み,テスト時間を短縮することがきわめて重要である.IDDQ テストにおいてテストベクトル数の 上限制約の下でテスト検出率を最大化することが要求 される.このため,検出対象故障をレイアウトデータ

LSI Product Technology Unit, Renesas Technology Corporation

†† 大阪学院大学情報学部

Faculty of Informatics, Osaka Gakuin University

<sup>†</sup> 株式会社ルネサステクノロジ製品技術本部

中での近接配線間のブリッジ故障に限定し,あらかじめ与えられたテストベクトル集合を,元の故障検出率を保持しつつ圧縮を行う.この目的のためにレイアウトデータから近接配線ペアを抽出しこれを IDDQ テストのブリッジ故障候補にすることが有効である $^{2)-6}$  . しかし,これらの既発表の手法は近接配線ペアに対するブリッジ故障発生確率の評価を行っていない $^{2)-4$ ,6)か,隣接配線の並走距離の重み付けによる近似的な評価 $^{5}$  である.

一方,テストベクトルの評価のために,回路レイアウトと異物発生密度(defect density)を入力として,異物による故障要因を分類しランキングする IFA (Inductive Fault Analisis) が報告されている $^{7),8)}$ .

本論文では、ブリッジ故障の絞り込みと IDDQ テス ト時間短縮のためにレイアウトデータ LEF/DEF か ら近接配線ペアを抽出しそれらのブリッジ故障の発生 確率を計算する手法を提案する.これを近接配線ペア リスト作成と呼ぶ.本論文のブリッジ故障確率評価方 法は IFA と同じ考え方に基づいているが,提案手法 の新規性は次の 2 点である . (1) IFA で使用されてい るブリッジ故障確率評価方法を初めて IDDQ テスト の故障診断に適用した.IFA による評価と IDDQ テ ストの故障診断とのインタフェースとして近接配線ペ アリスト (配線ペアごとのブリッジ故障確率の評価値 を IDDQ テストの故障解析支援のために危険度の高 い順に記述したファイル)を提案した.(2)自動配線 プログラムで設計した LSI 回路のレイアウト図形の特 徴, すなわち, レイアウト図形中に非常に多くの一定 幅の配線図形が一定距離の整数倍の間隔で並んでいる ことを活用し,異物径レンジのn分割離散化を行い, ブリッジ故障発生確率評価の精度を維持しつつ,高速 化した.この結果, 5M ゲート級 VLSI に一括適用可 能となった.

$90 \, \mathrm{nm} \,$  テクノロジの  $5 \mathrm{M} \,$  ゲート規模の LSI 回路をはじめとする数種の LSI 回路に提案手法を適用した結果から,提案手法の有効性を示す.

以下では,2 章「IDDQ テストと近接配線ペアリスト」,3 章「近接配線ペア抽出と故障確率の計算」,4 章「評価実験」,5 章「まとめ」の順に述べる.

#### 2. IDDQ テストと近接配線ペアリスト

本章では,ブリッジ故障モデルと故障辞書,IDDQ テスト診断フローについて説明した後,近接配線ペア リスト作成の狙いについて述べる.

#### 2.1 ブリッジ故障モデルと故障辞書

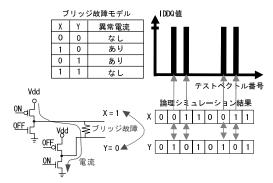

配線間のブリッジ故障の例を図1に示す.図1の真

図 1 セル間配線ブリッジ故障と IDDQ 異常電流

Fig. 1 Physical bridge fault between two nodes and the resultant irregular electric current.

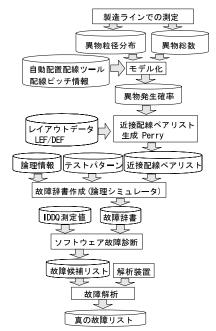

図 2 IDDQ テスト故障診断フロー

Fig. 2 Flow diagram of IDDQ fault location diagnosis.

理値表はブリッジ故障により短絡している 2 つの配線の論理値が一方が '1' で他方が '0' であるとき IDDQ 異常が発生することを示している . 信号配線 X と Y の ブリッジ故障を仮定した場合に論理シミュレータを用いてテストベクトルごとの信号線 X と Y の論理値テーブルを作成し , 一方が '1' で他方が '0' となり IDDQ 異常が発生するテストベクトルを記憶する . 故障辞書とは , 対象とするブリッジ故障群のそれぞれに対するテストベクトルと IDDQ 異常の有無を組み合わせたデータベースである .

#### 2.2 IDDQ テスト診断フロー

IDDQ テストの故障診断のフローを図 2 に示す.本

フローは CAD プログラム Perry , 小五郎 Iddq , 小五郎 Reasoning として実現され , 他に小五郎 Scan , 小五郎 Func とともに LSI 故障位置指摘システム小五郎<sup>9),10)</sup> を構成している .

近接配線ペアリスト生成ツール Perry が提案手法を実現したプログラムで,Perry はレイアウトデータ LEF/DEF を入力として近接配線ペアリストを作成する.故障辞書作成は近接配線ペアリストを入力として各配線ペア間のブリッジ故障を仮定し故障辞書を作成する.次に,故障診断では IDDQ 測定値と故障辞書を入力として故障位置の指摘を行う.一般に故障辞書は多重故障には対応できないので,テストパターンの分解能が低い場合には数多くの故障候補を指摘してしまい,真の故障箇所を絞りきれないことがある.故障解析支援は,故障診断結果の故障候補リストを入力として回路図表示,マスクレイアウト表示,発熱解析(液晶塗布法),発光解析(エミッション顕微鏡,OBIRCH解析)を活用して真の故障を特定する.

#### 2.3 近接配線ペアリスト

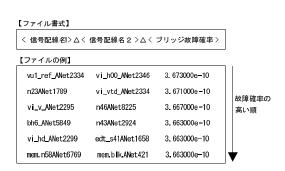

近接配線ペアリストは図3に示すように2つの信号配線名とその間のブリッジ故障発生確率を記述したファイルである.配線ペアは故障確率の高い順に並んでいる.

近接配線ペアリストは,(1) 検出対象故障の絞り込み,(2) 高い故障検出率の確保と,(3) 故障解析の効率化のために発生確率の高い故障候補から順に解析することに用いる.すなわち,近接配線ペアリストはIDDQ テストの効率を向上させる.ブリッジ故障候補の総数は信号線数の2乗に比例する.現状の適用対象のLSI は5M ゲート規模にも達しうるので全候補を扱うことは現実的ではない.したがって,検出対象故障を近接配線ペアに限定し,その故障検出率を高める(典型例,90%前後)ようにテストパターンを作成する.

図 3 近接配線ペアリスト

Fig. 3 Pair-list of adjacent wires.

#### 3. 近接配線ペア抽出と故障確率の計算

#### 3.1 処理フロー

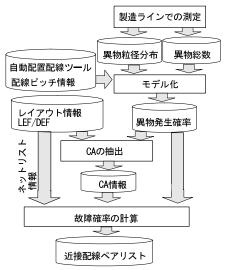

配線ペアについての故障確率の計算は,IFA における WCA 値の計算 $^{7}$ )と基本的な考え方は同じであるが,図  $^{4}$  に示すように,対象となる製造ラインにおける製造工程ごと,粒径ごとの異物発生確率の計算,CA の抽出,各近接配線ペアに関する故障確率計算のステップで実施する.

なお、本論文で考慮する故障は、異物の発生による単一層(特に配線層)内でのブリッジ故障(random defect)であり、レイアウト形状を要因とする故障(systematic defect)については、考慮しない、

異物発生確率は,粒径分布関数を,製造ラインでの 異物測定結果および実際の製品の歩留まりデータに フィッティングすることにより求める.なお,歩留ま りが安定した製造方式では,基本的に一度フィッティ ングを実施すれば,その関数を汎用的に使用可能であ るが,開発初期の製造方式の場合,時期ごとの製造ラ インの状態変動が激しく,本手法適用の直前での測定 結果に基づくフィッティングが必要となる.

異物発生確率の計算は,配線層ごとに実施し,まず一般的な分布関数にあてはめた後,後段の処理を高速化するために,扱う異物径のレンジをn分割して $x_0,x_1,\cdots,x_n$ に離散化を行い,異物粒径群とそれら異物粒径ごとの発生確率の対応について,配線層ごとの表としてモデル化する.図 5 に例を示す.たとえば,

図 4 近接配線ペア抽出と故障確率計算のフロー

Fig. 4 Flow diagram of extracting pairs of adjacent wires and calculating the probability of a physical bridge fault.

| 配線層  | 異物粒径<br>(x0) | 異物粒径<br>(x1) | <br>異物粒径<br>(xn) |

|------|--------------|--------------|------------------|

| 配線層  | DyC/Dall*    | DyC/Dall*    | <br>DyC/Dall*    |

| (y0) | f(x0, y0)    | f(x1, y0)    | f (xn, y0)       |

| 配線層  | Dy1/Dall *   | Dy1/Dall*    | <br>Dy1/Dall*    |

| (y1) | f(x0, y1)    | f(x1, y1)    | f (xn, y1)       |

|      |              | • •          | <br>             |

| 配線層  | Dynr/Dall*   | Dym/Dall∗    | <br>Dynr/Dall∗   |

| (ym) | f(x0,ym)     | f(x1,ym)     | f(xn, ym)        |

図 5 ブリッジ故障発生モデル例

Fig. 5 Example of function table calculating the probability of a physical bridge fault.

図中の  $\mathrm{Dy1/Dall*f(x1,y1)}$  は,異物粒径が  $\mathrm{x1}$  以上で  $\mathrm{x2}$  未満の異物の配線層  $\mathrm{y1}$  上での発生確率を表す.文献  $\mathrm{5}$ ), $\mathrm{6}$ )でも述べられているが,レイアウトのデー 夕形式としては一般的なデータ形式として  $\mathrm{GDS2}$  もしくは  $\mathrm{LEF/DEF}$  の  $\mathrm{2}$  種類が存在する.本手法では,処理の高速性を求め  $\mathrm{LEF/DEF}$  を入力情報として採用する.

${

m CA}$  の抽出は前記異物発生のモデルで定義される異物粒径  $x_i$  (  $i=0,1,\cdots,n$  ) ごとに , サイズ  $x_i$  の異物によりブリッジ故障を発生しうる距離にて隣接する図形要素ペアを見つけその  ${

m CA}$  を抽出する .

ここでいう CA とは,直径 x の異物の中心が当該領域内に存在した場合に 2 つの配線図形間にブリッジ 故障を引き起こしうる領域のことであり,当該領域を粒径 x の異物に対する Critical Area (以下 CA と呼ぶ)と定義する $^8$  . あとで説明するが,図 7 に CA の例を示す.さらに抽出後の図形要素をネットリストの接続情報に基づき,配線ペアごとの CA にまとめあげ,各粒径ごとの異物発生の情報を加えることにより,各配線ペアについて,当該工程で発生する異物によるブリッジ故障の確率を求める.

最終的には全配線層に関するブリッジ故障の確率を 計算し、順位付けを行った近接配線ペアリスト群を導 き出す.

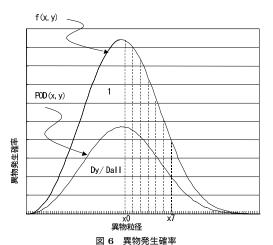

#### 3.2 異物発生確率計算

製造ラインにおいて,シリコン基板上に測定用のテストレイアウトパターンを作り,結果を発光テスト等で測定することにより,配線プロセス工程ごとに,ブリッジ故障の要因となりうる異物について,以下の情報を求める.

- ・異物粒径の分布関数

- ・ブリッジ故障の要因となりうる異物の総数

配線層 y における異物粒径 x の分布 (f(x,y))については,分布関数を 1 に規格化した場合,プロセスの製造条件限界により定まる各工程での最小図形間隔

Fig. 6 The probability of a particle's existence.

$x_0$  を最小値とし,異物発生確率が規定値を下回る図形間隔を最大値とする領域について最小 2 乗法により,発塵現象のモデル化に適した粒径分布関数 (Rossin-Rammler の式 $^{11}$ )式 (1)にフィッティングすることが可能である (Ky,Ny) はフィッティングパラメータ).

$$F(x,y) = 1 - \exp\{(-(x/K_y)^{N_y})\}$$

$$f(x,y) = dF(x,y)/dx$$

(1)

フィッティングした粒径分布関数 f(x,y) に対し,当該配線層の異物の総数  $D_y$  を全配線層の異物の総数  $D_{all}$  で割ったものをかけることによって,当該配線層での粒径 x の異物の発生確率 POD(x,y) を求めることができる(式 (2)).

$$POD(x,y) = D_y/D_{all} \cdot f(x,y)$$

(2)

図 6 に各関数の関係の概略を示す.ここまでで,粒径ごとの異物発生確率をモデル化することができたが,異物の粒径 x を連続的に変動させて対応する CA をレイアウト情報から抽出する場合,後述のとおり膨大な計算時間が必要となるため,POD(x) を離散化し,処理を現実的なものとする.

今回の手法の計算時間については 3.3 節と評価実験の章で述べるが,離散化処理なしの場合では,たとえば,取り扱う最小図形単位を  $0.001\,\mu\mathrm{m}$  とし,取り扱う異物のレンジを  $0.3\sim3\,\mu\mathrm{m}$  とした場合,n=1,000 となりこの n に比例する計算時間が必要となり,大規模な LSI への適用は実際には不能となる.

離散化は配置配線ツールの配線ピッチを基本に実施する.これは,現状の LSI の配線層の図形については,自動配置配線ツールで設計される図形の占める割合が支配的であり,当該図形寸法は,一定の配線幅および配線間隔の倍数で形成される.この場合,当該固定値の配線間隔ごとにブリッジ故障を発生しうる異物

径を逆算し,異物ごとのステップ関数を作成することにより,抽出精度を大きく悪化させることなく,離散化が実現できる.なおステップ関数作成時のxの下限値としては,最小の配線ピッチを採用し,上限値としては,設定されている配線ピッチのうち,発生確率が規定値を下回るものを採用する.

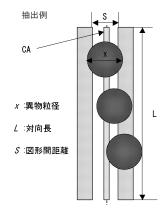

#### 3.3 CA 抽出と故障確率の計算

本節では、各異物粒径ごとのブリッジ故障発生確率を求めるために必要な CA の抽出方法について述べる、異物はチップ内のどの場所についても同一確率で発生するものとし、各異物の発生について相関関係はないという前提でモデル化する、図7に異物粒径とレイアウト情報の関係の概念図を示す.

図 7 に示すように , 配線層 y において , 距離 S , 対抗長 L にて隣接する 2 つの図形のペア p が , 粒径 x の異物によりブリッジ故障を起こす確率 CA(x,y,p) は図中の CA 内に中心を持つ異物が発生する確率と等価となり , CA の面積とチップ全体の面積 A の比として表現でき , 式 (3) のようになる .

$$CA(x, y, p) = 0 \qquad (x < S)$$

$$\frac{(x - S) \cdot L}{A} \quad (S \le x) \qquad (3)$$

なお,図 7 は平行な 2 つの図形間のショートをモデル化したものであるが,x が十分大きい場合には 3 本以上の配線を同時にショートさせるケースについても同じモデルでその発生確率の評価が可能である.各異物粒径ごとの発生確率およびブリッジ故障発生確率についてここまででモデル化できたが,この結果を利用すれば,各配線ペア p ごとの故障発生確率 POF(p) は,各配線層 y ごと,異物粒径 x ごとの異物の発生確率 POD(x,y) と当該異物に対する CA の面積の和 CA(x,y,p) により式 (4) のように求めることが可能

図 7 異物粒径とレイアウト情報の関係

Fig. 7 A particle's diameter and the corresponding layout critical area.

となる.

$$POF(p) = \sum_{u}^{all\_step} \sum_{x} (POD(x, y) \cdot CA(x, y, p)) \quad (4)$$

ここで配線層 j において,異物粒径  $x_i$  の CA を 抽出する手法とその計算量について簡潔に述べる.今 回,本手法を実現するにあたり,各図形情報は頂点情 報の集合として quad tree 構造のデータベースで管 理する.各図形間の間隔は,異物粒径  $x_i$  の 1/2 拡 大した図形情報に対して,平面走査法(plane sweep method)を適用して, tree 構造のソートおよび分割 を実施することにより,オーバラップする図形すなわ ち異物粒径  $x_i$  に対する CA を持つ配線ペアを抽出す る手法をとる.これらの処理はすべて  $O(N_i \cdot \log N_i)$ の手間で実行できる $^{12)}$ .ここで  $N_j$  は配線図形の総 数である、図形ペアからその CA は O(1) の手間で計 算できるので,図5の異物の発生モデルが与えられて 全配線図形ペアに対し式 (4) の POF(p) を計算する のに  $O(\Sigma(N_i \cdot \log N_i))$  ( $\Sigma$  は  $j = 1, 2, \dots, m$  の総 和,m は配線層数を表す)の手間がかかる.

#### 4. 評価実験

提案手法を C 言語のプログラム ( Perry と呼ぶ ) として , 実現した . 本章では , その評価実験結果を示す . 発生モデルの離散化した異物粒径の種類数 n と発生確率計算精度および実行時間の関係について , 提案手法をいくつかの品種に適用した結果を示し , その有効性を実証する . 実験対象の回路としては , 汎用的な製造方式である 180 nm , 150 nm クラスの製造方式から , 先端の製造方式である 90 nm クラスの製造方式まで , 多種のプロセスに関する事例をあげ , 本手法が幅広いプロセス種に適用可能であることを示す . 表 1 に実験対象の回路の諸元を示す .

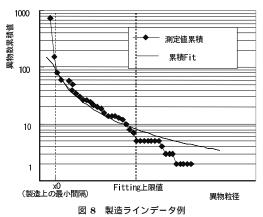

#### 4.1 発生モデル

汎用的な製造方式については製品実績が十分にある 状況であり,ブリッジ故障の発生モデルは従来の歩留 まり予測用モデルを適用可能であったが,先端の製造

表 1 実験対象回路

Table 1  $\,$  The benchmark circuits used in this experiment.

| LSI          | 製造方式             | ネット数       |

|--------------|------------------|------------|

| A            | 180 nm           | 112,288    |

| В            | $150\mathrm{nm}$ | 7,435,415  |

| $^{\rm C}$   | $150\mathrm{nm}$ | 5,339,214  |

| D            | $130\mathrm{nm}$ | 11,098,993 |

| $\mathbf{E}$ | $90\mathrm{nm}$  | 35,051,111 |

Fig. 8 An example of particle count in a production line.

方式については,本論文の実験段階では,まだ十分な 製品実績が積めておらず,製品に先行するテスト用パターンでの評価データを基にモデル化を行った.図8 に評価データからのフィッティングの一例を示すが, 異物粒径ごとの測定値の累積を基にサイズ分布関数のフィッティングを行い,分布関数を求める.当該ステップで要する時間は測定用のテストレイアウトパターンの製造および測定が支配的である.ただし,本工程は従来,歩留まり予測のために実施されてきた工程であり,本手法のために追加実施されるものではないため,本論文では議論の対象としない.

両製造方式の例ともに,異物の発生確率が規定領 域に含まれるサイズ分布として,最小の配線ピッチの 1.25 倍, 1.5 倍, 1.75 倍, 2 倍, 2.5 倍, 3 倍, 4 倍の 7 種のサイズ (n=7) のほかに 5 種 (n=5), 9 種 (n=9), 精度評価の基準として 70 種 (n=70), 比 較的小規模な LSI である A , B についてはさらに速 度評価のために 1,000 種 (n = 1,000) をモデル化の 対象とし,計算精度と計算時間の評価実験を行った. なお,異物欠陥発生確率のモデル化手法上,あらゆる 異物径を考慮した正解値を求めることは非常に困難で あり, また n 値の増加にともない, 精度が改善され ることも自明であるため,適用実験で実行可能な上限 値を選択するという視点で精度評価の基準を選択し、 70 種を選択した、70 種の場合と 1,000 種の場合の結 果比較については A, Bについて, 平均誤差 0.1%以 下を得ており,70種が精度基準として問題ないこと を確認している.

5種 (n=5), 7種 (n=7), 9種 (n=9)のケースの各計算精度については,実適用結果を基に,故障検出率 95%を得ることが可能であった上位 2.5K 組のペアリストを対象とする.基準とする n の値 70 と誤

表 2 モデル数ごとの精度

Table 2 Accuracy's variation by the sampling number n.

| LSI          | 平均誤差 (%) | 平均誤差 (%) | 平均誤差 (%) |

|--------------|----------|----------|----------|

|              | (n = 5)  | (n = 7)  | (n = 9)  |

| A            | 6.17     | 1.30     | 1.18     |

| В            | 0.61     | 0.37     | 0.20     |

| $^{\rm C}$   | 0.76     | 0.22     | 0.13     |

| D            | 1.47     | 0.40     | 0.37     |

| $\mathbf{E}$ | 2.73     | 0.26     | 0.21     |

表 3 Perry 実行時間 (2.8 GHz Opteron サーバ使用) Table 3 The runtime of Perry.

| LSI          | 実行時間    | 実行時間    | 実行時間    | 実行時間     | 実行時間        |

|--------------|---------|---------|---------|----------|-------------|

|              | (sec.)  | (sec.)  | (sec.)  | (sec.)   | (sec.)      |

|              | (n = 5) | (n = 7) | (n = 9) | (n = 70) | (n = 1,000) |

| A            | 7       | 8       | 9       | 77       | 1,082       |

| В            | 1,582   | 1,648   | 1,709   | 13,550   | 171,353     |

| $^{\rm C}$   | 3,090   | 3,175   | 3,267   | 25,713   | 適用不可        |

| D            | 3,703   | 3,808   | 4,068   | 29,326   | 適用不可        |

| $\mathbf{E}$ | 8,583   | 9,180   | 9,823   | 85,225   | 適用不可        |

差比較する n (たとえば , 7) のそれぞれのペアリストの上位  $2.5\mathrm{K}$  組のペアの間で同一ペアのブリッジ故障率の誤差を求めそれらの平均値を n の平均誤差とする . たとえば , n=70 の実行において , 信号 a 信号 b c%という結果を得 , n の実行結果で , 信号 a 信号 b d% という同一ペアがあれば誤差は |c-d|/c であり , そのように求めた誤差を平均したものが n の平均誤差である .

比較結果を表 2 に示す、表 2 に示すとおり,n=5 の場合,n=7 の場合,n=9 の場合の各々の平均 誤差はそれぞれ 6.2%以下,1.3%以下,1.2%以下となる.実運用上は,n=5 の場合で平均誤差が 5%を超えているものを除き,ほぼ問題ない誤差である.

一方,計算時間(CPU TIME)は,表 3 に示すとおり,オーバヘッド部分を除けば,ほぼ n に比例して増大しており,回路規模の増大にともない無視できない差異となっている.以上から平均誤差と処理時間のかねあいを考えて,表 1 の LSI と同等の規模の LSI に対する Perry の適用では n=7 を採用することが適切であると考える.また実運用可能な n 値の存在を確認したことにともない,評価実験により異物径レンジの n 分割離散化の有効性が確認できた.

#### 4.2 近接配線ペアリスト作成

レイアウト情報の抽出は LEF/DEF データと,前 記異物発生確率を入力とし,ブリッジ故障の確率について順位付けを行った近接配線ペアリストを出力する プログラム Perry を適用した.適用対象回路の規模および実行時間を表 1 および表 3 に示す.5M gate 規模の LSI E についても,標準的な適用条件 n=7 で

#### 表 4 従来手法との実行時間比較

Table 4 The comparison of runtime between the proposed method and the existing method.

| 手法             | 故障候補リスト作成までの実行時間 |

|----------------|------------------|

| 小五郎 IDDQ のみ適用  | 2 days           |

| 小五郎 IDDQ+Perry | 3 hours          |

3 hours 弱というように実行時間は小さく十分実用に耐えうる.

#### 4.3 従来手法に対する比較

本手法の今回の適用結果を従来手法と比較し,本手 法の効果を明確化する . LSI B については , 従来手法 として,小五郎 IDDQ と呼ぶ故障解析ツールのみを 使用し, 本手法でのレイアウト情報に基づく近接配線 ペアを使用しなかった際の解析に要した工数と、小五 郎 IDDQ +本手法を適用した場合に解析に要した工 数の 2 種の工数情報が揃っており,表 4 に示す. LSI B の規模でも,1チップの解析に対し,故障解析まで で小五郎 IDDQ のみの適用で2日間の工数を必要と していたものが,本手法 Perry の適用により,3時間 にまで短縮できている.また,出力結果については, 両手法ともに, 想定される全テストベクトル 226K ス テップ中から, 2.5K ステップを抽出し, 故障検出率 95%を実現しており,同等の結果を得ている.故障検 出率の残り5%については,メモリ IP 内部であり小五 郎 IDDQ + Perry の適用対象外である. なお, LSI B で完全に人手による論理調査で故障位置の特定を行っ た際の故障解析に要した工数は20日間であり,この 場合の故障検出率は75%程度であった.また,故障箇 所の解析に要する時間は,対象となるブリッジ故障候 補数が回路規模の2乗に比例するため, LSI E の規模 となった場合,本手法では2日程度で解析が実行でき ているが, Perry なしでの従来手法では, 現実的な工 数では解析不可能である.

#### 5. ま と め

LSI の微細化/大規模化にともない,LSI テストに対して故障検出率の向上と,故障診断時間の削減という相反した要求がなされる.IDDQ テストの故障診断では,テスタのフェイル結果と,故障辞書とを比較することにより実際の故障箇所を推定するが,論理情報の全配線ペアをブリッジ故障の故障候補とすればテスト時間と解析時間が膨大になるという問題がある.

本論文では,レイアウト情報の使用によるブリッジ 故障候補の絞り込みにより診断時間を短縮するための 近接配線ペアリスト生成手法を提案した.生成におい ては,自動配置配線ツールにより作成されるレイアウ トの特徴である等間隔性を利用した離散処理を有効活用することにより,効率的な生成を実現した.また,評価実験から大規模 LSI に対する提案手法の有効性が確認できた.

#### 参考文献

- Higami, Y., Takamatsu, Y., Saluja, K. and Kinoshita, K.: Fault Models and Test Generation for IDDQ Testing, Asia and South Pacific Design Automation Conference, pp.509– 514 (2000).

- Nigh, P., Forlenza, D. and Motika, F.: Application and Analysis of IDDQ Diagnostic Software, *International Test Conference*, pp.319–327 (1997).

- 3) Sanada, M.: A CAD-based Approach to Failure Diagnosis of CMOS LSI's Using Abnormal Iddq, *VLSI Test Symposium*, pp.186–191 (1996).

- 4) Stanojevic, Z., Balachandran, H., Walker, D., Lakbani, F., Jandhyala, S., Saxena, J. and Butler, K.: Computer-aided Fault to Defect Mapping (CAFDM) for Defect Diagnosis, *International Test Conference*, pp.729–738 (2000).

- 5) 野津山,本田,山口,中西:レイアウト情報を 反映するテスト品質評価・向上手法,信学技報, Vol.ICD2002-197, pp.1-6 (2003).

- 6) 藤本 , 四柳 , 橋爪 , 為永 : レイアウト情報を用いた故障候補エリアの抽出 , 情報処理学会研究報告 , Vol.SLDM117-26, pp.149-154 (2004).

- 7) Krishnaswamy, V., et al.: A Study of Bridging Defect Probabilities on a Pentium 4 CPU, *International Test Conference*, pp.688–694 (2001).

- 8) Shen, W.J.P. and Ferguson, F.J.: Inductive Fault Analysis of MOS Integrated Circuits, *IEEE design & test of computers*, Vol.2, No.6, pp.13–26 (1985).

- 9) 山中, 佐藤, 池田, 山崎, 小林, 高倉: 欠陥 ベース故障診断手法, 情報処理学会研究報告, Vol.SLDM100-5, pp.33-40 (2001).

- 10) 山中, 佐藤, 山崎, 高倉: DSM プロセスの総合 的故障診断手法, DA シンポジウム 2003 論文集, pp.283-288 (2003).

- 11) Sdrick, R.: An Engineer's Practical Guide to Drop Size, Spraying Systems Co. (1997).

- 12) Hsiao, P. and Feng, W.: Using a Multiple Storage Quad Tree on a Hierarchical VLSI Compaction Scheme, *IEEE Trans. CAD of IC and Systems*, Vol.9, No.5, pp.522–536 (1990).

(平成 18 年 9 月 15 日受付) (平成 19 年 2 月 1 日採録)

# 術統括部勤務.

#### 伊藤 俊明(正会員)

平成3年京都大学工学部情報工学 科卒業.同年三菱電機(株)入社. 以来,LSIの物理設計・検証技術の 研究開発に従事.現在,(株)ルネ サステクノロジ製品技術本部設計技

# 金本 俊幾(正会員)

在,(株)ルネサステクノロジ製品技術本部設計技術 統括部勤務.博士(情報科学)(大阪大学).電子情報 通信学会会員.

### 小谷 憲

サステクノロジ製品技術本部設計技術統括部勤務.

#### 清水 良浩

平成4年東京理科大学理工学部数学科卒業.同年(株)日立製作所入社.以来,LSIのテスト容易化設計技術の開発に従事.現在,(株)ルネサステクノロジ製品技術本部設計

技術統括部勤務.

#### 寺井 正幸(正会員)

1976 年大阪大学工学部電子工学 科卒業 . 1978 年同大学大学院工学 研究科博士前期課程修了 . 同年三菱 電機(株)入社 . 以来, LSI の CAD の研究開発に従事 . 2003 年(株)ル

ネサステクノロジへ転籍 . 2005 年大阪学院大学情報 学部教授 . 工学博士 . 電子情報通信学会会員 .