# 低消費電力アクセラレータ Cool Mega-Array(CMA)-2の実チップ評価

# 伊澤麻衣 小崎信明 安田好宏 木村優之 天野英晴

Cool Mega-Array (CMA) は,近年要求が高まる高性能低電力アクセラレータのための新しいアーキテクチャである.CMA は大きな組み合わせ回路から成る演算素子 (PE) アレイ,データアクセスを制御する小規模な  $\mu$  コントローラ及びデータメモリから構成される.PE アレイに DVFS やウェーブバイブラインを適用し, $\mu$  コントローラによってアレイからの演算結果を集約するタイミングを制御することで,高いエネルギー効率を実現する.最初のブロトタイプである CMA-1 は 65nm CMOS process を用いて実装した.CMA-1 はアレイサイズ 8×8 で設計され,実チップでは高いエネルギー効率を達成した.この CMA-1 はアレイサイズ 8×8 で設計され,実チップでは高いエネルギー効率を達成した.この CMA-1 を改良し,より高い性能とエネルギー効率を達成することを目指して,CMA-2 を 40nm CMOS process を用いて開発した.CMA-2 はアレイサイズを 10×8 に拡張し,また, $\mu$  コントローラをパイプライン化すると共に,命令メモリの容量を倍にした.更に,PLL を搭載することにより,I/O と  $\mu$  コントローラの周波数を分離し, $\mu$  コントローラにより高周波数のクロックを安定して供給できるようにしている.実チップでの評価の結果,CMA-2 はレイアウト上の問題が大きく,最大エネルギー効率は CMA-1 に及ばなかったが,sepia filter では 6.9% の電力効率の向上を達成した.

# Real Chip Evaluation of a Low-Power Accelerator Cool Mega-Array(CMA)-2

MAI IZAWA,† NOBUAKI OZAKI,† YOSHIHIRO YASUDA,† MASAYUKI KIMURA† and HIDEHARU AMANO†

Cool Mega-Array or CMA is a novel high performance but low power accelerator architecture for battery driven mobile devices. CMA is consisting of a large PE array with pure combinatorial logic, a small  $\mu$ -controller to keep flexibility of data management, and data memory. CMA is able to achieve high energy efficiency by appling DVFS and wave-pipeline to the PE array. The first prototype CMA-1 with 8×8 PE array was implemented with 65 nm CMOS process, and achieved a high degree of energy efficiency. To achieve higher performance and energy efficiency, the second prototype CMA-2 with 10×8 PE array was implemented with 40nm CMOS process. The depth of instruction memory was doubled, and  $\mu$  controller was pipelined. PLL was introduced to separate the system clock from I/O clock, and the  $\mu$  controller can work with a higher clock generated from PLL. The evaluation result with real chip shows that the power efficiency of CMA-2 is 6.9% higher than that of CMA-1 with sepia filter.

# 1. はじめに

近年,バッテリーで駆動するモバイル機器に搭載するため,低電力かつ高性能なオフロードエンジンの要求が高まっている。このためのアーキテクチャとして粗粒度な動的リコンフィギャラブルプロセッサ (Dynamically Reconfigurable Processor Array,DRPA) $^{1)}$ が注目されている。DRPA は対象アプリケーションを直接的な形で PE (Processing Element) アレイ上にマッピング可能であり,命令フェッチ等の余分な電力が少なく,低い動作周波数で高い性能を得ることができる。NEC の STP エンジン $^{2}$ ,IMEC の ADRES $^{3}$

Faculty of science and Technology, Keio University

などが既に商用化されている.

しかし、従来のリコンフィギャラブルプロセッサは データパスの再構成やクロックの分配に要する電力に まだ節約の余地がある。さらに、構成を切り替える ごとに変化するデータパスの最大遅延の違いもエネル ギー効率の改善に利用可能である。

我々は、DRPAのエネルギー効率を改善した新たなアーキテクチャとして、CMA (Cool Mega-Array)<sup>4)</sup>を提案した。CMA は、大規模な組みあわせ回路から成る PE アレイを持ち、動的再構成を行わないことで再構成にかかる電力を削減し、マッピングされたアプリケーションに応じた遅延で結果を格納することでエネルギー効率を改善している。再構成を行わないことによる柔軟性の低下は、小規模な μ コントローラによ

<sup>†</sup> 慶應義塾大学理工学部

りメモリからのデータの読み書きを柔軟に行うことで 補うことができる。PEアレイは、内部にレジスタを 持たないため、遅延時間に余裕がある場合は、レジス タのセットアップ時間やホールド時間等を気にせずに PEアレイの供給電圧を下げて、必要性能に応じたエ ネルギーでアプリケーションを実行可能である。さら に、PEアレイにはクロックツリーが不要であり、ク ロック分配に要する電力を削減している。

我々は、CMA の最初のプロトタイプとして 65nm プロセスを用いてアレイサイズ  $8\times 8$  の CMA-1 を開発した。CMA-1 は高いエネルギー効率を達成することができた。この実装経験に基づき、よりプログラミングが容易で、高い性能とエネルギー効率の達成を目指した CMA-2 を開発した。CMA-2 は、40nm プロセスを利用し、アレイサイズを  $10\times 8$  に拡張するなど、いくつかの改良を行った。本報告では、CMA-2 の設計、実装と実チップを用いた評価を述べる。

#### 2. CMA-1 の概要

ここでは CMA-1 を簡単に紹介する。CMA の基本構成と CMA-1 についての詳細は文献 $^4$ )を参照されたい。CMA-1 は CMA の最初のプロトタイプとして、e-shuttle 65nm プロセスを利用して開発された。CMA-1 は  $8\times 8$  サイズの PE アレイ、 $\mu$  コントローラ及びデータメモリ (DMEM) で構成される。PE アレイは組み合わせ回路のみで構成されている。PE は、24 ビット幅のデータを扱い、その構成情報は コントローラによってアプリケーション実行前にセットされ、実行中は基本的には変更されない。

$\mu$  コントローラは外部より与えられた簡単なプログラムによって制御され、PE アレイと DMEM 間のデータアクセスの制御を行う.  $\mu$  コントローラ内部には、プログラムの命令を格納するため、14 ビット 64 エントリの命令メモリが設けられている。

CMA-1 は、動的リコンフィギャラブルアクセラレー タをはるかに越えるエネルギー効率である 243 MOPS / mW を達成し、様々なアプリケーションを実装して電流を評価することが可能であり、最初のプロトタイプとしては十分な役割を果たした.

#### 3. CMA-2

本章では、CMA-2 の構成と CMA-1 に対する改善 点について述べる。

# **3.1** CMA-2 における改善点

CMA-2 は CMA-1 を改良し、より高い性能とエネルギー効率を達成することとアプリケーションの搭載を容易にすること、また、実際に CPU と組みあわせてアクセラレータとして利用可能なチップを目指して開発された。

主な改善点は以下の通りである.

- PE アレイのサイズを  $10 \times 8$  に拡張した. これに より, 並列性を高くして性能の向上を図っている.

- ▼プリケーションの搭載を容易にするため、定数 レジスタと命令メモリを増強した。

- $\mu$  コントローラをパイプライン化して、性能の改善と、エネルギー効率の向上を図った.

- PLL を搭載し、入出力用のクロックと内部動作のためのクロックを分離した。これにより、外部にホスト CPU を接続して実際にアクセラレータとして利用することが可能になった。

# 3.2 PE アレイ

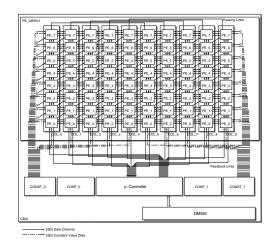

CMA-2 の構成を図 1 に示す。CMA-1 同様,CMA-2 は PE アレイ, $\mu$  コントローラ及びデータメモリ (DMEM) で構成される。

CMA-2 は  $10 \times 8$  の PE によるアレイ構造を持つ. PE は、CMA-1 同様に、マルチメディア処理を対象としているため、24 ビット幅のデータを扱うようになっている。アレイは図 1 に示すように配置され、組み合わせ回路で構成される。

CMA-1 はチップの面積の限界からアレイサイズを  $8\times 8$  としたが、元々の CMA の構想は、大規模な アレイを用意することで、並列性を利用して必要な性 能を実現することにあった。これには 64PE は必ずし も十分ではない。そこで、CMA-2 では、PE アレイ を拡張することで、並列性を向上させ、性能の向上を 図った。当初、アレイサイズは  $12\times 8$  に拡張することを目指したが、レイアウト時間とレイアウトに必要 なデータ量の制約により、結局  $10\times 8$  となった。

# 3.3 定数値レジスタ

CMA-1 では、PE アレイに供給する定数は 16 ビット、16 エントリであったが、アプリケーションによっては不足したため、プログラミングが難しくなった.

そこで、CMA-2 では、定数の bit 幅を PE のデータ 幅と同じ 24 ビットに拡張し、エントリ数も 26 エントリに増強した。定数は図 1 に示す通りに外部のレジスタより PE アレイへ接続される。

#### 3.4 $\mu$ コントローラ

#### **3.4.1** $\mu$ コントローラの動作

$\mu$  コントローラは、命令メモリ中のマイクロコード により、DMEM 上のデータを PE アレイに転送し、また、PE アレイからの演算結果を DMEM に格納するための制御を行う.

$\mu$  コントローラは、コントローラ本体、Fetch レジ スタ, Launch レジスタ, Gather レジスタから構成さ れる.  $\mu$  コントローラは、まず、データメモリから順 に値を読み出して、Fetch レジスタに格納する. PE ア レイへの入力データが全て揃ったら、これを Launch レジスタに移動し、PE アレイは、この入力データに 基づき演算を開始する. μ コントローラは, 一定時間 が経過した後に、PE アレイ上の演算結果を Gather レジスタに格納する、この時間は、対象のアプリケー ションと PE アレイに与える電圧に依存して決まり, プログラマが適切な値に設定する必要がある.次に Gather レジスタに入っている結果を、順番にデータ メモリに格納する. Fetch レジスタへの転送は、それ ぞれの入力に対応したアドレスレジスタを利用して, 任意のアドレスからの転送が可能である. また, ビッ トマップを用いたブロック転送,ストライド転送も可 能である. Gather レジスタからメモリへの転送も. ブ ロック転送が可能である.

(1) データメモリから Fetch レジスタヘデータを分 配, (2) PE アレイ上で演算, (3) Gather レジスタか らデータメモリへの書き戻しの三ステップは、パイプ ライン的に実行され,これによって処理性能の向上を 図っている. (1) (2) (3) のパイプライン処理を効率良 く行うためには、それぞれの時間を同じ程度にし、バ ランスを良くする必要がある. PE アレイ上の演算処 理が早く終了する場合は、アレイの供給電圧を下げる ことで、性能に影響を与えることなく演算で消費され る電力を削減することができ, エネルギー効率を向上 させることができる. 逆に PE アレイの遅延時間が長 い場合, μ コントローラの動作周波数を下げることで 処理時間のバランスを取るが、PE アレイにおける演 算時間が十分に長い場合には, 現在の結果データを回 収する前に、次の入力データを Launch レジスタに転 送して処理をスタートしてしまう, Wave Pipeline を 適用することで性能を改善することができる.

# **3.4.2** *µ* コントローラの改良

CMA-1 にアプリケーションを載せ、評価をとったところ、 $\mu$  コントローラが PE アレイの入力にデータをセットアップする時間よりも PE アレイでの演算

時間の方が高速であることがわかった。このような場合は、PE アレイの電圧を下げることで、性能を下げずにエネルギー効率を向上させることができる。しかし、CMA-2 では、 $\mu$  コントローラを改善して性能を向上させることを目指した。

$\mu$  コントローラは,プログラム格納型の簡単なプロセッサであるが,CMA-1 ではシングルサイクルで設計されているため,動作周波数が制限されている.そこで CMA-2 では, $\mu$  コントローラを Instruction Fecth Stage と Execution Stage の 2 ステージにパイプライン化し,性能の向上を図った.

また、CMA-1 の  $\mu$  コントローラは、マイクロ命令メモリをレジスタを用いて構成したため、エントリが64 に制限されると共に、電力消費も大きかった。そこで、CMA-2 では専用の IP のメモリに変更し、エントリ数を 64 エントリから倍の 128 エントリに増強した。

#### 3.5 データメモリ

データメモリ (DMEM) の構成は CMA-2 は CMA-1 と同じで、2つのバンクより構成され、各バンクは、25 ビット × 1024 エントリである。2つのバンクのうち、片方は PE アレイと接続されており、もう片方は外部と接続される。外部から与えられる信号によって接続は動的に切り替えられる。これにより、CMA-2 がアブリケーションを実行している間、外部と接続された方のバンクとデータの入出力が可能となり、データ転送時間の隠蔽ができるようになっている。

#### 3.6 I/O とシステムクロックの分離

CMA-1では、I/O クロックと内部のシステムクロックが分離していなかった。そのため、データ入出力と実行で外部からの周波数を切り替える必要があり、これらを同時に実行することができなかった。つまり、CMA-1は、I/O バッファとパッケージが高い周波数に対応していないことから、データを直接入出力する場合、100MHz が限界であるが、供給するクロックは波形を調整することにより、210MHz まで入力することができる。そのため、CMA-1の測定には以下の方法を用いていた。(1) クロック周波数 100MHz で命令、データを入力する。(2) クロック周波数を210MHz に上げてから、実行を開始する。(3) 実行終了を確認してから周波数を100MHz に下げて、メモリの内容を外部メモリに書き戻して結果を確認する。

このような方法では、操作が繁雑で時間を要する上、データを入出力しながら実際の動作に近い環境での評価ができない。さらに実際に CPU と接続してアクセラレータとして動作させる場合、動作周波数が制限されるなどの問題があった。そのため、CMA-2では PLL を導入することで、I/O クロックとシステムクロックを分離し、実際に CPU と接続してアクセラ

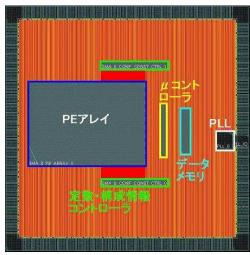

図 2 全体のレイアウト Fig. 2 Layout

レータとして利用することができるようにした.

CMA-2 では、チップ外部から与えられる低周波数の I/O クロックにより、PLL を用いてチップ内部で利用するシステムクロックを生成する。システムクロックと I/O クロックの比率は、PLL に与えるパラメータによって制御され、I/O クロックの 1 倍 (PLL off) から 5 倍まで設定できる。

#### 3.7 チップ実装

CMA-2 は、Renesas 40nm CMOS プロセスの 1 区画 (4mm × 4mm) に実装された。合成には Synopsys 社の Design Compiler 2009。06-SP5 を、配置配線には Cadence 社の SOC Encounter 9.1 を用いた。CMA-2 のレイアウトを図 2 に示す。当初は半区画に実装される予定であったが、パッケージの制約により 1 区画に変更されたため、まだ面積に相当の余裕がある。しかし、実装時間とレイアウトに要するデータ量の制約により、これ以上 PE アレイのサイズを大きくすることができなかった。

また、CMA-2では定数値レジスタと構成情報レジスタをそれぞれ二つに分割して設計した。これは、PEアレイが左右に拡張されたため、一つのレジスタファイルから PEアレイの左右に配線を引くと、配線量が多くなり、消費電力や面積性能が低下してしまう。そのため、レジスタファイルを二つに分割し、PEアレイの横に配置することで、配線量を減らしている。

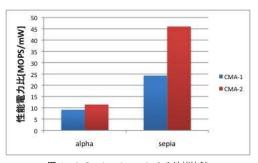

CMA-2 は  $\mu$  コントローラのパイプライン化によりシステムクロック 300MHz で動作するように設計されている。図 3 にシミュレーションにおける CMA-1 と CMA-2 の評価結果を示す。図はどちらも周波数 167MHz で動作させた場合の電力性能比を示している。この図から,CMA-2 では CMA-1 よりも電力を

図 3 シミュレーションによる性能比較 Fig. 3 Compared with CMA-1 on simulation

表 1 CMA-1 と CMA-2 の仕様 Table 1 Specifications

|                    | CMA-1                                         | CMA-2                                         |

|--------------------|-----------------------------------------------|-----------------------------------------------|

| Technology         | Fujitsu e-shuttle<br>65nm 12-metal CMOS       | Renesas 40nm<br>7-metal CMOS                  |

| Chip Area          | $2.1 \text{mm} \times 4.2 \text{mm chip}$     | $4.2 \text{mm} \times 4.2 \text{mm}$ chip     |

| Core Area          | $1.5 \mathrm{mm} \times 3.6 \mathrm{mm}$ core | $3.5 \mathrm{mm} \times 3.5 \mathrm{mm}$ core |

| Supply Voltage     | 0.45-1.2 V for<br>PE array (VDDL)             | 0.7-1.1 V for<br>PE array (VDDL)              |

| PE Array           | 8 × 8                                         | 10 × 8                                        |

| $\mu$ -controller  | 1 cycle non-pipelined                         | 2 stage pipeline                              |

| Instruction memory | 14 bit - 64 depth                             | 14 bit - 128 depth                            |

| Clock frequency    | $210 \mathrm{MHz}$                            | $180 \mathrm{MHz}$                            |

削減することができ、大きくエネルギー効率を向上させることができるはずであった.

しかし、CMA-2では、実装上の問題から目標の一部である、 $\mu$  コントローラの性能向上と、絶対性能の改善は実現することができなかった。CMA-1と CMA-2の仕様を表 1 に示す。

まず,動作周波数は目標の300MHzから180MHz まで低下した. これは、Gather レジスタから DMEM までの配線遅延と、メモリの書き込みタイミングの制約 から来ており、レイアウトの変更で改善可能であった. このため、最大性能は現在の所、CMA-1を上回るに 至っていない. さらに, コンパクトにレイアウトできた PEアレイが予想よりも電力を消費しなかった割に、配 線遅延と容量負荷の大きかった Fetch,Launch,Gather レジスタ,メモリ間が予想以上の電力を消費し,μコ ントローラの電力が PE アレイをさらに上回るよう になった. この CMA-2 の実装上の問題は, Renesas 40nmプロセスの性能に起因するものではなく, 我々の レイアウト能力の未熟さによる. 特に, Renesas 40nm プロセスの設計が、メタル埋めを設計者側で行うため に、レイアウトのデータ量が途中から膨大な大きさと なり、我々の計算資源では扱い切れなくなったことが 大きい. このため、最終的に謝辞に挙げた内藤電誠に お世話になりようやくテープアウトすることができた. 今回は,性能向上のために,レイアウトのチューニン グを行う余裕はまったくなく, これが最大動作周波数

表**2** アプリケーションプログラム Table 2 Applications Plograms

|  | af    | 24-bit $\alpha$ - Blender |  |

|--|-------|---------------------------|--|

|  | sf    | 24-bit sepia filter       |  |

|  | alpha | 8-bit $\alpha$ - Blender  |  |

|  | sepia | 8-bit sepia filter        |  |

|  | edge  | edge filter               |  |

|  | gray  | 24-bit gray scale         |  |

を上げることができなかった主原因である.

# 4. 評 価

本節では、CMA-2 の実チップにおける評価結果を示し、また、CMA-1 と性能電力比を比較した結果を示す。

評価に用いたアプリケーションプログラムを表 2 に示す. 8-bit のアプリケーションは,データは RGB の各素子ごとの 8 ビット単位でメモリに格納されていることを想定しているが, 24-bit のアプリケーションでは,1 ピクセルごとの 24 ビット単位で格納されているデータを扱っている.

CMA では、データメモリからデータを読み出して PE アレイに転送し、PE アレイでの演算結果を集約してデータメモリに書き戻す操作を  $\mu$  コントローラで制御している。しかし、先に述べたように CMA-2 は、特に  $\mu$  コントローラからデータメモリに書き戻す際の遅延が大きかったため、今回は PE アレイの演算結果を  $\mu$  コントローラ内部で一時的に格納する Gather レジスタの値を確認することで評価を行った。

#### 4.1 実機評価結果

CMA-2 において、アプリケーションを載せ、アレイの電圧を変化させた場合の消費電力と性能の評価結果を示す.

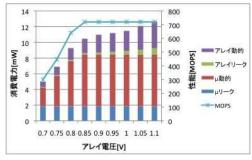

評価結果の例として、sepia を実行したときの消費電力の評価結果を図 4 に示す。この図は、横軸がアレイの供給電圧、縦の主軸が棒グラフで消費電力を示しており、第 2 軸が性能を示している。性能の単位はMOPS (million operation per second) であり、単位時間の処理性能となっている。これは  $\mu$  コントローラの動作周波数に比例している。

アレイ電圧 0.85 V 以上の時にはアレイにおける演算時間が短く, $\mu$  コントローラがボトルネックとなっている。この時の  $\mu$  コントローラの動作周波数は 180 MHz であった。アレイの供給電圧がそれより低い場合には,アレイでの演算時間に合わせて  $\mu$  コントローラの動作周波数を下げている。そのため,性能と消費電力共に減少している。

電力の内訳を見ると、棒グラフの赤い部分で示して ある  $\mu$  コントローラの動的電力の割合が高くなって おり、50% 以上を占めている.  $\mu$  コントローラにおける消費電力は、動作周波数とメモリへのアクセス頻度

図4 sepia filter の評価結果 Fig. 4 Evaluation (sepia filter)

に依存し、アレイの使用率や演算の種類には依存しない。評価したアプリケーション全ての平均を取ると、動作周波数 180 MHz で動作させた時の  $\mu$  コントローラでの消費電力は約 8.47 mW であった。次に PE アレイにおける消費電力を見る。アレイのリーク電力は供給電圧 1.1~V の時 0.835~mW と小さい。 PE アレイの動的電力は、動作周波数と PE アレイの使用率や演算の種類に依存する。評価したアプリケーション全ての平均を取ると、動作周波数 180~mHz,供給電圧 1.1~V で動作させた時の PE アレイでの消費電力は約 6.11~mW であった。

CMA-2 では、 $\mu$  コントローラにおける消費電力と性能を改善することを目的としていたが、実チップの評価では、これらの改善を図ることができなかったことが明かになった。これは先に述べたように、レイウアトの改善により解決可能な問題であると考えられる。

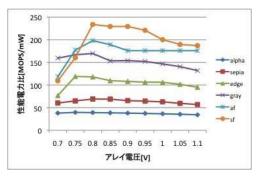

それぞれのアプリケーションプログラムにおいて、性能を電力で正規化したグラフを図 5 に示す. 供給電圧を下げた場合、基本的には PE アレイでの演算時間に合わせて  $\mu$  コントローラの動作周波数を下げるが、データパスの長いアプリケーション ( edge, gray, af, sf ) では、低いアレイ電圧の時にはウェーブパイプラインを適用し、これによって電圧の低い領域における性能の急激な悪化を防ぎ、性能向上を図っている.ウェーブパイプラインを適用した範囲は、edge, grayでは 0.8~V 以下、af では 0.85~V 以下,sf では 0.95~V 以下である.

alpha や sepia のように比較的データパスが短く、また、メモリからのデータのロード 回数が多いアプリケーションでは、性能電力比は alpha で最大 39.5 MOPS / mW, sepia で最大 69.1 MOPS / mW とあまり高くない。対して、af や sf のように、データパスを長くして PE の使用数を増やし、また、メモリからのデータのロード 回数を減らして設計されたアプリケーションでは、性能電力比は、af で最大 198.0 MOPS / mW, sf で最大 233.7 MOPS / mW と高いエネルギー効率を達成した。CMA-2 にアプリケー

図 5 性能電力比 Fig. 5 Energy efficiency

図 6 CMA-1 との比較結果 Fig. 6 Compared with CMA-1

ションを載せ評価を取った結果,最もエネルギー効率 が良かったのは sf を実行した時であり,233.7 MOPS / mW を達成した.

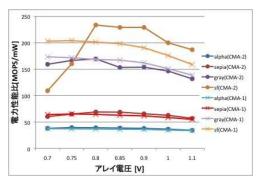

#### 4.2 CMA-1 との比較

CMA-1 は 210MHz で動作するが、CMA-2 の最大 動作周波数は 180MHz であり、 $\mu$  コントローラの絶対 性能を改善することはできなかった. CMA-1と CMA-2のエネルギー効率の比較結果を図6に示す. CMA-2 は CMA-1 と比較して alpha では 4.1%, sepia では 6.9% のエネルギー効率の向上が見られた. しかし, gray のように CMA-1 の方が CMA-2 よりもエネ ルギー効率が高くなるものもあった。また、CMA-1 の最大エネルギー効率は 243 MOPS / mW であり, CMA-2 の 233.7 MOPS / mW よりも大きい。alpha や sepia は PE の使用率が CMA-1 と同じになるよ うに並列性を高めることができたが, 並列性を高めら れず CMA-1 と同じデータ数しか処理できないアプリ ケーションではエネルギー効率を高めることができな かった. PE アレイのサイズが 12 × 8 であれば使用 率をもっと高めたアプリケーションを載せることがで き,エネルギー効率を高めることができたのではない かと考えられる.

また, CMA-2 では, アレイの供給電圧を下げてい

くと、CMA-1 よりも早くエネルギー効率が下がっている。これは、アレイの供給電圧を下げたことでアレイでの遅延が延び、性能が下がったことが原因である。これは、CMA-2 は CMA-1 と比較して、PE アレイの配線遅延が長くなったためと考えられる。

# 5. 結 論

本研究では、CMA-1を改良した低消費電力アクセラレータ CMA-2を設計、開発し、その実装方法と実チップによる評価結果を報告した。CMA-2はレイアウト上の問題が大きく、CMA-1と比較して絶対性能と最大エネルギー効率を改善することができなかった。しかし、いくつかのアプリケーションではエネルギー効率を向上させることができ、 $\alpha$ -Blenderで4.1%、sepia filterで6.9%の性能向上が見られた。

今回 CMA-2 は、VDEC で大学が設計実装した Renesas 40nm では始めてのケースであり、内藤電誠の力を借りてテープアウトをするのがやっとであった。 CMA-2 の問題は次に実装しなおせば、ほとんどが解決可能と考えられる。一方で、PE アレイのサイズを大きくし、 $\mu$ コントローラの動作周波数を上げるという CMA-2 の方向性については、どの範囲まで行うべきかを、実際の設計データを踏まえて検討する必要がある。PE アレイのサイズをある程度に抑えて、CMAのマルチコア化を図るのも、もう一つの方向性と考えられる。

#### 謝 辞

本チップ試作は東京大学大規模集積システム設計教育研究センターを通し、株式会社半導体理工学研究センター、ルネサスエレクトロニクスおよび内藤電誠の協力で行われた。関係者各位に深く感謝する.

#### 参考文献

- 1) H.Amano, et.al: "Muccra chips: Configurable dynamically-reconfigurable processors", Proc. of ASSCC, pp. 384–387 (2007).

- M. Motomura: "STP Engine, a C-based Programmable HW Core featuring Massively Parallel and Reconfigurable PE Array:its Architecture, Tool, and System Implications", Prof. of CoolChips XII. (2009).

- F.J.Veradas, et.al: "Custom implementation of the coarse-grained reconfigurable adres architecture for multimedia purposes", Proc. of International Conference on Field Programmable Logic and Applications (FPL05), pp. 106–111 (2005).

- N.Ozaki, et.al. "SLD-1(Silent Large Datapath): A ultra low power reconfigurable accelerator", Cool Chips XIV, IEEE, 2011.