# カーボンナノチューブトランジスタを用いて論理合成した プロセッサの電力/面積/回路遅延評価

概要:カーボンナノチューブトランジスタ(CNFET)はシリコントランジスタ(Si-MOSFET)と比較して高速かつ低消費電力に動作する。そのため,CNFET を用いてプロセッサを実装した場合,トランジスタと配線の間の遅延と電力のバランスが大きく変化し,プロセッサのアーキテクチャが大きく変わる可能性がある。CNFET を用いたプロセッサのアーキテクチャを検討するためには個々のユニットレベルの評価が必要だが,これまではプロセッサ全体レベルの評価しか行われていなかった。そこで本稿では,我々が開発した CNFET セルライブラリを用いてプロセッサの論理合成を行い,CNFET を用いたプロセッサの各ユニットの電力/面積/回路遅延を評価する。評価の結果,CNFET 7nm および 5nm セルライブラリを用いた場合,Si-MOSFET のセルライブラリである NanGate 15nm オープンセルライブラリを用いた場合と比較して,OpenSPARC T2 プロセッサのユニットごとの消費電力を最大 96.7%,回路面積を最大 58.4%,回路遅延を最大 87.7%削減できることがわかった.

キーワード: CNFET, OpenSPARC T2, 論理合成

## 1. はじめに

現在のプロセッサはシリコントランジスタ(Silicon Metal Oxide Semiconductor Field Effect Transistor. 以下 Si-MOSFET とする)により構成されており、Si-MOSFET の微細化と共にその性能を向上させてきた. しかし、Si-MOSFET の微細化は限界を迎えつつあることから、プロセッサの性能向上も近い将来に頭打ちになると予想されている [2]. プロセッサが今後も半導体製造技術の進歩による性能向上の恩恵を受けるためには、Si 以外の半導体素子を用いたトランジスタが必要とされている [6].

Si-MOSFET を将来代替すると期待されている半導体素子の1つにカーボンナノチューブトランジスタ(Carbon Nanotube Field Effect Transistor. 以下 CNFET とする)がある [9], [12]. CNFET は FET のチャネル部分にカーボンナノチューブ(Carbon Nanotube. 以下 CNT とする)を使用したトランジスタである. CNT はシリコンと比較して電子/正孔の移動度が 2 桁程高いことから,CNFET は

低い電源電圧で高速にスイッチングできる. 具体的には、 CNFET は Si-MOSFET の数分の 1 の消費電力で数倍高速 に動作することが報告されている [9].

このような背景から CNFET を用いたプロセッサ(以下 CNFET プロセッサとする) の早期実用化が期待されてお り、これまでに実験室レベルで CNFET プロセッサを実現 した例がいくつか報告されている [4], [5]. しかしながら, これまでの研究事例では CNFET プロセッサ全体の動作 速度と消費電力のみが報告されており、プロセッサの内部 アーキテクチャに踏み込んで CNFET 化の効果を詳細に分 析した事例はない. 特に CNFET は高速かつ低消費電力な スイッチング動作が可能なため、CNFET を用いて製造し た回路においてはトランジスタと配線の間の遅延/電力バ ランスが従来とは大きく異なることが予想される. それに よってプロセッサ内のユニット間の遅延/電力バランスが 大きく変化し、Si-MOSFET 向けに最適化されてきた従来 のアーキテクチャが CNFET プロセッサでは最適ではなく なり、アーキテクチャの大幅な見直しが必要になる可能性 がある.

そこで本稿では、Si-MOSFET と CNFET それぞれを用いてプロセッサの論理合成を行い、トランジスタの CNFET 化がプロセッサ内の各ユニットの電力/面積/回路遅延に与える影響を分析する。論理合成に必要なスタンダードセル

<sup>1</sup> 電気通信大学

<sup>1-5-1,</sup> Chofugaoka, Chofu, Tokyo 182–8585, Japan

<sup>2</sup> 株式会社ロジック・リサーチ

<sup>3-8-33,</sup> Momochi, Sagaraku, Fukuoka 814-0001, Japan

<sup>3</sup> 東京大学

<sup>7-3-1,</sup> Hongo, Bunkyoku, Tokyo 113–8656, Japan

a) sasaki@hpc.is.uec.ac.jp

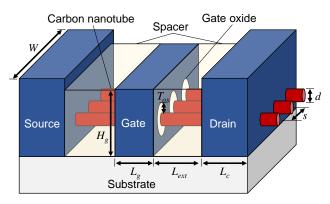

図 1: VS-CNFET

ライブラリは、Si-MOSFET に関してはいくつかのオープンセルライブラリ [1]、[8]、[11] が存在するが、CNFET に関しては我々の知る限りにおいてオープンセルライブラリが存在しない.そこで我々は、CNFET のトランジスタモデルや論文データなどの公開情報を元に CNFET の SPICE モデルを独自に作成し、作成した SPICE モデルを元に CNFET のセルライブラリを新たに開発した.そして、この開発したライブラリを用いて OpenSPARC T2 プロセッサの論理合成を行い、CNFET 化された OpenSPARC T2 プロセッサの電力/面積/回路遅延を評価した.

以下,本稿の章構成を述べる.まず次章では,研究背景として CNFET について詳しく説明した後,CNFET プロセッサに関する先行研究を紹介する.続く 3章では,今回開発した CNFET セルライブラリの概要を述べる.そして,4章で評価方法を説明し,5章で評価結果を示す.最後 6章で本稿をまとめる.

# 2. 研究背景

#### 2.1 **CNFET**

LSI は Si-MOSFET を微細化することで消費電力を削減しつつ動作速度を向上させてきた.しかし、Si-MOSFET のサイズがナノメートルオーダにまで縮小したことにより、リーク電流の増加が深刻な問題となっている.リーク電流を抑制するためには一般に Si-MOSFET の閾値電圧を高くする必要があるが、閾値電圧の上昇はスイッチング速度の低下を招くため、近年は微細化による消費電力削減とスイッチング速度向上の両立が困難となっている.

この問題を解決するデバイスとして、FET のチャネル部分に CNT を使用した CNFET の開発が進められている [9], [12]. これまでにさまざまな構造の CNFET が開発されているが、一例として 5nm ノードまでの微細化が期待されている VS-CNFET (Virtual Source CNFET) [13] を図 1 に示す. VS-CNFET では、図に示すように、ゲート/ソース/ドレインの各電極を貫通する形で数 nm 級の CNTが等間隔に形成される. ゲートに電圧を加えるとソースとドレイン間が導通し、CNT 内を電流が流れる.

CNFET の特徴の1つとして、消費電力が非常に小さいことが挙げられる。例えば VS-CNFET の駆動に必要な電圧は0.4V 前後とされており [4]、FinFET の駆動に必要な電圧の半分程度である。CMOS 回路の動的消費電力は電源電圧の2乗に、静的消費電力は電源電圧に比例するため、CNFET の電源電圧が小さいことは回路の省電力化に大きく寄与する。

また、CNT は正孔と電子の移動度が等しく、その移動度 がシリコンよりも 2 桁以上高い、そのため、Si-MOSFET から CNFET に変更することでトランジスタのスイッチン グ速度が向上し、回路の高速動作が可能になる.

一方, CNFET は Si-MOSFET と比較してゲート遅延を 大幅に削減できるため、回路内のゲート遅延と配線遅延の 比が逆転し、配線遅延が支配的なユニットがクリティカル になると予想される。その結果、CNFET プロセッサはシ リコンプロセッサと異なるアーキテクチャが必要になる可 能性がある。また、トランジスタの CNFET 化により回路 の消費電力や面積も大きく変化し、ユニット間の消費電力 や回路面積のバランスも大きく変化する可能性がある。

# 2.2 CNFET プロセッサ

2013 年に Shulaker ら [10] によって 1kHz で動作する世界初の CNFET プロセッサが開発されて以来,より高性能な CNFET プロセッサを実現するためにさまざまな研究が行われてきた.以下では,CNFET プロセッサの最新の研究事例をまとめる.

文献 [4] では、5nm および 7nm ノードの CNFET を用 いて OpenSPARC T2 プロセッサの論理合成と配置配線を 行い,同プロセッサの動作周波数と消費エネルギーを評 価している. 同文献によると, 5nm および 7nm ノードの CNFET を用いた場合, 5nm および 7nm ノードの FinFET を用いた場合に対してプロセッサの動作周波数は約3倍向 上し、サイクルあたりの消費エネルギーは約1/3に減少す る. 論理合成に使用した CNFET セルライブラリは独自の ツールを用いて作成されており、ツールそのものは公開さ れている [3]. ただし、公開されているツールのアーカイ ブには実行に必要ないくつかのファイルが同封されておら ず、上記の実験で使用していた CNFET セルライブラリを 再現することができない状態である. この不具合に関して 開発者に問い合わせたものの返答がなく、上記の公開ツー ルを用いて CNFET セルライブラリを作成することは事実 上不可能である.

文献 [5] では、7nm ノードの CNFET を用いて 16 ビットの RISC-V プロセッサを設計し、テストチップの制作を行っている。同文献によれば、上記のテストチップは 10kHz で動作し、969 $\mu$ W の電力を消費する。設計には著者らが独自に開発した未公開の CNFET セルライブラリを使用しており、同ライブラリは 60 種類以上のセルをサポー

表 1: CNFET のパラメータ

|                                       | 5nm ノード   | 7nm ノード |

|---------------------------------------|-----------|---------|

| W (nm)                                | 21        | 32      |

| $L_g/L_c/L_{ext}$ (nm)                | 10/15/8.5 | 9/9/12  |

| $H_g$ (nm)                            | 20        | 30      |

| $T_{ox}$ (nm)                         | 1.9       | 2.0     |

| $K_{ox}$                              | 10.6      | 10.3    |

| $K_{spacer}$                          | 4.0       | 5.0     |

| d (nm)                                | 1.8       | 1.7     |

| s (nm)                                | 2         | 4       |

| $l_{off} (\mathrm{nA}/\mu\mathrm{m})$ | 100       | 100     |

| $V_{dd}$ (V)                          | 0.375     | 0.4     |

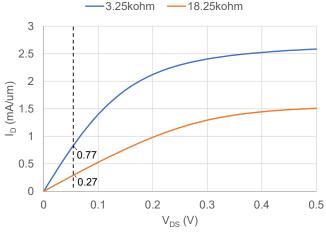

図 2: 7nm CNFET の I-V 特性

トすることが文献に記載されている。他にも各セルのレイアウトや出力波形などの情報は文献に記載されているものの、各セルの消費電力や遅延などの詳細なデータは記載されておらず、文献内の情報だけから上記の実験に使用された CNFET セルライブラリを再現することはできない。

# 3. CNFET セルライブラリ

今回開発した CNFET セルライブラリは,5nm および7nm ノードの CNFET セルライブラリである. CNFET のトランジスタモデルには,文献 [4] と同様,スタンフォード大学が開発した VS-CNFET モデル [13] を採用した.

5nm および 7nm ノードの CNFET の主要なパラメータを**表 1** に示す.表の各パラメータの値は,文献 [4] に記載されている値と同じである.同文献に記載のないパラメータについては値を振って SPICE シミュレーションを行い,シミュレーションによって求めた I-V 特性が同文献に記載されている I-V 特性と一致する値を採用した.

7 nm ノードの CNFET セルライブラリの作成に使用した CNFET モデルの I-V 特性を**図 2** に示す.図の青色の線は接触抵抗が  $3.25 \text{k}\Omega$  の場合,橙色の線は接触抵抗が  $18.25 \text{k}\Omega$  の場合を表している. $V_{DS} = 0.05 \text{V}$  (線形領域)に おけるドレイン電流( $I_D$ )は,接触抵抗が  $3.25 \text{k}\Omega$  の場

合に  $0.77\text{mA}/\mu\text{m}$ ,  $18.25\text{k}\Omega$  の場合に  $0.27\text{mA}/\mu\text{m}$  であった.これらの値は文献 [4] に記載されている値(それぞれ  $0.75\text{mA}/\mu\text{m}$  と  $0.27\text{mA}/\mu\text{m}$  )とほぼ一致しており,同文献で使用されていた CNFET モデルを高い精度で再現できた と考えている.

上記の CNFET モデルを用いて AND2\_X1, AND2\_X2, INV\_X1 など計 56 種類のセルのネットリストを作成し, SPICE シミュレーションを行うことで各セルの遅延と消費電力を求めた. 遅延モデルは CCS(Composite Current Source)と NLDM(Non-Linear Delay Model)の 2 種類を用いた. セル面積は, ゲートピッチの比をスケーリングファクターとして NanGate 15nm オープンセルライブラリ [11] の各セルの面積から求めた. 同様の計算方法は先行研究で用いられているセルライブラリ作成ツール [3] 内でも使用されており, 問題ないと考えている. このようにして求めた値を元に, 論理合成に必要な CNFET セルライブラリ (.lib ファイル)を作成した.

# 4. 評価方法

前章で述べた CNFET セルライブラリを用いて OpenSPARC T2 プロセッサの論理合成を行い、プロセッサ内の各ユニットの消費電力/面積/回路遅延を評価した. 以下では、OpenSPARC T2 のアーキテクチャをまず述べた後、具体的な評価方法を述べる.

#### 4.1 OpenSPARC T2

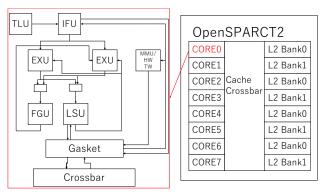

OpenSPARC T2 [14] は旧サン・マイクロシステムズ社 (現オラクル社) によって開発されたオープンソースのプロセッサである。OpenSPARC T2 は8 つのインオーダコアからなるマルチコアプロセッサであり(図 3 右),各コアは8 つのスレッドを細粒度マルチスレッディング方式によって処理する。各コアは,8 ステージの整数系パイプラインと12 ステージの浮動小数点系パイプラインを有する。キャッシュメモリは,プライベートな L1 キャッシュと共有 L2 キャッシュの 2 階層によって構成されている。

コア内の主要ユニット(図3左)を以下に列挙する.

IFU (Instruction Fetch Unit) 命令フェッチを行うユニットであり、以下の3つのサブユニットで構成される.

CMU (Cache Miss Logic Unit) キャッシュミス した命令の処理を行うユニット.

**FTU (Fetch Unit)** 命令をメモリから取り出すユニット.

**IBU** (Instruction Buffer Unit) FTUによって取り出された命令を格納するためのバッファ.

PKU (Pick Unit) 複数のスレッドから実行可能なスレッドを選択するユニット.

DEC (Decode Unit) 命令デコードを行うユニット.

IPSJ SIG Technical Report

図 3: OpenSPARC T2 の構成

**EXU (Execution Unit)** 整数型の算術演算(乗算と除 算を除く)と論理演算を行うユニット. 各コアに 2 つ ずつ搭載されている.

FGU (Floating-Point and Graphics Unit) 浮動小数点演算, 画像演算, 整数型乗算/除算を行うユニット.

LSU (Load/Store Unit) データのロードとストアを 行うユニット.

MMU (Memory Management Unit) メモリの保護 やアドレス変換などを行うユニット.

PMU (Power Management Unit) クロックゲーティングによるユニット単位の電力制御を行うユニット.

**TLU (Trap Logic Unit)** 例外/トラップ処理を行うユニット.

**GKT** (Gasket) コアとキャッシュのクロスバスイッチのアービタ.

GLU (Glue Logic Unit) ユニット間を繋ぐ糊のよう な役割を果たすロジック.

上記以外にL1キャッシュ,レジスタファイルなどのユニットがコア内に存在する. ただし,これらの(OpenSPARC T2ではメガセル [15]と総称される)メモリは通常はマクロとして定義されるものであり,スタンダードセルライブラリを用いて論理合成されるものではない. 実際,OpenSPARC T2の通常の論理合成プロセスでもこれらのメモリは合成の対象とならないことから,本稿でも評価の対象外とした.

#### 4.2 具体的な評価方法

今回開発した CNFET 7nm および 5nm セルライブラリ (以下ではそれぞれを CNFET7, CNFET5 とする) に加えて、Si-MOSFET のセルライブラリである NanGate 45nm および 15nm オープンセルライブラリ (以下ではそれぞれを OCL45, OCL15 とする) を用いて OpenSPARC T2 プロセッサのコア 1 つを論理合成し、コアおよびコア内の各ユニットの消費電力/回路面積/回路遅延の評価を行った.各セルライブラリのコンパイルには Synopsys 社のライブラリコンパイラ (バージョン M-2017.06-SP3) を、論理合成に

は同社のデザインコンパイラ (バージョン O-2018.06-SP4) を使用した.

論理合成の結果は回路の目標動作周波数によって異なることが予想される.一般には、目標動作周波数が低い時はタイミングマージンに余裕があるため低消費電力な回路が合成されやすい一方、目標動作周波数が高い時は厳しいタイミングマージンを満たすため高消費電力な回路が合成されやすい.そこで本稿では、複数の目標動作周波数に対してコアの論理合成を行い、結果を比較する.具体的には、目標動作周波数が0.1,0.2,0.4,0.8,1.6,3.2,6.4,12.8GHzの8通りについて論理合成を行い、それぞれの動作周波数におけるコアとコア内の各ユニットの消費電力を計測した.

詳しくは次章で述べるが、OCL45 に関しては目標動作周波数が 1.6GHz 以上になると論理合成時にタイミング制約違反が発生し、目標とする周波数で動作可能な回路を得ることができない.そのため、各ユニットの消費電力/面積/回路遅延を評価する際は、全てのセルライブラリで動作可能な回路が得られる最高動作周波数(具体的には 0.8GHz)に着目して分析を行った.

次章で示すデータは回路の論理合成のみを行った結果であり、配置配線まで行った結果ではない点に注意されたい.すなわち、セル間を結ぶ配線の消費電力/面積/遅延は今回の結果に含まれていない.トランジスタの CNFET 化がセル間の配線に与える影響を評価するためには論理合成だけでなく配置配線まで行う必要があり、配置配線まで行った場合の消費電力/面積/遅延の評価は今後実施する予定である.

## 5. 評価結果

#### 5.1 コア全体の評価

# 5.1.1 電力性能

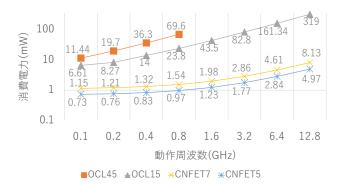

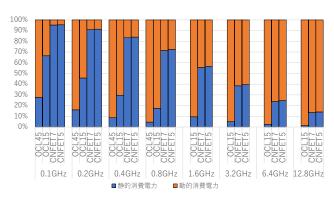

各セルライブラリを用いて論理合成したコアの動作周波数と消費電力を図4に示す.グラフの横軸はコアの動作周波数,縦軸はコアの消費電力を表している.グラフより,いずれのセルライブラリにおいても動作周波数の増加にほぼ比例してコアの消費電力は増加する.ただし,OCL15の場合は0.4GHz以下,CNFET7とCNFET5の場合は1.6GHz以下の領域において動作周波数に対する消費電力の変化は緩やかとなる.これは,後述するように,動作周波数が高い領域ではコアの消費電力において静的消費電力(動作周波数に比例しない成分)よりも動的消費電力(動作周波数に比例しない成分)よりも動的消費電力(動作周波数に比例する成分)が支配的となり,動作周波数が低い領域ではその逆となるためである.

なお、OCL45 に関しては、目標動作周波数を 1.6GHz 以上に設定するとタイミング制約を満たす回路を論理合成できなかった。そのため、OCL45 の 1.6GHz 以上の消費電力はグラフにはプロットしていない。すべてのセルライブラリに対して動作可能な回路が得られた 0.8GHz に

IPSJ SIG Technical Report

図 4: コアの動作周波数と消費電力

図 5: 動的消費電力と静的消費電力の内訳

おいては、CNFET7 および CNFET5 は OCL15 に対してそれぞれ 94.4%および 96.6%、また OCL45 に対してそれぞれ 97.8%および 98.6%の消費電力を削減できることがわかった.

IRDS によれば、Si-MOSFET のスイッチングに必要な消費エネルギーは、7nm から 5nm に微細化されると 22.4%減ると予想されている [7]. したがって、微細化が 1 世代進むごとに Si-MOSFET 回路の消費電力は 30%減ると考えれば、OCL15 から 5nm ノードまで 3 世代(10nm $\rightarrow$ 7nm $\rightarrow$ 5nm)微細化が進むと回路の消費電力は 34.3%になると考えられる。また、文献 [4] によると、5nm ノード CNFET を用いた場合の OpenSPARC T2 の消費電力は 5nm ノード FinFET を用いた場合の 1/4 以下であることから、OCL15 に対する 5nm ノード CNFET の消費電力削減量は 91.1%程度と考えられる。前述した OCL15 に対する CNFET5 の消費電力削減量(<math>96.6%)は上記の見積もりに近い値であり、今回の実験結果は妥当と考えている。

# 5.1.2 動的/静的消費電力の内訳

各動作周波数におけるコアの動的消費電力と静的消費電力の内訳を図 5 に示す. グラフより,まず全体的な傾向として,CNFET は Si-MOSFET より静的消費電力の割合が大きい.特に動作周波数 0.1GHz においては,OCL15 の消費電力の約 65%が静的消費電力によるものだったのに対し,CNFET7 および CNFET5 の消費電力の 90%以上が静的消費電力によるものであった.また,4 つのセルライブ

表 2: 各ユニットの消費電力(単位:mW. 括弧内の数字は OCL15 に対する比率%)

|         | OCL45      | OCL15 | CNFET7     | CNFET5     |

|---------|------------|-------|------------|------------|

| GLU     | 0.87(294)  | 0.30  | 0.03(8.51) | 0.02(5.32) |

| DEC     | 0.98(332)  | 0.30  | 0.02(5.60) | 0.01(3.50) |

| EXU     | 4.63(277)  | 1.67  | 0.01(7.76) | 0.08(4.94) |

| FGU     | 22.47(320) | 7.01  | 0.37(5.30) | 0.23(3.34) |

| GKT     | 1.99(298)  | 0.67  | 0.04(6.71) | 0.03(4.19) |

| IFU_CMU | 1.77(317)  | 0.03  | 0.19(6.18) | 0.02(3.85) |

| IFU_FTU | 4.58(300)  | 0.10  | 0.51(6.49) | 0.06(4.12) |

| IFU_IBU | 5.62(283)  | 0.14  | 0.74(6.37) | 0.08(4.03) |

| LSU     | 7.72(274)  | 2.82  | 0.19(6.81) | 0.12(4.27) |

| MMU     | 6.32(268)  | 2.35  | 0.17(7.02) | 0.10(4.40) |

| PKU     | 1.85(298)  | 0.62  | 0.04(7.21) | 0.03(4.50) |

| PMU     | 1.26(269)  | 0.47  | 0.04(8.05) | 0.02(5.06) |

| TLU     | 9.50(269)  | 3.54  | 0.25(7.04) | 0.16(4.44) |

| Total   | 69.6(292)  | 23.8  | 1.54(6.46) | 0.97(4.07) |

図 6: 各ユニットの消費電力の割合

ラリに共通する性質として、動作周波数が高くなるほど動的消費電力の占める割合が大きくなることが確認できた.これは、CMOS 回路の動的消費電力は動作周波数に比例する一方、静的消費電力は動作周波数によらず一定なためである.

#### 5.2 ユニットごとの評価

### 5.2.1 消費電力

動作周波数が 0.8GHz のときの各ユニットの消費電力を **表 2** に示す. 表より, OCL15 から CNFET7 または CN-FET5 に変更することで最も消費電力が削減されたユニットは FGU であった. 特に CNFET5 の FGU の消費電力 は, OCL15 の FGU の消費電力の 3.34%であった.

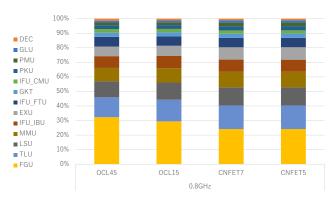

コア全体の消費電力に占める各ユニットの消費電力の割合を図6に示す.グラフより、OCL45とOCL15ではFGUの消費電力が全体の約30%を占めていたのに対して、CNFET7とCNFET5ではその割合が約25%に低下していることが確認できた.一方、その他のユニットの消費電力割合に関しては、セルライブラリの違いによる違いはほとんど見られなかった.

表 3: 各ユニットの回路面積(単位: $\mu m^2$ . 括弧内の数字は OCL15 に対する比率%)

|         | OCL45       | OCL15  | CNFET7      | CNFET5      |

|---------|-------------|--------|-------------|-------------|

| GLU     | 7383(367)   | 2010   | 873(43.5)   | 873(43.4)   |

| DEC     | 4287(354)   | 1209   | 517(42.8)   | 518(42.8)   |

| EXU     | 34155(356)  | 9581   | 4182(43.7)  | 4186(43.7)  |

| FGU     | 84689(357)  | 23714  | 10280(43.4) | 10287(43.4) |

| GKT     | 12802(357)  | 3585   | 1491(41.6)  | 1491(41.6)  |

| IFU_CMU | 8598(359)   | 2389   | 1027(43.0)  | 1027(43.0)  |

| IFU_FTU | 27071(362)  | 7468   | 3212(43.0)  | 3216(43.1)  |

| IFU_IBU | 26303(332)  | 7922   | 3415(43.1)  | 3425(43.2)  |

| LSU     | 54447(358)  | 15174  | 6502(42.9)  | 6504(42.9)  |

| MMU     | 42600(352)  | 12079  | 5211(43.1)  | 5208(43.1)  |

| PKU     | 14247(394)  | 3611   | 1552(43.0)  | 1555(43.1)  |

| PMU     | 11057(355)  | 3106   | 1336(43.0)  | 1335(43.0)  |

| TLU     | 70705(357)  | 19760  | 8478(42.9)  | 8487(43.0)  |

| Total   | 398351(356) | 111614 | 48084(43.1) | 48117(43.1) |

図 7: 各ユニットの面積の割合

## 5.2.2 回路面積

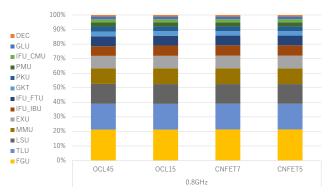

動作周波数が  $0.8 \mathrm{GHz}$  のときの各ユニットの回路面積を表 3 にまとめた。OCL15 から CNFET7 および CNFET5 に変更することで最も回路面積が削減されたユニットは GKT であった。特に CNFET5 の GKT の回路面積は, OCL15 の 41.6%であった。ただし,OCL15 に対する面積削減率が最も小さかった EXU(43.7%)との差は 2.1 ポイントであり,その差はわずかと言える。

また CNFET7 と CNFET5 を比較すると、CNFET5 に 比べて CNFET7 の方がコア全体の面積は  $33\mu\text{m}^2$  小さかっ た.この原因として以下の 2 点が考えられる.

- (1) 表 1 より、CNFET7 と CNFET5 で使用されているトランジスタはゲートピッチ( $L_g+L_c+2\times L_{ext}$ )の大きさがまったく同じである。そのため、3 章で述べたセル面積の計算方法にしたがうと、2 つのセルライブラリ間で同じ種類のセルの面積がまったく同じになる。

- (2) CNFET7 と CNFET5 ではデザインコンパイラが論理合成に使用するセルの種類が微妙に異なっており、CNFET7 の方がわずかに小面積なセルが選択された.コア全体の面積に占める各ユニットの面積の割合を**図7**

表 4: 各ユニットの回路遅延(単位:ps. 括弧内の数字は OCL15 に対する比率%)

|         | OCL45      | OCL15  | CNFET7       | CNFET5       |

|---------|------------|--------|--------------|--------------|

| DEC     | 880(1850)  | 47.48  | 23.74 (50.0) | 19.08 (40.2) |

| EXU     | 1050(1620) | 64.97  | 39.64 (61.0) | 25.43 (39.1) |

| FGU     | 580(1710)  | 33.86  | 21.57 (63.7) | 14.03 (41.4) |

| GKT     | 510(2240)  | 20.9   | 3.76 (18.0)  | 2.57(12.3)   |

| IFU_CMU | 810(1950)  | 41.60  | 24.50 (58.9) | 15.70 (37.7) |

| IFU_FTU | 750(1890)  | 39.75  | 24.66 (62.0) | 16.59 (41.7) |

| IFU_IBU | 600(1920)  | 31.27  | 21.43 (68.5) | 13.75 (44.0) |

| LSU     | 900(1590)  | 56.70  | 30.66 (54.1) | 20.15 (35.5) |

| MMU     | 740(1320)  | 55.87  | 34.10 (61.0) | 22.45 (40.2) |

| PKU     | 1250(973)  | 128.46 | 63.80 (49.7) | 40.78 (31.7) |

| PMU     | 660(1530)  | 43.14  | 22.96 (53.2) | 14.60 (33.8) |

| TLU     | 730(3560)  | 20.51  | 11.39 (55.5) | 7.03 (34.3)  |

図 8: PKU に対する各ユニットの遅延時間の比率

に示す. グラフより, ユニットの面積割合に関してはセルライブラリの違いによる違いが見られない. CNFET 化によって各ユニットの面積がほぼ同じ比率で削減されていることがわかる.

### 5.2.3 回路遅延

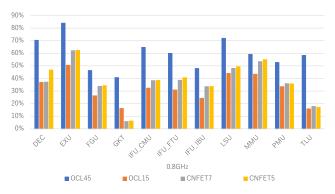

動作周波数が 0.8GHz のときの各ユニットの回路遅延を**表 4** に示す。OCL15 から CNFET7 および CNFET5 に変更した際の回路遅延削減率が最も高かったユニットは GKT であり,CNFET5 の GKT の回路遅延は OCL15 のそれの約 12.3%になった。一方,回路遅延の削減率が最も小さかったユニットは IFU\_IBU であり,CNFET5 の IFU\_IBU の回路遅延は OCL15 のそれの 44.0%になった。

4つのライブラリに共通して、回路遅延が最も大きいユニットは PKU であった.そこで、PKU の回路遅延に対する各ユニットの回路遅延の比率を図 8 にまとめた.グラフより、3 番目に回路遅延が大きなユニットは、OCL45 とOCL15 では LSU なのに対して CNFET7 と CNFET5 では MMU であった.また、OCL15 の MMU の回路遅延は PKU のそれの約 40%だったのに対し、CNFET5 の MMU の回路遅延は PKU のそれの約 55%であった.このように、CNFET 化によってユニットのクリティカリティが変化することが確認できた.

IPSJ SIG Technical Report

# 6. おわりに

本稿では我々が開発した CNFET セルライブラリを用いて OpenSPARC T2 プロセッサの論理合成を行い, CNFET を用いたプロセッサの各ユニットの電力/面積/回路遅延を評価した. 評価の結果, CNFET 7nm および 5nm セルライブラリを用いた場合, NanGate 15nm オープンセルライブラリを用いた場合と比較して, OpenSPARC T2 プロセッサの各ユニットの消費電力を最大 96.7%, 回路面積を最大 58.4%, 回路遅延を最大 87.7%削減できることがわかった. また, ユニット間のバランスは, 消費電力と回路面積に関しては CNFET 化によってほとんど変わらなかったのに対し, 回路遅延に関しては CNFET 化によってその差が縮小する傾向にあることが確認できた.

今後は論理合成だけでなく配置配線まで行い、トランジスタの CNFET 化が各ユニットの配線遅延に与える影響を詳しく調査する。また、今回は評価対象に含めなかったレジスタファイルやキャッシュなどのメモリについてもCNFET 化した際の消費電力/面積/回路遅延の見積もりを行い、その効果を分析することを考えている。さらには、インオーダプロセッサだけでなくアウトオブオーダプロセッサについても論理合成と配置配線を行い、アウトオブオーダプロセッサの各ユニットに対して CNFET 化が与える影響を詳細に分析する予定である。

謝辞 本研究は JSPS 科研費 JP18K19778 の助成を受けて、東京大学大規模集積システム設計教育研究センターを通しシノプシス株式会社の協力で行われたものである.

# 参考文献

- Clark, L. T., Vashishtha, V., Shifren, L., Gujja, A., Sinha, S., Cline, B., Ramamurthy, C. and Yeric, G.: ASAP7: A 7-nm finFET predictive process design kit, Microelectronics Journal, Vol. 53, pp. 105–115 (2016).

- [2] Eeckhout, L.: Is Moore's Law Slowing Down? What's Next?, *IEEE Micro*, Vol. 37, No. 04, pp. 4–5 (2017).

- Hill, G.: Variation-aware Nanosystem Design Kit (NDK), Internet:nanohub.org/resources/22582 (July 29, 2015 [June 9, 2021]).

- [4] Hills, G., Bardon, M. G., Doornbos, G., Yakimets, D., Schuddinck, P., Baert, R., Jang, D., Mattii, L., Sherazi, S. M. Y., Rodopoulos, D., Ritzenthaler, R., Lee, C.-S., Thean, A. V.-Y., Radu, I., Spessot, A., Debacker, P., Catthoor, F., Raghavan, P., Shulaker, M. M., Wong, H.-S. P. and Mitra, S.: Understanding Energy Efficiency Benefits of Carbon Nanotube Field-Effect Transistors for Digital VLSI, IEEE Transactions on Nanotechnology, Vol. 17, pp. 1259–1269 (2018).

- [5] Hills, G., Lau, C., Wright, A., Fuller, S., Bishop, M. D., Srimani, T., Kanhaiya, P., Ho, R., Amer, A., Stein, Y., Murphy, D., Arvind, Chandrakasan, A. and Shulaker, M. M.: Modern Microprocessor Built from Complementary Carbon Nanotube Transistors, *Nature*, Vol. 572, pp. 595—602 (2019).

- [6] IRDS: International Roadmap for Devices and Systems

- 2018 Beyond CMOS-, Whitepaper (2018).

- [7] IRDS: International Roadmap for Devices and Systems 2018 – More Moore–, Whitepaper (2018).

- [8] NC State University: FreePDK, Internet:www.eda.ncsu.edu/wiki/FreePDK (May 29, 2014 [June 10, 2021]).

- [9] Qiu, C., Zhang, Z., Xiao, M., Yang, Y., Zhong, D. and Peng, L.-M.: Scaling Carbon Nanotube Complementary Transistors to 5-nm Gate Lengths, *Science*, Vol. 355, pp. 271–276 (2017).

- [10] Shulaker, M. M., Hills, G., Patil, N., Wei, H., Chen, H.-Y., Wong, H.-S. P. and Mitra, S.: Carbon Nanotube Computer, *Nature*, Vol. 501, pp. 526—530 (2013).

- [11] Silicon Integration Initiative: 15nm Open-Cell Library and 45nm FreePDK, Internet:si2.org/open-cell-library/ ([June 10, 2021]).

- [12] Simonite, T.: IBM: Commercial Nanotube Transistors Are Coming Soon, Internet:www.technologyreview.com/ 2014/07/01/172177/ibm-commercial-nanotubetransistors-are-coming-soon/ (July 1, 2014 [June 9, 2021]).

- [13] Stanford Nanoelectronics Lab: VS-CNFET Model, Internet:nano.stanford.edu/stanford-cnfet2-model (July 2, 2021 [June 10, 2021]).

- [14] Sun Microsystems: OpenSPARC T2 Core Microarchitecture Specification, Whitepaper (2007).

- [15] Sun Microsystems: OpenSPARC T2 Processor Megacell Specification, Whitepaper (2007).