# プログラマブルSoCのためのシステム設計環境の検討と SW-HW インタフェース生成手法の実装

東 遼平 $^{1,a)}$  高瀬 英希 $^1$  高木 一義 $^1$  高木 直史 $^1$

概要:近年,プロセッサと FPGA を 1 チップに集積したプログラマブル SoC が注目されている.この SoC では,求められる負荷と柔軟性が異なる処理を混在させたシステムが実現できる.本研究では,高性能な組込みプロセッサを搭載したプログラマブル SoC を対象としたソフトウェア中心のシステム設計環境について検討する.本環境では,設計者がハードウェアやインタフェースの知識無しに,ソフトウェア向けの高級言語の知識のみでシステムを設計できるようにすることを目指す.ソフトウェア向け高級言語からのハードウェアの合成には高位合成を適用する.また,本研究では,ソフトウェアとハードウェアのインタフェースを生成する手法の実装について説明する.設計者は,ソフトウェア向けの高級言語によるシステム全体の設計およびシステムの構成情報の指定のみで,プログラマブル SoC に特有のソフトウェアとハードウェア間のインタフェースを自動生成することができる.

キーワード:プログラマブル SoC, 高位合成

# A Study of a System Design Environment and Implementation of a SW-HW Interface Synthesis Method for Programmable SoCs

Abstract: Recently, programmable SoCs which integrate a processor and an FPGA on one chip are released and attracting attentions. A programmable SoC can realize systems composed of various processes with different requirements of the load and flexibility. In this paper, we study a software-centric system design environment targeting programmable SoCs equiped with high performance embedded processors. The environment makes designers to be able to design systems with only the knowledge of software programming languages and without that of hardware and the interfaces. In the environment, we apply conventional high-level synthesis systems to the hardware part. In this manuscript, we describe the method of generating the interface between software and hardware in detail. Using the method, we can automatically generate software/hardware interfaces, which are distinctive feature of programmable SoCs, by specifying the whole system design and system configurations.

Keywords: Programmable SoC, High Level Synthesis

# 1. はじめに

近年,プロセッサと FPGA ( Field Programmable Gate Array ) を 1 チップに集積したプログラマブル SoC が登場し,注目を集めている.従来の SoC とは異なる点として,プロセッサと FPGA の通信が高速であること,および,搭載されるプロセッサが高性能であることが挙げられる.これらの利点から,同一の SoC で様々な構成のシステムを

設計することが可能となった.プログラマブル SoC では , プロセッサと FPGA が専用のオンチップバスで接続される.このため , プロセッサと FPGA が別 SoC として接続された従来のヘテロジニアスシステムとは異なり , 両者の高速な通信が可能である.また , Xilinx 社 Zynq-7000 All Programmable SoC\*1 [1] や Altera 社 SoC FPGA [2] のようなプログラマブル SoC では , ARM Cortex-A9 という600MHz から 1GHz ほどの高速なクロック周波数で動作できる組込みシステム向けプロセッサが搭載されている.

<sup>1</sup> 京都大学 大学院情報学研究科

Graduate School of Informatics, Kyoto University

a) azuma@lab3.kuis.kyoto-u.ac.jp

<sup>\*1</sup> 以降 , 単に Zynq-7000 と記す .

プロセッサ上のソフトウェアは,負荷の変動が大きく柔軟性が求められる処理に向いている.FPGA 上のハードウェアは,処理内容や負荷は一定であるものの高速な応答性が求められる処理に向いている.プログラマブル SoC のプロセッサは高性能であるため,異なる負荷と柔軟性が求められるタスク\*2を混在させたシステムが実現できることが期待される.このようなシステムの例として,カーナビゲーションシステムでは,GPS や経路探索のような高速かつ柔軟な処理が求められるタスクはプロセッサ上で,マップ表示のように処理速度が求められるタスクはハードウェアに合成して処理することが効率的であると考えられる.

これまでにもプログラマブル  $\operatorname{SoC}$  を使った設計 [3] が報告されているが,プログラマブル  $\operatorname{SoC}$  の特徴のひとつである高性能なプロセッサを有効に活用できた事例は,著者らの知る限り存在しない.既存の協調設計環境 [4], [5] は,ソフトウェアは  $\operatorname{FPGA}$  上のソフトコアで実行されることを前提としており,プログラマブル  $\operatorname{SoC}$  を採用したシステム設計に適用できない.さらに,協調設計においてシステム設計者は,ソフトウェアとハードウェア両方の深い知識が求められる.また,プログラマブル  $\operatorname{SoC}$  はプロセッサと  $\operatorname{FPGA}$  の接続が特徴的であり,このインタフェース設計に関する知識も必要とされる.

本稿では、高性能な組込みプロセッサが搭載されたプログラマブル SoC において、ソフトウェアとハードウェアが協調動作するシステムのための設計環境を検討する。ターゲットとなるシステムは Zynq-7000 の評価ボードである ZedBoard [6] を採用する・検討する設計環境に求められる要件として、システム全体の設計がネイティブな C 言語で可能であることを挙げる。これにより、設計生産性の向上を図る。なお、入力の設計の中においてハードウェアとする部分には高位合成の技術を利用する。これにより、設計者はハードウェアの設計手法に関する知識なしにハードウェアを設計することが可能になる。なお、本稿では特に、システム設計環境における構成情報の規定について議論する。構成情報を入力とすることで、設計者は高い抽象度でアーキテクチャを選択することができる。

本研究ではさらに,システム設計環境内におけるフロントエンドを実装する.フロントエンドの機能は,ソフトウェア向け高級言語による設計から指定された箇所のハードウェアへの切り出し,および,ソフトウェアとハードウェア間のインタフェースの生成からなる.前者では,設計環境の入力となるソースファイルは,ソフトウェアとして動作する部分とハードウェアとして動作する部分に切り分けられる.後者では,構成情報の指定に応じて,適切なインタフェースが自動的に生成される.

本稿の構成は以下の通りである.2章では,準備として

\*2 本稿では,システム内の実行単位をタスクと定義する.

プログラマブル SoC および高位合成について解説する .3 章では , プログラマブル SoC のためのシステム設計環境について検討する .4 章では , システム設計環境のフロントエンドを実装について述べる .5 章では , 本稿のまとめと今後の方針を述べる .

# 2. 準備

#### 2.1 プログラマブル SoC

プログラマブル SoC とは,ハードマクロのプロセッサと FPGA を 1 チップ上に搭載した SoC のことである.特徴 として,プロセッサと FPGA の接続がチップ上に実装されるため,両者の高速な通信が可能であることが挙げられる.また,近年の市場では,搭載されるプロセッサが 600MHz から 1GHz と高性能なものも発表されている,このようなプログラマブル SoC は,FPGA ベンダなどから多様な種類の製品がリリースされている.その中で本稿では,2011年 3 月に Xilinx 社より発表されたプログラマブル SoC である Zynq-7000 について詳述する.

ハイエンドの組込みシステムを対象とした Zynq-7000 は,プロセッシングシステム(PS)およびプログラマブル ロジック(PL)の2つで構成されている.前者はデュアル コアの ARM Cortex-A9 プロセッサを中心として,キャッ シュ,オンチップメモリ,外部メモリインタフェース,DMA コントローラ,および,入出力ペリフェラルで構成されて いる.後者は構成可能論理ブロック,RAM,ディジタル 信号処理ブロック、プログラマブル入出力ブロック、シリ アルトランシーバ, および, A-D コンバータで構成されて いる . PS の ARM Cortex-A9 プロセッサの最大動作周波 数は 600MHz から 1GHz となっている.これは, FPGA 上にソフトコアとしてプロセッサを合成した場合のものと 比べて,数倍高速なものとなっている.また,PSとPL は複数層の ARM AMBA ( Advanced Microcontroller Bus Architecture ) AXI(Advanced eXtensible Interface)を使 用して接続されており,両者間の高速な通信を可能にして

## 2.2 Zynq-7000 における通信方式

Zynq-7000 の ARM AMBA AXI における PS-PL 間通信では,表 1 に示すようにいくつかの通信ポートが用意されている.ここで,GP-AXI は汎用 AXI のポートである.次に,AXI-HP はオンチップメモリまたは DDR メモリへのアクセスのためのポートである.最後に,AXI-ACP はキャッシュへのアクセスのためのポートである.以上の 3 種類の通信ポートを利用して,以下の PS-PL 間の通信を行うことができる.

## PS から PL へのアクセス

PL 内に生成されたメモリに対して PS 内のソフトウェアからアクセスを行う . PS がマスターとなる GP-AXI ポー

表 1 Zynq-7000 における通信ポート

|         | タイプ          | バス幅   | ポート数 |

|---------|--------------|-------|------|

| GP-AXI  | PS マスター/スレーブ | 32bit | 2    |

| AXI-HP  | PS スレーブ      | 64bit | 4    |

| AXI-ACP | PS スレーブ      | 64bit | 1    |

トを経由して通信を行う.このポートは帯域幅が小さくバス幅が32 ビットであるため,パラメータ設定や動作制御,または小規模のデータの通信に適している.

### PL からメモリへのアクセス

オンチップメモリおよび DDR メモリに対して PL からアクセスを行う . PL がマスターとなる AXI-HP ポートを経由して通信を行う . バス幅は 64 ビットで大規模なデータの通信に適している . なお , AXI-HP ポートはチップ上に 4 つ用意されているため , 複数の専用回路のデータを並列に制御する用途にも利用できる .

### PL からキャッシュへのアクセス

PS 内のキャッシュに対して PL からアクセスを行う. PL がマスターとなる AXI-ACP ポートを経由して通信を行う.キャッシュ上のデータの制御となるため,大規模なデータに対しては適用できないが, PS 内では DDR メモリヘのアクセスより高速に処理できる.

#### 2.3 高位合成

高位合成とは、ソフトウェア向け高級言語からハードウェア記述言語(HDL)を生成する技術のことである.高位合成を実現するツールとしては、Vivado HLS [7], Bach [8], CyberWorkBench [9], および、eXCite [10] などが挙げられる.また、高位合成を用いたシステム設計の事例としては、[11] が報告されている.

設計生産性の観点からは、合成される回路の詳細な仕様を意識することなくハードウェアが設計できることが望ましい、ソフトウェア向けの完全にネイティブな高級言語でハードウェア設計ができれば、設計者の負担の軽減に繋がる、しかし、Vivado HLSではSystemC、BachではBachCなど、これらのツールの多くはソフトウェアの高級言語に仕様拡張した言語による記述が入力となる、これらの言語は、並列記述などを追加することで合成される回路の性能を高める狙いがある、しかし、このような言語仕様拡張は、結局のところ設計者にハードウェアの知識を要求することとなっている、一方、CyberWorkBenchおよびeXCiteでは、ほぼネイティブなC言語による記述を入力として扱える、しかし、以上で挙げた高位合成ツールは、すべて商用でありそのソースコードは公開されていない。

以上の議論から,本稿では,ほぼネイティブな C 言語による記述を入力とし,かつ,フリーソフトウェアである LegUp [12] に着目する.LegUp は,Verilog HDL による記述を生成する高位合成ツールである.オープンソースで

あるため,独自の処理や機能を追加できるという利点もある.入力の C 言語は,完全にネイティブではないものの,再帰関数,動的メモリ,浮動小数点数の構造をもたない C 言語のプログラムはすべて合成可能である.LegUpのフロントエンドは Clang [13] を用いており, C 言語をいったんLLVM 固有の中間表現である LLVM IR に変換し,これをバックエンドで処理を行い, Verilog HDL による記述を合成する.

# 3. システム設計環境の検討

### 3.1 要件と全体像

本稿で検討するシステム設計環境が満たすべき要件について議論する.

まず,本設計環境の入力として与えるシステムの設計は,すべてほぼネイティブな C 言語のみで行う.つまり,設計対象のハードウェアやインタフェースの詳細な仕様や設計を意識することなく,ソフトウェア向けの高級言語のみでシステムを設計できるようにする.ソフトウェア開発の知識または経験のみを持つ設計者でもプログラマブル SoCを用いたシステム設計ができるようになり,設計生産性の向上を図ることができる.

システム設計環境の扱う処理粒度は,関数単位とする.これは,ソフトウェア設計においては,一般に関数の粒度でソフトウェアの各機能が定義されるためである.さらに,ターゲットとなるプログラマブル SoC に複数の選択肢をもたせることも要件とする.このため,実行モジュールを生成する直前までは,デバイスに依存しない形式のモジュールで処理を行うようにする.ターゲットデバイスの情報は,構成情報として設計環境に与える.

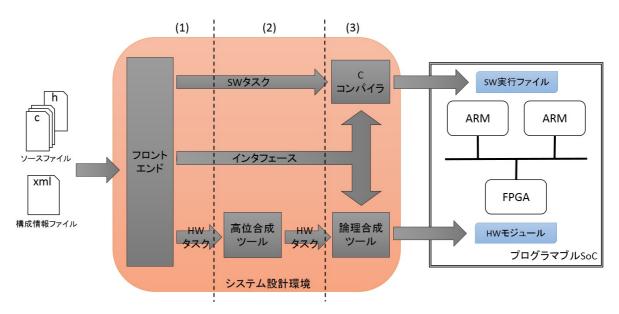

これらの要件を満たすシステム設計環境の全体像を,図1に示す.設計環境の入力は,ソフトウェア向け高級言語のソースファイルと構成情報である.ここで,本設計環境では,ソースファイルはC言語で記述される.構成情報とは,設計したシステム内の各関数の処理方法やインタフェースが記述されたテキストデータである.構成情報の詳細は,3.3節にて解説する.

本設計環境におけるタスクには , SW タスクと HW タスクの 2 種類がある .

- SW タスク プロセッサで実行されるタスク

- HW タスク

FPGA上に専用回路として合成して実行されるタスク どちらのタスクも , コンパイル時点まではデバイスに依存 しない記述である . SW タスクは C 言語による記述 , HW タスクは Verilog HDL による記述である . デバイス独自の 実行ファイルは , ターゲットとなるデバイスに対応したコンパイラや合成ツールを用いることで生成される .

図 1 プログラマブル SoC のためのシステム設計環境の全体像

# 3.2 ワークフロー

本システム設計環境のワークフローについて詳述する. ワークフローはタスク解析,タスク·インタフェース合成, 実行可能モジュール生成の3フェーズから構成される.

#### 3.2.1 タスク解析

このフェーズでは、構成情報に基づいて入力の C ソースファイルを解析し、タスクに分割し、SW タスクと HW タスクを生成する. さらに、ソフトウェアとハードウェア間のインタフェースを生成する. これらの処理は図 1 のフロントエンド内で行われる.

まず,入力の C ソースファイルを解析し,タスク単位に分割する.3.1 節で述べたように,本設計環境におけるタスクの粒度は関数単位である.

次に,構成情報から HW タスクを切り出す.このとき,HW タスクとして指定された関数が高位合成ツールに適用可能であるか検査する.高位合成が適用できない構造には,アーキテクチャ依存およびツール依存がある.アーキテクチャ依存の構造とは,高級言語のファイル操作のように FPGA 上で実行できない構造のことである.一方,ツール依存とは,適用する高位合成ツールの仕様で合成不可能な構造である.この依存は LegUp であれば再帰関数,動的メモリ,および,浮動小数点数が挙げられる.このような構造を含む関数が HW タスクとして設定されている場合には,設計環境が自動で SW タスクとして再設定することとする.

最後に,入力のソースファイルから HW タスクに指定した関数を取り除き,SW タスクを生成する.このとき,SW タスクには,デバイスの初期化を行う関数とその呼び出し,および,HW タスクの関数呼び出しが追加される.HW タスクの関数呼び出し部分は,生成されたインタフェースに対応する適切な記述が挿入される.さらにこのフェーズで

は、構成情報で指定された情報に基づいて、ソフトウェアとハードウェア間のインタフェースを合成するための適切な情報が生成される・インタフェースにおいて通信される情報は、HW タスクの開始信号、終了信号、引数、および、返り値である・

# 3.2.2 タスク・インタフェース合成

このフェーズでは,高位合成ツールにより HW タスクを合成し,さらに,インタフェースを合成する.なお,タスク解析時に生成された SW タスクは次フェーズにおける処理に適用できるため,このフェーズでは特に SW タスクへの処理を行わない.

タスク解析で切り分けられた HW タスクは,高位合成ツールを利用して HDL に変換する. HW タスクとして合成される回路には演算部やメモリ部だけでなく,プロセッサとの通信ポートを追加する必要がある.この要件から,高位合成ツールはオープンソースであることが望ましい.従って,本設計環境では,高位合成ツールに LegUp を採用する.

さらに、構成情報に基づいて、インタフェース情報を含むモジュールが合成される、Zynq-7000を対象とした場合は、この処理は Xilinx Platform Studio (XPS) によって行われる.

#### 3.2.3 実行可能モジュール生成

このフェーズでは,ターゲットのプログラマブル SoC 上で実行可能な形式のモジュールを生成する.SW タスクはデバイスに対応した C コンパイラにより,プロセッサで実行可能なバイナリにコンパイルされる.一方,HW タスクはデバイスに依存したブロック RAM,および,インタフェース情報を含むモジュールと統合した後,論理合成ツールにより FPGA 上に構成可能な実行形式であるビットストリームを合成する.ここで,C コンパイラおよび

図 2 構成情報の記述例

論理合成ツールは構成情報内のデバイスの情報により選択される . Zynq-7000 を対象とした場合は , SW タスクは ARM クロスコンパイラ , HW タスクは Xilinx ISE が用いられる .

#### 3.3 構成情報

本設計環境の入力のひとつである構成情報とは,ターゲットデバイスや OS の有無といったシステム情報,ハードウェアで処理する関数とそのインタフェースの指定などの記述のことである.構成情報の記述例を図 2 に示す.本設計環境では,構成情報は XML 形式で記述されたテキストデータとして与えられるとする.

<device>は,設計対象とするデバイスについて定義する. 'Zynq' や 'SoCFPGA' などのパラメータが想定される. <sw\_task>は,SW タスクの構成について定義する.定義する情報としては,<os>にて OS の選択がある. 'baremetal' は OS 無しの構成であり,OS 有りの構成としては'Linux' や'ITRON' などのパラメータが想定される. <hw\_task>は,HW タスクとそのインタフェースについて定義する. <name>にて HW タスクに設定する関数名, <axi>にて通信ポートを選択する. デバイスを Zynq-7000 と定義した場合には,想定される通信ポートは,2.2節で示した GP-AXI,AXI-HP, AXI-ACP のいずれかであり,パラメータはそれぞれ'gp','hp','acp'で表される. <obj\_func>ではシステム設計の目的関数について定義する. 実行時間,回路面積および消費エネルギーを表す'speed', 'area' および 'energy' などのパラメータが想定される.

# 3.4 検討の現状

本稿執筆時点におけるシステム設計環境の検討の現状について述べる.構成情報の現状については,デバイスは Zynq-7000,SW タスクにおける OS はベアメタル,HW タスクとのインタフェースは GP-AXI のみをサポート範囲としている.つまり,構成情報で指定できる構成は,実質的には HW タスクとする関数のみである.また,HW タスクとする関数の指定に関しても,現状では指定可能な関数は 1 つのみである.今後は,デバイスに関しては SoC

図 3 フロントエンドでの処理

FPGA, OS に関しては Linux や ITRON などといったように,様々なシステム構成が選択可能であるようにサポートしていく予定である. HW タスクには関しては複数の関数を指定できるようにしていく予定である. さらに,本設計環境を用いたシステム設計フローの確立も計画している. 構成情報内<obj\_func>は,これを視野に入れた仕様である.

# 4. フロントエンドの実装

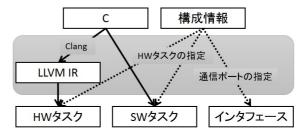

本章では,本稿で検討したプログラマブル SoC のための 設計環境のフロントエンド処理について,その実装を説明する.図3に示すように,フロントエンドでは,タスクの切り分け,および,インタフェースの生成の処理を担う.

#### 4.1 タスクの切り分け

入力である C ソースファイルは,設計環境内のフロントエンドで SW タスクと HW タスクに切り分ける.切り分けは,C ソースファイルから HW タスクとする部分を切り出すことで行う.

SW タスクには,入力ファイルにデバイスの初期化を行う関数およびその呼び出しと HW タスクの関数呼び出しが追加される.この二つの処理は,入力のソースファイルへの記述の追加で実現できるため,入力の C ソースファイルに対して処理を行う.

一方,HW タスクとして切り出される関数については,HW タスクから呼び出される関数や,HW タスク内で使用されるグローバル変数も考慮する必要がある.従って,ソースファイル全体を解析して,タスクを切り分けることになる.しかし,C 言語は記述の自由度が大きいため,対応する解析器の実装コストが大きくなる.従って,HW タスクの切り出しは,記述の自由度の小さい LLVM の中間表現である LLVM IR に変換した上で行う.LLVM IR への変換は,Clangによって行う.なお,LegUp でも Clang で変換された LLVM IR を中間表現として採用している.このため,LLVM IR で記述された HW タスクを LegUp のバックエンドに入力することで高位合成が適用できる.

#### 4.2 インタフェース生成

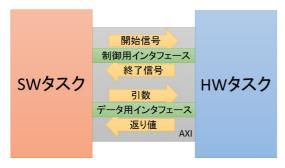

本設計環境では,図4に示すように,1つのタスクに対

図 4 生成されるインタフェース

して制御用途とデータ用途の 2 つのインタフェースを生成する. 前者は制御信号のためのインタフェースで, HW タスクの開始信号および終了信号を送受信する. 後者はデータの受け渡しのためのインタフェースで, HW タスクの引数および返り値を受け取る.

HW タスクおよびインタフェースの実行時の流れを説明する.まず,PS 内の SW タスクから開始信号を送信し,PL 内の HW タスクが起動される.ここで,HW タスクに引数があれば,同時にデータ用のインタフェースを介して引数を HW タスクに送信する.HW タスクの実行完了後には,SW タスクに終了信号が送信される.HW タスク内の実行で返り値を持つ場合は,データ用インタフェースを介してその値も送信される.SW タスク側では,終了信号の通知を監視しており,終了信号の通知時に返り値を受信する.

最後に、それぞれのインタフェースで利用される通信ポートについて説明する.まず、制御用インタフェースでの信号値はビット幅が小さいため、GP-AXIをインタフェースのためのポートとして指定する.一方、データ用インタフェースは、通信されるデータ量や要求される転送速度に応じて、2.2節で紹介したGP-AXI、AXI-HP、AXI-ACPのいずれの通信ポートも選択可能である.ただし、現状の設計環境では、GP-AXIのみのサポートとなっている.なお、インタフェースに使用する通信ポートは構成情報内<axi>に記述することで指定できる.

# 5. おわりに

本稿では、高性能なプロセッサを搭載したプログラマブル SoC のためのシステム設計環境を検討した、本稿における設計環境を用いることにより、設計者はソフトウェア向けの高級言語の知識のみでシステム全体の設計が可能となる、ハードウェア設計およびソフトウェアとハードウェア間のインタフェース設計を設計者から隠蔽することで、設計生産性の向上を図る、

さらに本研究では,システム設計環境におけるフロントエンド部分を実装した.フロントエンドでは,入力ファイルからの SW タスクと HW タスクの切り分け,および,SW-HW 間のインタフェース生成の処理を担う.これらの

処理は,設計者の指定した構成情報に基づいて自動的に行われる.

今後の課題としては,インタフェースやターゲットデバイスなどの構成情報における選択肢の拡充,および,複数の関数を HW タスクとして指定可能とすることが挙げられる.また,システム設計環境が実用可能なものに開発できれば,実用システムの設計への適用事例によってその有用性を評価することも計画している.

# 参考文献

- [1] Xilinx Inc.: Zynq-7000 All Programmable SoC, available from \( \http://japan.xilinx.com/content/xilinx/ja/\) products/silicon-devices/soc/zynq-7000.html\( \).

- [2] Altera 社: アルテラ SoC の概要,入手先 〈http://www.altera.co.jp/devices/processor/soc-fpga/overview/proc-soc-fpga.html〉.

- [3] Dobai, R. and Sekanina, L.: Towards Evolvable Systems Based on the Xilinx Zynq Platform, *Proc. of SSCI 2013*, pp. 89–95 (2013).

- [4] Ha, S., et al.,: PeaCE: A Hardware-Software Codesign Environment for Multimedia Embedded Systems, ACM Trans. of TODAES, Vol. 12, No. 24, pp. 1–25 (2007).

- [5] Honda, S., et al.,: RTOS and Codesign Toolkit for Multiprocessor Systems-on-Chip, *Proc. of ASP-DAC '07*, pp. 336–341 (2007).

- [6] Avnet Internix Inc.: Zedboard, available from \(http://www.zedboard.org/\).

- [7] Xilinx Inc.: Vivado Design Suite, available from (http://japan.xilinx.com/products/design-tools/vivado/).

- [8] Dobai, R. and Sekanina, L.: Hardware synthesis with the Bach system, *Proc. of ISCAS '99*, pp. 366–369 (1999).

- [9] NEC 社: ASIC·FPGA 設計向け C 言語ベース高位合成ツール CyberWorkBench, 入手先 (http://jpn.nec.com/cyberworkbench/).

- [10] Y Explorations Inc.: eXCite, available from (http://www.yxi.com/).

- [11] Navarro, D., et al.,: High-Level Synthesis for Accelerating the FPGA Implementation of Computationally-Demanding Control Algorithms for Power Converters, *IEEE Transactions on Industrial Informatics*, Vol. 9, No. 3, pp. 1371–1379 (2013).

- [12] Canis, A., et al.,: LegUp: High-level synthesis for FPGA-based processor/accelerator systems, *Proc. of FPGA 2011*, pp. 33–36 (2011).

- [13] University of Illinois: clang: a C language family frontend for LLVM, available from \( \text{http://clang.llvm.org/} \).