# ディジタル・ハードウェア研究開発を題材とする PBL への取り組み A Trial PBL Using Digital Hardware R&D-Oriented Theme

山本 竜也<sup>†</sup> 橋本 浩二<sup>‡</sup> モシニャガ ワシリー<sup>†‡</sup> Tatsuya YAMAMOTO Koji HASHIMOTO Vasily G. MOSHINYAGA

文部科学省推進の下、IT 系ソフトウェア開発を主題材とする課題解決型学習(PBL)が全国の大学で実践されている. 我々は、これまでの PBL 型演習の実績を踏まえ、ディジタル・ハードウェア・システムの研究開発委託を題材とする長期 PBL 演習(修士1年、春~秋)を行った. この PBL では、研究室で取り組んでいる研究テーマの一つを題材として選び、教員が顧客となり、学生側は具体的な企画から実証システムの納品までを一貫して取り組んだ. 結果、従来のソフトウェア PBL との開発工程の共通点、差異点を明瞭化できた. また研究開発要素の強い課題を PBL の題材とするのは人材育成、研究活動推進に効果的であるとわかったが、様々な課題も顕わになった.

## 1. **はじめ**に

現在、日本では情報技術すなわち IT 分野における 人材が不足しており、その中でも特に、高度な専門性 を有するソフトウェア技術者の不足が大きな課題となっ ている.このような重要分野における人材の微弱性は, 日本の国際競争力にかかわる深刻な問題であり、学界、 産業界の双方から、早急に効果的な人材育成・強化シ ステムを構築する必要性が指摘されている. そこで, 文 部科学省は大学院を対象とした「先導的 IT スペシャリ スト育成推進プログラム」を実施している.これは、ソフト ウェアの研究開発現場で直ちに求められる基礎的ない し専門的な技術力・実践力に加えて,これからの社会 情勢の変化・IT の変容などに応じたソフトウェア開発に 先見性をもって柔軟に対処し,企業などで先導的役割 を担い得る実力を備えた「先導的 IT スペシャリスト」の 育成を行う拠点形成を支援・推進するというものである [1]. なおプログラムの実施は、大学単位で行うのでは なく,複数の大学がグループを形成し,グループで連 携して実施することとなっている.

本論文では、福岡大学における上記プログラム実施3年目となる2010年度に初めて実践した、ディジタル・ハードウェア・システムの研究開発委託を題材とするプロジェクト型開発演習(PBL: Project Based Learning)に

†福岡大学大学院 工学研究科 電子情報工学専攻 Graduate School of Electronics and Computer Science, Fukuoka University, Japan ‡福岡大学 工学部 電子情報工学科 Department of Electronics Engineering and Computer Science

Fukuoka University, Japan

ついて説明する. 以後この演習をハードウェア PBLと呼称する. この PBL の目的は,それまでに実施してきた PBLの目的に加え2つある. 1つ目は,ソフトウェア分野で実施してきた育成カリキュラムを活用しつつ,ディジタル・ハードウェア分野へと範囲を拡大させてみたときに,その効果を検証することである. 2つ目は,学生の研究分野と PBL の両立を図る,ということである. 業務請負型でシステム開発を行うという PBL のスタイルは,長期にわたって開発に取り組むことを学生に求める. そのため,大学院生の本分である研究活動の時間を確保しにくいという問題がある. そこで,学生が行ってきた研究開発テーマを請け負うというかたちを題材とするハードウェア PBL の実現を目指す.

以上を踏まえ、本論文では我々が試行的に取り組んだハードウェア PBL の概要、設計したシステム、開発工程について紹介した後、従来 PBL との比較、課題点について考察していく.

2章では、本学におけるこれまでのPBLの取り組みを 説明する. 3章では今回実践したPBLの概要、設計し たシステム、開発工程について説明する. 4章では、実 践したPBLの課題点を考察し、5章でまとめを行う.

# 2. 本学における PBL への取り組み

IT に「通信」を加えた ICT(情報通信技術)は産業・行政・社会の基幹として社会経済の様々な場面で使われており、今や産業および国家を支える中核技術となっている. 他方、我が国のICT分野においては、グローバルに市場を先導する欧米・新興国のICT企業から厳しい競争圧力を受け、勤務環境が厳しくなっていること

もあり、ICT の職業としての魅力が低下している. その 一方で、ICT 利活用の高度化が進むとともに信頼性へ の要求が非常に高まっているため、これに対応できる ICT 人材への需要が高まっている. とりわけ, ICT 企業 において上流工程を担うITアーキテクトやプロジェクト・ マネージャー, ICT 利用企業等において新たな付加価 値を創造することが期待される企業役員(CIO)等のい わゆる高度 ICT 人材の不足が顕著となっている[2]. こ のため、高度 ICT 技術者を国内において体系的に育 成することは、情報科学・工学系の大学・大学院修士 課程における重要な教育テーマの一つとなっている. そこで文部科学省は「先導的ITスペシャリスト育成推進 プログラム」の募集を行い、九州地区においては 2007 年度から九州大学が拠点大学となり,「次世代情報化 社会を牽引する ICT アーキテクト育成プログラム」が推 進されてきた.このような動向に対し、我々の所属する 福岡大学工学研究科·電子情報工学専攻(修士課程) も,遅れを取らないことが極めて重要であると判断し, 2008 年度よりこのプログラムに参加している[3].

本学ではプログラムの目標と特徴として、以下のように位置付けて取り組んでいる.

- 大規模なソフトウェア・システム開発に必要となるソフトウェア工学などの各種専門知識の習得

- ・ システム開発演習による実践的技術の習得

- PBL

- 実用に近いソフトウェア・システムの開発演習

- 学生数人でプロジェクトを構成し、役割を分担 しながら共同で開発

- ・ 九州大学大学院システム情報科学府との連携科目 の開講と相互単位互換

他大学と比較すると、PBLへの取り組みをはじめたのは遅い方であること、また、プログラムに参加可能な学生は修士課程学生のなかでも、主に IT 系ソフトウェア・システム開発に関係する研究室に所属する1年生に限られていたため、当初は小さい規模で始まった。それでも本プログラムを 2010 年度までの 3 年間進めてきたなかから、多様な成果を得ることができた。その一つは、学部カリキュラムの見直しである。 2011 年度より、学部生の講義としてソフトウェア・システム開発の実践力につながる講義科目を新設し、プログラミング関連の講義・演習の年次進行を修正した。また大学院においてもソフトウェア・アーキテクチャの講義科目が新設された。また、学部から大学院への進学を希望する学生に対して、本プログラムが魅了的なアピール・ポイントとして認

識されるようになった. 2011 年度は大学院進学者が増加しており,本プログラムを履修する学生数は今後,漸増すると思われる.

その一方で、様々な問題点も露呈した.一つは、本 プログラムが対象としている分野が実質的にソフトウェ ア・システム開発に限定した構成となっているということ に由来するものである. 今後, ICT システム構築全般に おいて、ソフトウェアとハードウェアの垣根が曖昧化して いくと予想される. 特に昨今, いわゆる「組込みシステム」 分野において,対象アプリケーションの広範囲化・高度 化が劇的に進行しており、ディジタル・ハードウェア技 術の発展がそれを後押ししている. そうした流れの中で, 九州大学をはじめとする多くの先進的な大学では,組 込みシステムのソフトウェア開発が PBL 演習テーマの 一つとして設定され、実績を上げている. だが、組込み システムの高度化・高性能化を実現するためには,必 然的にソフトウェア技術とディジタル・ハードウェア技術 とが密接に関連しあうことが必須である. 事実, 最先端 の組込みシステム機器,携帯端末,ICT 基盤通信シス テム開発等での、ソフトウェア-ハードウェアの垣根を越 えた高度な技術開発上の協調関係は周知のものとなっ ている. その範囲はアプリケーション, OS, ミドルウェア からファームウェアへ, さらにはディジタル・ハードウェア, システム LSI 設計へと至っており, 今後, 複数の領域に またがった能力を有する技術者の需要が高まることは 自明である.だが,これまで本学において推進してきた ICT アーキテクト育成プログラムでは、ソフトウェアとハ ードウェアのジャンルをまたがる優秀な技術者の育成 は到底不可能な状況にある.

もう一つは、半期にわたって実施される PBL と研究 活動の両立という課題点を克服できていないということ である. 情報工学系のなかでも例えば自然言語処理, メディア情報処理といったものを研究領域とするような、 主にソフトウェアを扱う情報系教員にとっては、PBL を 学生に経験させることでソフトウェア開発技術の向上が 見込め, 研究活動への波及効果が期待できる. また修 了後の就職先とPBL 演習テーマとの関連性も有してい ることが多いため、本大学における PBL 推進の原動力 として寄与してきた.しかし、計算機工学分野、例えば コンピュータ・アーキテクチャ, システム LSI 設計等やロ ボット制御分野等を研究領域とする情報系教員にとっ ては、IT 系のソフトウェア開発技術との関連性は低い. むしろ, 研究に必要となるハードウェア開発・制御技術 を習得するための時間を確実に削ぐことになり、地方私 立大学の研究能力低下が問題になっているなかで,研

究活動の貴重な戦力を PBL に奪い取られることになりかねない. そのため, 本プログラムに対しての否定的な意見は根強いものであった. それにもかかわらず, 専攻のカリキュラムとして(やや強引に) PBL を推進しているため, 情報系教員の間に亀裂が生じる懸念が出てきた. 学生の就職状況, という現実に目を向けてみると, 昨今の社会情勢化にあって, 専攻修了者の半数以上が IT系企業に就職しているにも関わらず, である.

そこで我々は、PBLのテーマとして組込みシステム、ハードウェア制御、あるいはハードウェア開発といった要素を取り入れることを提案した。研究推進上の多少の時間的ロスは避けられないとしても、PBLによる人材育成効果およびマネジメント能力向上効果により、結果的に、修士2年次において、研究活動の効率化を実現できるのではないかと考えたからである。また、同時に専攻内における教員同士の対立に発展しかねない芽を摘むことができると考えた。加えて、製品のライフサイクルが年々短くなっている今日において、ディジタル・ハードウェアやシステムLSI開発設計の現場でもプロジェクト管理能力が必要不可欠なものとなっている。そこで、そうした知識を兼ね備える人材を育成するノウハウを、情報工学系のハードウェア分野の教員が獲得する機会を得たいと考えた。

提案は認められ、2010 年度、ディジタル・ハードウェア・システム研究開発受託型 PBL を試行した.以後、この PBL をハードウェア PBL と呼称する. 開発テーマについては研究室教員から研究開発テーマを請け負う、すなわち受託することとし、教員が直接指導するのではなく、学生が主体的に開発プロジェクトを推進するという形をとった. 次章にて、そのハードウェア PBL の詳細を説明する.

### 3. ハードウェア PBL **の**詳細

# 3.1. 目的

ハードウェアPBLの目的として,以下の2項目を掲げることとする.

- 1. これまでのソフトウェア PBL を前提とするカリキュラムの延長線上で、ハードウェア PBL を実現可能かどうか、検証する.

- 2. PBL の題材に研究的要素を組みいれた「研究開発型 PBL」の実現を試みる.

項目1は、来年度以降もハードウェア PBL を実施することを考慮したものである. 学生たちは、実際の PBL に入る前に、顧客とのヒアリング方法、工程分析方法、仕様書・設計書の作成、作業工程管理の手法につい

・・・・マネジメント能力、コミュニケーション能力、仕様書作成 能力などシステム開発に必要な能力を養う講義科目 ・・・ハードウェア・アーキテクチャ、設計開発工程の進め方 など専門的技術指導を行う講義科目

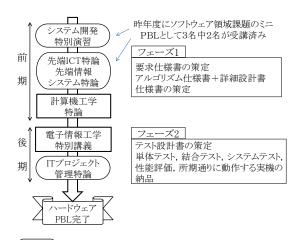

図 1. カリキュラム上での本ハードウェアPBLの流れ

て知っておく必要があるが、IT ソフトウェア開発とディジ タル・ハードウェア開発とでは、細部が異なっている. そ の PBL を一度行ってみて、差異点を実際に認識し、場 合によっては今後の課題として捉え, 講義内容の改善 を図ることを目的とする. 項目2については、学生の本 分として位置づけられている研究活動と PBL との両立 が本学においては困難であり、多くの時間を PBL 課題 の開発作業へ割かなければ納品に間に合わないという 事例が, 過去, 多発した. 一方で PBL を終えた学生は, スケジューリングやタスクの管理といった, PBL 演習で 培った業務遂行能力を研究分野に発揮させることがで きる. そこで, 研究室の研究テーマに関連した内容の ハードウェア・システムを開発するという PBL 演習内容 にすることで、研究への波及効果の獲得をも狙う. PBL に研究開発要素を取り込むことで, 学生たちが不安, 作業の取っ付きにくさを感じる可能性が生じるが、自分 たちが慣れ親しんでいる研究テーマを扱うことで, 開発 の基本となる技術内容の把握がしやすいという,一種 の安堵感を与えることも期待する.

## 3.2. 構成,期間,履修条件

複数人の修士課程 1 年次生からなる(今回は 3 人)でチームを構成し、顧客からの要求に基づくハードウェア・システムのプロトタイプを開発し納品する. 顧客、すなわち研究開発テーマの発注元は上級の専任教員が演じ、その教員は技術的アドバイス等を行わない. 企業での半導体・システム開発の経験を有する専任教員を

| 表1. PBL の体制 | 表1. | PBL | の体制 |  |

|-------------|-----|-----|-----|--|

|-------------|-----|-----|-----|--|

| チーム       | 修士課程1年生によるチーム(構成人員は3),チーム数は1.           |  |

|-----------|-----------------------------------------|--|

| 人数•構成     | 全員, LSI 論理回路設計・画像処理に係る研究室に所属.           |  |

| 指導体制      | 技術アドバイザ, 企業アドバイザ, それぞれ1名.               |  |

| プロジェクトの管理 | 学生が自主的に管理. 月に1回程度, 技術・企業アドバイザとのレビューを実施. |  |

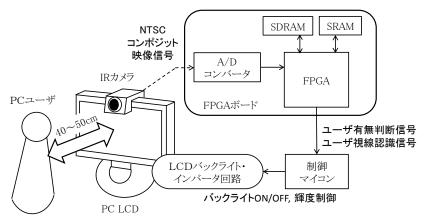

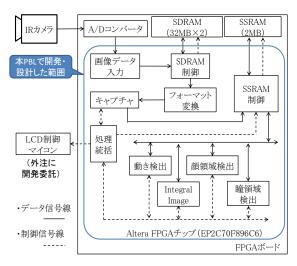

図 2. 本 PBL で開発するシステムの基本構成

技術アドバイザとして、企業からのアドバイザを非常勤教員として、それぞれ1名ずつ配置する.

最初に、顧客とのヒアリングで、与えられた研究開発テーマにおける要求分析を行い、要求仕様書と全体仕様書、アルゴリズム仕様書を検討し、まとめる(フェーズ1、実際の期間は5~7月).次に詳細設計・実装を行い、テスト計画を作成・実施する(フェーズ2、実際の期間は10月~12月).上記の各工程において時間、コスト、品質、人的資源などの管理を適切に行い、フェーズ2では、期日までにシステムを完成させ、設計書や操作マニュアルなどとともに、納品物の納品を完了させる.

本 PBL では、学生があらかじめ備えておくべき前提知識として、ハードウェア記述言語(HDL)を用いたハードウェア・システム設計、FPGA ボード上での回路実装に関する知識が最低限必要である。メモリへの画像データ格納や、ディスプレイへの出力など、周辺機器や画像処理に関する基礎的な知識を有していることも前提とする。また、「システム開発特別演習」(前期)と「IT プロジェクト管理特論」(夏休み集中講義)を覆修しておくことが、この PBL 演習科目の覆修条件である。本PBL の体制を表1に、カリキュラムの流れを図1に示す・PBL チーム・メンバー(3名)のうち2名は、2009年度にソフトウェア開発課題のミニ PBL(1年次前期:システム開発特別演習)を先行して受講した経験を有しているため、プロジェクト進行や仕様書作成といった、PBL を自律的に進めていくための基本的な要件は満たしてい

る. したがって、企業での製品開発経験を有するアドバイザ教員を配置することで、ハードウェア PBL の指導は十分に可能であると判断した.

教員サイドとしては、ソフトウェア領域 PBL とハードウェア領域 PBL とでの相違点(仕様書の作成スタイルや進捗管理の違い等)を把握し、同時に、研究開発型 PBL を進めていくためのノウハウを獲得することに意識を向けるようにした.

## 3.3. 開発テーマ

学生はいずれも、システムの低消費電力化を実現するシステム LSI に関連する研究を行っている。一例をあげると、カメラで撮影された、ユーザを含む画像データを記憶装置に蓄積した後、学生それぞれの研究テーマに沿う特定処理に基づき、ユーザの動線や顔領域などを検出する研究を行ってきた。具体的には、その一連の動作を実現するハードウェア論理回路の HDL 記述設計およびシミュレーションによる性能評価、FPGAボード上での実装、動作検証などを実施するといった研究あるいは低消費エネルギー画像処理フィルタ回路構成の研究である。そうした実績と個人の力量を吟味した結果として、「ユーザの視線認識に基づくディスプレイ電力管理システム」(画像処理・画像入出力ハードウェア・シスムの開発)を PBL の題材とした。

システムの構成概要を図 2 に示す.このシステムはディスプレイ注視者の動き検出・顔領域検出・瞳位置

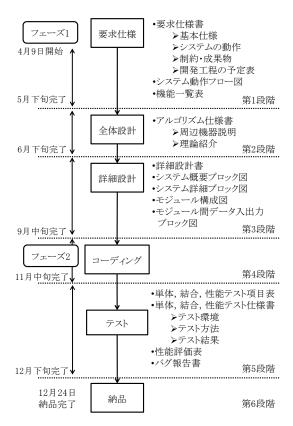

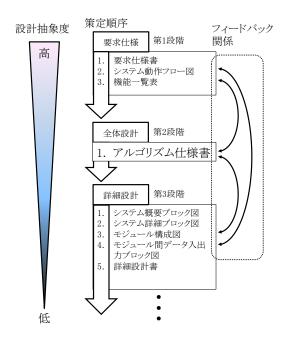

図3. 開発工程の流れ, 各工程の成果物

検出を一括して処理するものであり、また、システム内においてはソフトウェア処理を一切含まず、専用ハードウェア回路による画像処理を実現させる. 顧客に対しては FPGA ボード上での回路実装・納品・検証までを行うものとする. 演習のリアリティを醸し出し、学生たちに企業と同等の雰囲気と緊張感を与えるために、開発依頼の経緯を以下のように設定する.

- PC ディスプレイは、その使用者が画面を注視していない時間もバックライトが点灯し続けているため、消費電力を無駄に費やしている. 顧客は現在、PC 使用者の顔領域・瞳位置・瞳方向を検出することにより、実動作で消費電力を削減できるPC 液晶ディスプレイ(LCD)システムを研究開発している. LCD は小型埋め込みカメラ、画像処理回路、特別なバックライト制御系を備えるが、その画像処理系の開発は著しく停滞していた.

そこで当チームに対して、アナログ・カメラからの NTSCコンポジット映像信号を入力とし、A/D変換 および、画像処理を経てバックライト制御系への

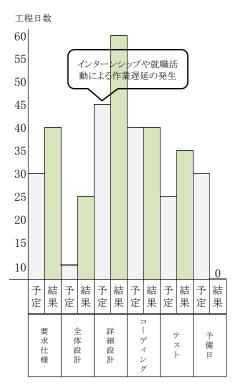

図 4. 工程日数の予定と結果

コマンド信号を出力するシステムを FPGA ボード 上に実現・納品するよう, 依頼があった. ただし画 像処理アルゴリズムはまだ大まかにしか決定して いないとのこと.-

画像処理アルゴリズムの基本的な事項は顧客から提示されるが、アルゴリズムの細部およびシステム・アーキテクチャの詳細については、顧客ーチーム間の折衝のなかで固めていくこととした。また下記に示すシステム構成の基本的要件が提示された。

- さほど複雑でない画像処理アルゴリズムでもって, PC 使用者 1 人を検出できるようにすること

- ・ 顧客が提供する安価な FPGA ボード(納品単価 5 万円以下)上に実現すること

- 0.5W 以下の消費電力でもって,動画像リアルタイム処理回路を実現すること

- ・ 部品単価3000円程度の安価なアナログ式近赤 外線白黒カメラ(IRカメラ)を用いること

一方で、顧客の役割を演じる専任教員が学生に対して、教員としての指導的態度を(うっかり)とってしまうと、学生たちが混乱してしまう。そこで顧客としての教員は、開発に用いる画像処理に関する技術知識を全く備えて

いないよう演じることとした. さらに, 画像処理アルゴリズムの検討・提案は学生が行い, 顧客が技術的に疑問に感じた点についても, 学生たちが丁寧に説明し理解を得ることを追加条件とした.

#### 3.4. 開発工程

本節では、ハードウェア PBL で執り行った開発工程 について、段階に分けて説明する. 開発工程の流れと 各工程の成果物を図3に、工程日数の予定と実際の結 果を表したグラフを図4に示す.

本学では、ソフトウェア PBL のノウハウしか持ち合わせておらず、また、チームのうち2名が昨年度、ソフトウェア・システムの開発をミニ PBL として実施した経験を有するにすぎなかった。それでも学生たちは、ハードウェア・システム開発を行う上で必要となるプロジェクトに対する意欲や目的・目標意識を有し、本ハードウェア PBL 実施提案に積極的であった。また、仕様書・設計書の作成技術、コミュニケーション能力、ハードウェア PBL で取り扱う各種部材に関する知識についても、ミニ PBL および過去の研究活動の経緯から、おおむね備えているものと判断した。よって、ヒアリング方法や要求分析方法、工程管理方法、開発工程の知識・技術、工程の組み方については、本学の既存カリキュラムをベースとし、実践を通して随時学習していく、という方針でもって本ハードウェア PBL を開始した。

前後期ともに、まず開発工程それぞれをチームで検討させ、アドバイザたちとのレビューを通して、工程それぞれの内容や管理方法を理解し、スケジュールの仮組を行った後に、アドバイザのゴーサインを得てから開発に臨んだ、アドバイザは、学生たちが提示した工程内容について、学習状況、バイタリティ、メンタリティを考慮しつつ、現実的に実行可能なところまで再検討させた。また、各工程で作成する設計書・仕様書といった成果物の内容については、工程の立ち返りが発生し成果物の見直しが必要になったとき、すぐに問題個所を理解できるようにするため、文章、図・表・グラフを工夫して、内容が平明になるような作成指導を行った。

工程の第1段階は、要求仕様書の策定である。顧客とのヒアリングから要求仕様をまとめたのち、システムの動作フローを検討し、動作フローチャートと機能一覧表の作成までを行った。動作フローチャートは、機能一覧表と照らし合わせることで、動作フローと機能の該当関係を視覚的に表すようにした。この工程を進めるにあたり企業アドバイザからは、顧客とのヒアリング方法や要求範囲の取り決め方、追加するべき項目など仕様書作成に関する指導を受けた。また技術アドバイザからは、

システムのアーキテクチャ,システム内部の処理アルゴ リズム・フローの考案など技術的要素の指導を受けた. そうした指導内容をもとに、学生たちは要求仕様書を 作成し、顧客に提示した.

続いて第2段階の全体設計では、システムを構成する FPGA ボード、IRカメラ、LCD 制御マイコンといった各種ハードウェア・デバイス類および、人物の瞳検出アルゴリズムについての説明文章を書き起こし、アルゴリズム仕様書を作成した。だが要求仕様書を顧客と取りまとめていく段階で、システム全体の構成や概要、必要となる機能や処理アルゴリズムをまとめあげてしまっていた。したがって本工程は、ソフトウェア・システム開発と異なり、システム構成図や E-R 図、機能一覧などの、ユーザ要件を満たすための基本的な仕様を定義する基本設計(外部設計)とはならなかった。このことは、学生たちが当初想定していた第1段階-第2段階工程の境界線の曖昧化を引き起こし、スケジュールの遅延を招くこととなった。

第3段階の詳細設計では、システム全体の入出力の接続構成をブロック図で示し、処理が集約されているFPGA チップの中を、メイン処理ブロック、制御ブロック、カメラ・ブロックに分け、チップ内のデータ入出力関係を表す概要ブロック図を作成した.次に、概要ブロック内部を構成する内部回路モジュールの間を信号入出力線で接続し、データ入出力関係図を作成した.この作業過程を経ることで、システムへの目線を最上位から最下位へと段階的に落とすことができ、外部との入出力関係から内部回路モジュール間の入出力関係まで、正確に把握することができた.これにより、詳細設計書を作成しやすくなるという効果が得られた.

第 4 段階では、詳細設計書をもとに、内部回路モジュールおよび接続回路などの論理回路記述作成(HDLコーディング)作業を行った。

第5段階では、初めに、システムのメイン処理、制御、外部接続といった個々の機能を担う下位モジュールそれぞれで単体テスト項目表を作成した.次に、項目表をもとに単体テストベンチを作成し、HDLシミュレーションによって、各下位モジュールの信号入出力の動作確認を行った.動作確認では、組合せ回路部分については、入力信号パターンをすべて列挙し、それに応じた出力パターンを確認した.順序回路部分については、状態遷移機械の動作に従ったデータの入出力を確認した.チーム・メンバーは、それぞれの担当部分が期待値通りかどうかをテストした後に、テスト・ミスが無いか調べるために、残りのメンバーが同様のテストを行った.

続いて結合テストでは、トップ・モジュールと下位モジュ ールを統合し、FPGA コンフィギュレーションを行ってか ら, バックライトを制御可能な特殊 LCD および LCD 制 御マイコンを除いて、システム動作検証を行った.シス テムのデバッグ環境は IR カメラ, コンフィギュレーション 済みの FPGA ボードおよびデバッグ出力ディスプレイで 構成される. デバッグ出力ディスプレイにはIRカメラか らの入力画像を処理した結果画像が表示される. また FPGA ボード上の 7 セグメント LED 表示により, 内部機 能が正常に動作しているか判別できる.このようなデバ ッグ環境により, 結合・性能テストにおける観測の容易 化を図った. そして結合テストの項目表を作成し, 期待 通りの基本動作を検証するための統合テストを行った. その後の性能テストでは、10名の被験者の協力のもと、 要求仕様の環境下においてシステムが正常に動作す るかどうかのサンプリング調査を行い,正常検出成功率 を計算した. ここまでの作業で, 要修正箇所が発見され たときは、その内容をバグ報告担当者へ通達し、担当 者は、バグ発生理由や修正方法を日付入りで管理した. 修正作業に伴って要求仕様書の書き直しが必要にな ったときは、その旨を顧客へ速やかに報告し、改善案 の提示および許可を得てから修正した. そのほか, 詳 細設計書への修正が必要なときは、チーム内レビュー で報告し, チーム全員が状況を認識したうえで, 詳細 設計書およびシステム内部の修正を施した.

最後の第 6 段階では顧客立会いのもと、システムの動作をプレビューし、期待通りの動作をしているか、制約は満たしているかといったレビューを実施した後、納品物を引き渡し、PBL 演習完了となった.

以上が, 開発工程の概要である. 顧客からは当初, これらの工程を数か月以内で完了させるようにという要 求がなされていたが、実際は、大幅に日数を超過した. その原因は複数挙げられるが、最大の原因は、顧客が 当初想定していた作業工数の見積もりが著しく不合理 であったことと、チーム・メンバーである学生の技術習 熟度のばらつきは当初想定していたよりも大きかったた め,作業工数の見積もりには当初より大きな誤差が存 在していたためである. 2つ目の原因は, 詳細設計のフ ェーズ 1 終了間際から、インターンシップや就職活動と いった学生個々人の重要な予定が増えたことである. ミ ーティング予定日にチーム全員が揃わないことや,チ ーム全員が丸一日作業に従事できない, といった事態 が発生するたびに,工程日数を検討し直し,細かなス ケジュール調整を強いられた.3つ目の原因は、各工 程の理解を始めとして仕様書・設計書の度重なる加筆 修正に加えて、FPGA デバイス、イメージセンサー、A/D コンバータ LSI、DRAM、SRAM といった各種半導体デバイスに関する技術的資料の読解、および回路設計方法の検討で想定外の時間を要したことである。このことは各工程それぞれでの大幅なスケジュール遅延を招いてしまった。結果、PBLをフェーズ1とフェーズ2とに分割実施せざるを得なくなり、計7か月以上の開発期間を費やしてPBL演習は完了した。

#### 3.5. 開発システムの波及効果

このPBLで完成したプロトタイプ・システムは、顧客から要求された機能をすべて満足し、アルゴリズム処理は機能的には正常に動作した.しかし、検出精度が低いことが性能テストにより判明した.原因は、顔領域検出処理とカメラ距離、背景の違いにより、システムの不安定な動作を生み出していたことによる.このため、性能テストの時点では、このシステムの実用性は低いという評価を結論とせざるを得なかった.

そこで PBL 終了間際, 学生たちは独自にアルゴリズムを根本的に見直し, 顔領域検出機能の再構築および内部制御ロジックの修正を行い, 検出精度の向上を実現可能な性能改善策を取りまとめ, 顧客にサービスとして提示した. PBL 終了後, チーム・メンバーのうち 2名が性能改善作業を引き継いだが, 1か月弱で飛躍的に精度を上昇させることができた. さらにその後, メンバーの1名が引き継いで研究活動を進めた. 結果, 回路規模と消費電力の低減および検出精度の上昇を実現できた. また, その成果を学会で発表した[4].

PBL の成果物として多くのドキュメントがもたらされるということは、その研究活動あるいはその成果物を後進に引き継がせていくのに大変有用であると考えられる。また、数年以上の長期的な視野での、システム開発を伴う研究テーマの場合、その研究基盤(プラットフォーム)の構築を PBL 形式で取り組むことにより、その後の研究活動の効率化・研究促進効果が期待できると考えられる.

# 4. ハードウェア PBL の課題点

#### 4.1. 解決すべき課題

前章まで、スケジュールの遅延や各工程の困難さな ど表面的な問題を述べてきたが、実際のところ、人間関 係など内面的な問題も多く発生していた.

1 つ目は、システム開発を適切に指揮可能なプロジェクト・マネージャーが不在であったために生じた問題である. プロジェクト・マネージャーには、顧客とチーム、またはチーム内で発生する人間関係の問題を解決し、

良いチームを育成するための環境を作り、そして、プロジェクトの方向性を常に適切に保つことが求められる。 そして学生の学習効果すなわち PBL チームの業務達成能力向上効果は、その環境に大きく依存するといえる。一方で、PBL のように少人数メンバーで構成されるプロジェクトの場合、メンバー個々の体力・精神的な影響をダイレクトに受けやすいという特徴がある。

だが今回のハードウェア PBL では開始当初から、ス ケジュールおよびプロジェクトの方向性の点について、 顧客との深刻な対立が生じていた. 加えて, 工程成果 物作成の過程で2人のアドバイザの意見が分かれたた め、混乱を招いてしまったりした。さらには、チーム内で の作業負荷が偏ったことによる不平不満が発生した. そのようなことが、プロジェクト・チームの目標達成への 意欲や作業の意欲を大きく変動させ, 仕様書・設計書 に残る曖昧さや規約に沿わない間違ったコーディング といった、未然に防ぐことができたはずのミスが多発し た. プロジェクト・マネージャーの基本的な役割は, チ ーム内のオープンなコミュニケーションの土壌を整える ことにある. 特に研究開発要素を含む PBL を推進させ るには、プロジェクトの方向性およびモチベーションの 適正な維持管理が特に重要であることがわかった. そ のためには、演習期間にあわせた適切な課題サイズか つ, 目標が演習途中で揺らぐことのないよう, 顧客との 要求仕様打ち合わせの議論を十分に深めておくことが 重要である. また学生が不信感を一切抱かないよう, 顧 客・教員・アドバイザのなかで指導方針を突き詰めて検 討し、固めておくことが求められる.

2 つ目は、開発工程の構成および各工程での作業 内容での問題である. 開発工程の問題は前章で述べ たとおり、各工程で実施する作業では様々なトラブルが 続き, 工程スケジュール遅延が発生した. 今回実施し た研究開発型ハードウェア PBL は試行的な取り組みで あるため、PBL を進めるなかで生じてくる問題を明らか にしつつ解決を図っていくという、実践学習体制として いた. したがって学生たちは、各開発工程について理 解と学習を深めつつ,作業を進めていった.だが学生 たちは、ソフトウェア PBL の知識しか備えていなかった ため, ハードウェア分野とソフトウェア分野とで仕様書・ 設計書の記述スタイルが異なるということに戸惑い、工 程進捗の遅延の一原因となった. 例えば第5段階のテ スト工程では、8 ビットの入力信号パターンに合わせて 出力を行う組み合わせ回路のテスト項目を作成する場 合, 256 通りの入力信号パターンと, 出力信号パター ンを確認できる項目表が必要となる. ソフトウェアのテス ト工程と比べると、ハードウェアは複雑な入力に対する出力の組み合わせや、膨大な信号データを取り扱う、したがってテスト項目を正確に効率よく確認できるよう、仕様書の記述方法を工夫したりすることが求められるのだが、回路によってはテスト規模が非常に大きくなるものがあり、学生たちは、理解しやすいテスト項目表の考案に頭を悩ませることとなった。また、本 PBL は今後のハードウェア PBL の指標となるべく、課題内容・規模ともにチャレンジ的性格を備えているため、成果物である仕様書・設計書の規模も大きくなった。

さらに本 PBL 研究開発的要素を含むため,予期していなかった問題の発生に際して,その原因調査および改善策の提示が必要になるなどしたため,最終的にスケジュールの大幅な遅延を招いた.このスケジュール遅延は課題そのものに起因し,本質的に不可避であるとはいえ,それをできるだけリカバリーできるよう,開発工程構成上の仕組みを検討し,今後の PBL 事前学習カリキュラムに盛り込むことが求められる.

## 4.2. 重層ウォーターフォール・モデル

今回実践したハードウェア PBL の開発工程は、広域 で見ると, 現工程が完了した後に次工程に移るため, 開発工程モデルは,基本的にウォーターフォール・モ デルであるといえる. また, ある工程で複数の成果物を 作成する場合は、最初の成果物の作成し終わるまで、 次の仕様書・設計書に取り掛かかることができず、複数 の成果物を同時作成することが極めて困難である. つ まり狭域で見るとさらにウォーターフォール・モデルとな っていることがわかる(図 5). 例えばソフトウェア・システ ム開発では,ウォーターフォール・モデルだけでなく,ス パイラルモデルや反復型といった開発手法が存在し、 開発対象となるシステムに応じて, 最適な手法を選択 することができる.またアクティビティ図やクラス図,ユー スケース図といった成果物は、それぞれが独立した使 用目的を持っているため、同時並行で作成できる. そし て仕様の変更など、工程を立ち返る際のフィードバック を繰り返し、逐次対応をしていくことができる.

しかし、今回のようなハードウェア・システム開発では、一部の独立した項目(たとえば抽象的なテスト項目検討など)を除き、広域狭域ともにウォーターフォール・モデルとならざるをえないことがわかった。事実、詳細設計工程で起きた時間ロスを取り戻そうとして、システム概要ブロック図とシステム詳細ブロック図を同時並行で作成してみたところ、ブロック図どうしの接続関係の整合性を確認するために、何度も仕様書を照らし合わせなければならなかった。さらに、システム概要ブロック図

図 5. ハードウェア・システム開発工程の詳細

で要修正個所が発生するたびに、同時並行で作成していたシステム詳細ブロック図の加筆修正を行わなければならず、作業がいっこうに進まなかった。そこで、詳細設計工程全体を見直し、システム概要ブロック図を作成した後に、システム詳細ブロック図を作成するというように方針を転換したところ、上記のような問題は発生しなくなった。

以上のことから、今後ハードウェア PBL を実施する際、ソフトウェア開発で一般的に使われる開発工程モデルをそのまま適用することは難しく、自然と重層ウォーターフォール・モデル的開発とならざるを得ないということに注意しなければならない、したがって、仕様の変更等が発生した時、時間的にも労力的にもコストがかかることは避けられないということを、教員側は学生たちに強く意識させることが重要である。

#### 5. **まとめ**

学生たちは、顧客との意思疎通の困難さや、スケジュール通りに工程を進めるために必要な進捗管理方法といった経験を、本学において実施したディジタル・ハードウェア研究開発を題材とする PBL 演習カリキュラムを通して学ぶことができた。学生個々の研究活動に関係したテーマを題材とすることで、PBL 演習が終了した後も、システム改良を行い、性能を向上させるとともに、さらなる研究活動への発展を実現できた。また教員は、

ソフトウェア領域 PBL とハードウェア領域 PBL とでの相違点, 研究開発型 PBL を進めていくためのノウハウをいくらか獲得できた.

一方で, 顧客を演じた教員およびアドバイザを演じた 教員の問題, 演習課題の開発規模, スケジュール管理, ソフトウェアとハードウェアとでの開発工程の違い, とい った問題により、PBL 進行が大きく遅延する結果となっ た. 当初, 4月~7月までの3か月弱の研究開発で, 要 求仕様書設計から納品まで行ってほしいという、実行 不可能な要望が顧客から提示されていた. また, 開発 工程を進めるにつれて、PBL 演習課題の規模が少々ス ケジュールを調整したとしても過大であることが明らか になった. そこでフェーズ 1 とフェーズ 2 に分離した長 期の演習カリキュラムとして仕切り直し、12 月の末まで 延長して PBL 演習を行ったが, 学生からの強い要望に より、教員サイドは時間が許す限り打ち切らないという 方針で、最後まで取り組むことができた. 結果的に、開 発に要した期間は約7か月となってしまったものの,今 回のハードウェア PBL の成果物目標はおおむね達成 できたといえる.

我々は現在、研究開発要素を含む組込みシステム全体(=ハードウェア+ソフトウェア)の開発を PBL のテーマとして本格的に実施することを検討中であるが、ソフトウェア領域 PBL はこれまでに何度も実施済みであり、いくらかのノウハウを蓄積している。そこで今回は、潜在的に高い開発ポテンシャルを有する学生 3 名に対し、比較的大きな課題規模の研究開発要素を含むハードウェア領域 PBL を実施したことで、将来起こり得る問題点をある程度あらわにできたと考えている。そこで 2011年度後期において、さっそく、課題規模は小さいものの、マイコン・センサ回路の開発設計を含む、研究開発型の組込みシステム PBL を開始したところである。ソフトウェアとハードウェアとで開発工程の適正モデルが異なるため、二つをどう協調・推進させていくかについての知見を得たいと考えている。

さらに将来の展望として、本大学の場合、ハードウェアとソフトウェアがそれぞれ 1 チーム以上の、複数のチームが共同分担して大テーマ PBL に取り組むことで、学科規模での研究活動の活性化と学生のモチベーション向上を図ることができるのではと考えている。

# 開発システムの紹介

本 PBL で開発したシステムのアーキテクチャを図 6 に示す. 顧客から要求された機能は大きく 2 つである.

図 6. 開発システム・アーキテクチャの概要

1 つは、PC ユーザが動いたかどうかを検出する機能であり、2 つは PC ユーザの瞳領域を検出する機能である。 それら 2 機能は FPGA ボード上に実装され、FPGA ボードからの制御信号出力に基づき、LCD 制御マイコンは PC LCD のバックライト電源・輝度状態を制御する。 FPGA ボードには 1 個の FPGA チップ、SDRAM、SSRAM、A/D コンバータが集積されていて、IR カメラと LCD 制御マイコンが外部接続される。IR カメラからの NTSC コンポジット映像信号は FPGA ボード上の A/D コンバータを経由し、FPGA チップ内部の「画像入力 I/F」でデータ整列されたのち、ピクセル・データとして SDRAM に全画像フレームが格納される。

FPGA チップ内部では、まず「処理統括」ロジックの 制御下にある「キャプチャ」ロジックが 0.25 秒毎に画像 フレームを取り出し、「フォーマット変換」にて RGB デー タへと変換してから 320×240 のサイズに縮小されて SSRAM に格納する. 次に、「処理統括 ロジックは「動き 検出」,「Integral Image」,「顔領域検出」,「瞳領域検 出」,「SSRAM 制御」をそれぞれ制御して,ユーザの動 きと瞳領域検出処理を実現する. 具体的には「動き検 出」ロジックでは、2枚の画像データの差分からユーザ が動いた範囲を検出する.「Integral Image」ロジックは その検出範囲内で、顔・瞳領域検出を行うための画素 値の総和と平均値の高速計算を担う.この計算結果を 基に「顔領域検出」ロジックが, 人間の顔領域の特徴を 生かした 6 分割矩形フィルタ処理を行い, 顔領域候補 を検出する. そしてさらに「瞳領域検出」ロジックがユー ザの瞳部分を検出する. 最終的な処理結果はユーザ の動きを判別する信号と、瞳領域を検出したかどうかの 2 種類の信号として, LCD 制御マイコンへ出力され, 最終的にバックライトを制御する. システムの詳細および 改良アルゴリズムの詳細は[4]に記している.

# 参考文献

- [1] 文部科学省, "先導的ITスペシャリスト育成推進 プログラム(平成 18 年

- 度)"\http://www.mext.go.jp/a\_menu/koutou/it/ h18.htm\(2011/07/06 現在)

- [2] 総務省, "第8回 高度ICT人材育成に関する 研究会(平成20年5月23日)"

- <a href="http://www.soumu.go.jp/main\_sosiki/joho\_tsusin/policyreports/chousa/ict\_ikusei/080523\_2.html">http://www.soumu.go.jp/main\_sosiki/joho\_tsusin/policyreports/chousa/ict\_ikusei/080523\_2.html</a> > (2011/07/06 現在)

- [3] 福岡大学大学院 工学研究科 電子情報工学専攻, "平成22年度 先導的IT スペシャリスト育成推進プログラム 実施報告書", pp.1-21, 2011年4月.

- [4] 安藤智晃,橋本浩二, Vasily G. Moshnyaga, "使用者瞳認識によるディスプレイ電力管理システムの FPGA 実装",第24回 回路とシステムワークショップ,pp.437-442,2011年8月.