# FPGAによる省電力計算機の開発評価環境の試作

高橋昭宏†1 小 林 弘 明 <sup>†1</sup> 坂 本 龍 一 †1 美太郎 †1 未来子 †1 中村 宏†2 並木 佐藤 英 晴<sup>†3</sup> 天 宇佐美 公良 †4 章 †5 佐々木 広 †2 沂 藤 正

### 1. はじめに

プロセッサも同時に並行して研究開発している様なシステムソフトウェアの研究において、信頼性の高い実機検証の環境を短期間で構築することは難しい。実際にはシミュレーションを用いてプロセッサとシステムソフトウェアを検証する場合が多く、簡易的なOSあるいはOSを搭載せずにベンチマークプログラムを実行して評価するに留まっていることが多い。しかし、実環境に近い Linux 等の規模の大きな汎用OSを用いた評価などは、割り込み処理や入出力装置の実装、シミュレーション時間などが問題となり難しい。

本研究では、システムソフトウェアの方式評価環境として、FPGAを備える評価ボード上に細粒度パワーゲーティング機能(以下PG)を備えたプロセッサコアを含む計算機環境を実現し、プロセッサと OS とが連携する省電力向けシステムソフトウェアの評価を行っている。本稿では、FPGA評価ボード上に構築した省電力計算機環境の仕様と実現方法を示し、その計算機環境上で構築したシステムソフトウェアを紹介する。

# 2. システム構成と FPGA 開発環境

### 2.1 システム概要

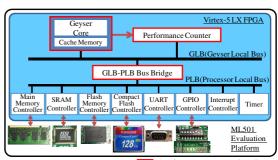

図1に、本研究で試作したシステム構成を示す。省電力プロセッサとして、MIPS R3000の演算ユニットに細粒度 PG 機構を有する Geyser アーキテクチャ<sup>1)</sup>を FPGA で実現している。Geyser コアには、TLB、キャッシュメモリ、MMU、3 章に示す省電力機構を実装している。その他、表1に示す主記憶、SRAM、Flash Memory などのメモリ資源、タイマ、UART、Compact Flash (CF) などを備えている。また、PGによる電力削減効果を推算するためのスリープ頻度の計測用カウンタ、キャッシュミスを計測するためのカ

:本研究でVerilog-HDLで作成した部分

図1 FPGA 開発環境のシステム構成

| 表 1 Geyser on FPGA 仕様 |              |                        |

|-----------------------|--------------|------------------------|

|                       | FPGA ボード     | Xilinx ML501 (VIRTEX5) |

|                       | Geyser コア周波数 | $40 \mathrm{MHz}$      |

|                       | キャッシュメモリ     | 命令 8KB , データ 8KB       |

|                       | 主記憶          | DDR 256MB              |

|                       | SRAM         | 1MB                    |

|                       | FlechDOM     | 29MD                   |

ウンタなどを実装している.

# 2.2 FPGA 開発環境とプログラム開発

Geyser コアとパフォーマンスカウンタを Verilog-HDL を用いて記述している. なお, 主記憶, I/O 等の実装には Xilinx 社製の Embedded Development Kit(EDK)<sup>2)</sup> の IP コアを用いている. 既存の IP コアを用いることで, ハードウェアの開発効率を向上できる. さらには, OS のデバイスドライバも流用できる利点がある. 筆者らの設計した GLB(Geyser Local Bus) と Xilinx 社の開発環境が用意している PLB(Processor Local Bus) とを作成したバスブリッジを介して接続した. 以上のモジュールを Xilinx 社の Integrated Software Environment(ISE) を用いて論理合成し, Xilinxの評価ボード ML501<sup>3)</sup> 上に実装した.

本 FPGA の開発環境で実行するシステムソフトウェアおよびプログラムは、ホスト計算機で MIPS 用 GCC クロスコンパイラでコンパイルし、バイナリをコンソールから本評価ボードへ転送して実行する。また、本評価ボード用の CF ドライバを作成して開発効率を向上

<sup>†1</sup> 東京農工大学

<sup>†2</sup> 東京大学

<sup>†3</sup> 慶應義塾大学

<sup>†4</sup> 芝浦工業大学

<sup>†5</sup> 電気通信大学

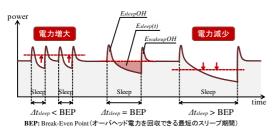

図2 パワーゲーティングを行ったときの電力推移

させると共に OS のブートロードを可能とした.

## 3. Geyser の省電力機構

本環境の Geyser プロセッサは本来は実チップにより実現される. FPGA での実装では、PG による電源 遮断は実際に行わないが、PG 機構は実装しており、テストと評価に利用できる.

図 2 に細粒度 PG を行ったときの電力推移を示す。図 2 左部のように、短期間で演算ユニットのオン・オフが繰り返された場合は、オーバヘッド電力  $(E_{sleepOH} + E_{wakeupOH})$  が、削減したリーク電力  $(E_{sleep(t)})$  より大きくなってしまう。そのような場合は、PG を適用せずにオーバヘッド電力の発生を抑制する工夫が有効となる。Geyser では、(1) コアが使用しない演算ユニットへの電力供給を自律的に遮断する PG モード、(2) キャッシュミス時にのみ演算ユニットへの電力供給を遮断する PG モード、(3)PG を行わないモード、のいずれかをソフトウェアから設定可能である。また、命令のオペコードにも PG 制御情報を付加して上記モードを制御する機能も備えている.

# 4. OSによる省電力制御方式の評価環境

本研究では 3 章の省電力機構を用いて、システムソフトウェアにおけるプログラムの静的解析・動的解析により PG を制御する各種方式を提案している $^{4)\sim6}$ )、本章では、Linux および組込み向け GeyserOS における制御方式を紹介する.

#### (1)Linux における PG 制御方式<sup>6)</sup>

本開発評価環境では、I/O や割り込み機構を実現することで Linux カーネルにおける評価環境を実現した。Linux での省電力制御では、Linux プロセススケジューラにおいて、電力的に不利になる PG がどの程度あるかをプロセス切替え時に動的に算出し、最適な省電力モードをプロセスごとに設定している。本開発評価環境において、PG を制御しない場合に比べてスリープ時平均リーク電力およびエネルギー遅延積の削減効果を確認した。

## (2)GeyserOS における温度情報の適用制御方式<sup>5)</sup>

コア温度により BEP 値が変わることを考慮し、電力オーバヘッドを減少させるようスリープ時間粒度に

応じた閾値温度を設定し、これを基に OS が省電力 モードを設定する方式である。本開発評価環境上にコ ア温度エミュレーションをソフトウェアで実装し、閾 値温度を決める二つの手法を OS へ実装して平均リー ク電力の削減効果を示した。

# (3) コンパイラと OS との協調制御方式 $^{4)}$

Geyser 向けコンパイラ<sup>7)</sup> により PG 制御情報を含むオブジェクトコードを温度ごとに生成しておき,OS が実行時のコア温度の変化に基づいて動的にこれらを切り替えて実行する方式である。本開発評価環境上でベンチマークプログラムを用いた提案機構の評価実験を行い,提案手法の有効性示している.

本開発評価環境により(1)~(3)を実装,評価し,OSの方式検討の段階でマルチタスク制御,省電力モード制御を例外・割込みを契機として行えた.OSの処理オーバヘッドを含めてベンチマークプログラムを用いた方式比較評価を実機上で,より正確に短期間に行い方式提案ができることは大変有効である.

#### 5. おわりに

本稿では、FPGA評価ボード上に実現した省電力計算機の開発評価環境およびOSの研究成果を示した. 本ポスターではFPGAの評価ボードを展示する.

謝辞 本研究は、科学技術振興機構「JST」の戦略的創造研究推進事業「CREST」における研究領域「革新的電源制御による次世代超低消費電力高性能システム LSI の研究」によるものである.

### 参考文献

- 1) N. Seki et al, "A Fine-grain Dynamic Sleep Control Scheme in MIPS R3000", Proc. of the 26th IEEE ICCD-2008, pp. 612–617(2008).

- 2) Xilinx, "Embedded Development Kit (EDK)", Available via WWW: http://japan.xilinx.com/ support/documentation/dt\_edk.htm

- 3) Xilinx, "ML501 Reference Design", UG227, vol. 1.0(2007).

- 4) 小林 弘明他, "OS における細粒度パワーゲーティング向けオブジェクトコードの実行時管理機構の研究", IPSJ 2011-OS-117, No. 1, pp. 1-8(2011).

- 5) 木村 一樹他, "コア温度の変化に適応する OS による細粒度パワーゲーティング制御方式", IPSJ 2011-OS-117, No. 30, pp. 1-8(2011).

- 6) 高橋 昭宏他, "細粒度パワーゲーティング制御による省電力化を行う Linux プロセススケジューラの試作", IPSJ 2011-OS-117, No. 31, pp. 1-8(2011).

- 7) T. Komoda et al, "Compiler-Directed Fine Grain Power Gating for Leakage Power Reduction in Microprocessor Functional Units", 7th Workshop on ODES-2009(2009).