# [招待講演] 3D 積層フレキシブルメモリ

# 斎藤 英彰†

**あらまし** 近年、プロセス微細化の限界を打破するために3次元実装技術を使った3次元集積デバイスの研究開発が盛んになっている。本講演では3次元実装とメモリ動的再構成技術を使った新しいメモリである積層フレキシブルメモリについて、そのアーキテクチャとプロトタイプ動作について紹介する。

# 3D chip-stacked flexible memory

# Hideaki Saito<sup>†</sup>

**Abstract** Recently, 3D integration has been intensively investigated as a technology for overcoming a limitation of p rocess scaling. In this meeting, I introduce new memory architecture, chip-stacked flexible memory, which has the 3D integration and a dynamic reconfigurable memory technology.

# 3D積層フレキシブルメモリ

日本電気株式会社 デバイスプラットフォーム研究所 斎藤 英彰

#### 3D集積の特徴

- 高集積度

- チップ実装あるいは半導体層のプロセス積層で高さ方向に集積

- DRAM, Flashの積層で大容量メモリ実現が近い

- ↓ 小型パッケージ

- Si貫通ビア(TSV)で裏面配線してパッケージを小型化

- イメージセンサですでに実用化

- | 高性能

- チップ内の長距離配線を3次元の短距離配線に置き換え

- 回路遅延、消費電力の向上を期待

- | システムインテグレーション

- 異種デバイス、異種プロセスチップの積層によるシステム統合

- ロジック(プロセッサ)とメモリの積層の応用検討が活発

- 積層フレキシブルメモリ: システムLSIのロジックとメモリの分離、チップ積層

| Page2 | NECC onfidential | Empowered by Innovation NEC |

|-------|------------------|-----------------------------|

|-------|------------------|-----------------------------|

©2010 Information Processing Society of Japan

<sup>&</sup>lt;sup>†</sup> 日本電気株式会社 NE C Corporation

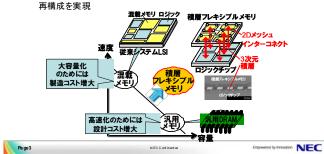

## 積層フレキシブルメモリの開発

| 高速性能と大容量性能の両方を兼ね備える新しいタイプのメモリ | 特徴

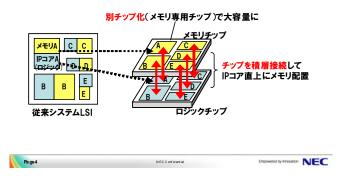

- システムLSIからメモリ部分を分離して独立のチップにし、3次元実装

- メモリチップをメモリタイルと2次元メッシュ・インターコネクトで構成し、メモリー

東機式を実現

# 技術①: 3次元実装技術

⇒システムLSIの中の混載メモリを別チップ化して大容量化し、近接積層

# 技術②: メモリ再構成技術

多数の小規模メモリをチップ内のインターコネクト網で結合

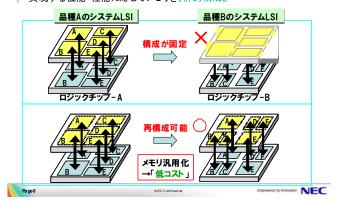

## 多品種のシステムLSIで共通で使える『汎用化』

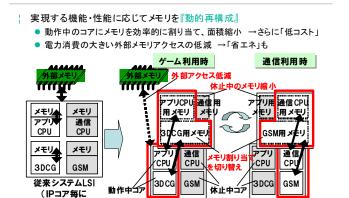

| 実現する機能・性能に応じてメモリを『静的構成』

Empowered by Innovation NEC

## メモリの利用効率の向上も可能

新しいアーキテクチャのシステムLSI NEC

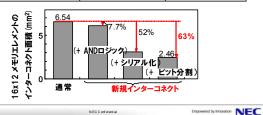

#### 再構成機能の面積オーバーヘッドを削減

- ↓ メモリ特化型インターコネクトで面積オーバーヘッド削減

- 12×16 MEのレイアウト

Page8

メモリを確保)

| 2Dメッシュインターコネクト構成        | 通常インターコネクト (面積削減策なし) | 新規インターコネクト |  |  |

|-------------------------|----------------------|------------|--|--|

| レイアウト面積 ((a)+(b)) [mm²] | 22.20                | 18.12      |  |  |

| (a) SRAMマクロ合計           | 15.66                | 15.66      |  |  |

| (b) 2D メッシュインターコネクト     | 6.54                 | 2.46       |  |  |

| 6.54<br>7.7% 594        |                      |            |  |  |

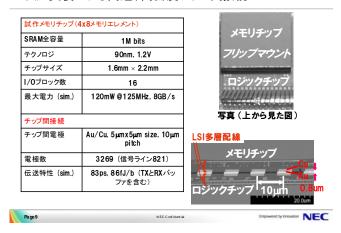

## 3次元実装による高速、高密度チップ間接続

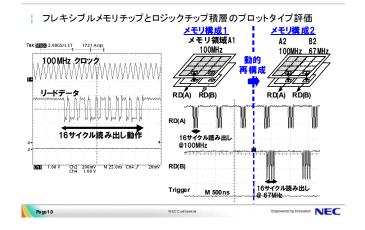

## プロトタイプの動作波形