# Regular Temporal Logic Expressively Equivalent to Finite Automata and Its Application to Logic Design Verification

Hiromi Hiraishi\*, Kiyoharu Hamaguchi\*\*, Hiroshi Fujii\*\*\*

and Shuzo Yajima\*\*

Due to the progress of VLSI technologies, logic circuits have become more complex. As a result, the possibilities of design errors have increased. Logic design verification, therefore, has become more important as a means of guaranteeing the correctness of logic degign. Logic design verification requires mathematical logic with enough expressive power to describe the behavior of logic circuits. While propositional logic is known to be equivalent to combinatorial logic circuits, a class of mathematical logic that corresponds to sequential machines and/or finite automata has not yet been clarified.

This paper introduces various types of Regular Temporal Logic (RTL), which is expressively equivalent to finite automata and can express the notion of time explicitly. A design verification algorithm for sequential machines based on a model-checking method of the RTL is also given. Although the complexity of the model-checking problem of the RTL is non-elementary, the proposed model-checking algorithm is efficient and still runs in a time proportional to the size of the structure models. An RTL model checker based on the proposed algorithm is implemented, and it is shown that it can determine whether the designs for medium-size sequential machines allow them to satisfy their specifications in a reasonable time and space.

#### 1. Introduction

With the progress of VLSI technologies, the designs of logic circuits are becoming more and more complex. As a result, the possibility of design errors is increasing, and this greatly affects the development cost and time. It is therefore important to establish new logic design methodologies that make it possible to verify the correctness of logic design.

Conventional logic simulations do not meet this requirement because they cannot guarantee correctness of design except for the input patterns simulated. To guarantee the correctness of a design, we need to prove it formally by describing its specification/design and verifying its correctness according to some formal mathematical logic.

Although propositional logic is known to correspond to combinatorial logic circuits, we currently have no finite mathematical logics that correspond to sequential circuits and/or their mathematical models. The construction of such mathematical logic systems is strongly

desired not only in the field of logic design verification and concurrent processes but also in the field of mathematical logic itself.

As a mathematic logic for logic design verification, temporal logic [10], which can express the notion of time explicitly, has been studied widely in the field of formal design verification of protocols and logic circuits. Some practical formal design verification systems have been developed on the basis of temporal logic [1, 2, 3, 4, 5, 11]. The temporal logic used in these systems, however, does not have enough expressive power to describe the specifications of any finite automata. Because of the weak expressive power of conventional temporal logic, there have been several attempts to extend its expressive power. Wolper et al. introduced temporal operators associated with right linear grammar and/or Büchi automata [12, 13] and achieved on expressive power equivalent to that of finite automata. In order to describe specifications in their logic, however, it is necessary to introduce temporal operators that correspond in a sence to the automaton to be designed. We therefore need an infinite number of temporal operators to describe the specifications of any finite automaton in general. Moszkowski proposed a more powerful temporal logic named interval temporal logic (ITL) [9], but its expressive power is too strong and its satisfiability problem is undecidable. It is therefore difficult to use ITL as a basis for logic design verification.

This is a translation of the paper that appeared originally in Japanese in Transactions of IPSJ, Vol. 31, No. 7 (1990), pp. 1134-1145

<sup>1145.

\*</sup>Department of Information and Communication Sciences,

Faculty of Engineering, Kyoto Sangyo University.

<sup>\*\*</sup>Department of Information Science, Faculty of Engineering, Kyoto University.

<sup>\*\*\*</sup>Information and Communication Processing Research Laboratory, NTT.

Considering the above stated problems, we have proposed various classes of regular temporal logic (RTL) [6, 14, 17] that correspond to regular sets (regular sets can be regarded as input/output sequences (behavior sequences) of finite automata),  $\varepsilon$ -free regulae sets (a subclass of regular sets), and  $\infty$  and/or  $\omega$  regular sets, which include infinite sequences.

Regular temporal logic contains only three temporal operators, which express notions of time, namely, "next time," "next interval," and "repeat," in addition to the conventional propositional operators. Its expressive power is equivalent to that of finite automata. We can therefore describe the input/output specifications of any logic circuit in RTL.

In this paper, we first give a unified definition for various classes of temporal logics and discuss their expressive power. In order to verify that a given automaton or a sequential machine meets their specifications, we also propose an efficient model-checking algorithm of RTL. A formal logic design verification system based on the proposed model-checking algorithm has been implemented, and some verification examples show that it can verify the correctness of the design of sequential machines with several hundred states in a reasonable time and space.

This paper is organized as follows: Section 2 gives the basic notations and definitions of finite automata, infinite strings, and so on. Four classes of regular temporal logics are introduced. Section 3 discusses basic approaches to verification based on one class of RTL named  $\varepsilon$ -free RTL. In Section 4, a verification algorithm called model-checking algorithm is described and its computational complexity is discussed. Section 5 explains the verification system (model checker) based on the proposed algorithm. Examples of design verification are also given and show that the RTL model checker is useful from a practical point of view. Section 6 concludes this paper by summarizing the results.

#### 2. Regular Temporal Logic

#### 2.1 Basic Notations

This section gives the basic notation and definitions of basic terminologies.

A finite word over an alphabet  $\Sigma$  is a finite non-null sequence of symbols from  $\Sigma$ . An  $\omega$  wold is a countably infinite sequence of symbols from  $\Sigma$ . An empty word is a null sequence that contains no symbols and is denoted by  $\varepsilon$ .  $\Sigma^{\dagger}$  is a set of all finite words over  $\Sigma$ .  $\Sigma^{\omega}$  is a set of all  $\omega$  words over  $\Sigma$ .  $\Sigma^* = \Sigma^{\dagger} \cup \{\varepsilon\}$  and  $\Sigma^{\infty} = \Sigma^* \cup \Sigma^{\omega}$ . An element in  $\Sigma^{\infty}$  is called a word over  $\Sigma$ .

For a word x over  $\Sigma$ , |x| represents the length of x. x(i) refers to the i-th symbol of x and  $x^i$  represents the suffix sequence of x starting at the i-th symbol of x. Note that  $x^1 = x$ ,  $|\varepsilon| = 0$ , and  $|x| = \omega$  if x is an  $\omega$  word. We also define that  $x(i) = \varepsilon$  and  $x^i = \varepsilon$  for i > |x|.

Concatenation of two words x and y over  $\Sigma$ , denoted

by xy, is defined as follows:

- 1.  $\varepsilon x = x \varepsilon = x$ .

- 2. If  $x \in \Sigma^{\dagger}$  and  $y \in \Sigma^{\dagger} \cup \Sigma^{\omega}$ ,

- xy(i)=x(i) for any integer i such that  $1 \le i \le |x|$ .

- xy(|x|+i)=y(i) for any integer i such that  $1 \le i$ .

- 3. If  $x \in \Sigma^{\omega}$ , xy = x.

A set of words over  $\Sigma$  is called a *language* over  $\Sigma$ .  $L_1L_2$  denotes a concatenation of two languages  $L_1$  and  $L_2$  over  $\Sigma$ , and is defined as  $L_1L_2 = \{xy | x \in L_1, y \in L_2\}$ . Various types of closure of a language L over  $\Sigma$  are

defined as follows:  $L^{\dagger} = \bigcup_{i=1}^{\infty} L^{i}$ ,  $L^{*} = \bigcup_{i=0}^{\infty} L^{i}$ ,  $L^{\omega} = \{x_{1}x_{2} \cdot \dots \mid x_{1}, x_{2}, \dots \in L \cap \Sigma^{\dagger}\}$ , and  $L^{\infty} = L^{*} \cup L^{\omega}$ , where

$L^0 = \{\varepsilon\}$  and  $L^{i+1} = L^i L (i \ge 0)$ . **Definition 1 (Regular Set).** Let us consider the following production rules for a class of languages,  $\mathcal{R}$ , over  $\Sigma$ :

- A1. An empty set  $\emptyset$  is an element of  $\Re$ .

- A2. If  $s \in \Sigma$ , a set  $\{s\}$  is an element of  $\Re$ .

- A3. In  $L_1$ ,  $L_2 \in \mathcal{R}$ ,  $L_1 \cup L_2$  and  $L_1 L_2$  are elements of  $\mathcal{R}$ .

- A4. If  $L \in \mathcal{R}$ ,  $L^*$  is an element of  $\mathcal{R}$ .

- A5. If  $L \in \mathcal{R}$ ,  $L^{\omega}$  is an element of  $\mathcal{R}$ .

If a language L over  $\Sigma$  is an element of the class of laguages  $\mathcal{R}$  constructed by the finite application of the above rules A1-A5, L is called an  $\infty$  regular set. In this case, if  $L \subseteq \Sigma^{\omega}$ , L is called an  $\omega$  regular set; if  $\varepsilon \notin L$ , L is called an  $\varepsilon$ -free  $\infty$  regular set. If L is an element of a class of languages obtained by the finite applications of the above rules A1-A4, L is simply called a regular set. In this case, if  $\varepsilon \notin L$ , L is called  $\varepsilon$ -free regular set.

### 2.2 Dfinition of Regular Temporal Logic

Regular Temporal Logic (RTL for short) is an extension of propositional logic with three temporal operators "O", ":", and ":" whose intuitive meanings are "next time," "next interval," and "repeat," respectively.

**Definition 2(Syntax).** Let AP be a set of atomic propositions. RTL formulas are defined inductively as follows:

- B1. If  $p \in AP$ , then p is an RTL formula.

- B2. If  $\eta$  is an RTL formula, then so are  $(\neg \eta)$ ,  $(\bigcirc \eta)$ , and  $(\boxdot \eta)$ .

- B3. If  $\eta$  and  $\xi$  are RTL formulas, then so are  $(\eta \lor \xi)$  and  $(\eta : \xi)$ .

Let  $\Sigma$  be a set of states. The value of an RTL formula is defined according to a sequence of states in  $\Sigma$ . Let D be a semantic domain of RTL formulas. If  $D = \Sigma^{\dagger}$ , the RTL is called  $\varepsilon$ -free finite RTL. If  $D = \Sigma^*$ , it is called finite RTL. If  $D = \Sigma^* - \{\varepsilon\}$ , it is called  $\varepsilon$ -free infinite RTL. If  $D = \Sigma^*$ , it is called infinite RTL.

The  $\varepsilon$ -free finite RTL is exactly the same temporal logic as proposed in [6, 7]. The finite RTL is exactly the same temporal logic as proposed in [16, 17]. The  $\varepsilon$ -free infinite RTL is exactly the same temporal logic as proposed in [14, 15].

The formal semantics of RTL formulas are given in the following.

**Definition 3 (Linear Model).** A tuple  $M = (\Sigma, I)$  is called a *linear model* of RTL, where  $\Sigma$  is a set of states and I is a function for interpreting atomic propositions. I labels each state with a set of atomic porpositions that are true in that state. For the  $\varepsilon$ -free finite/infinite RTL,  $I: \Sigma \to 2^{AP}$ ; for the finite/infinite RTL,  $I: \Sigma \cup \{\varepsilon\} \to 2^{AP}$ .

**Definition 4(Value of RTL Formulas).** M,  $\sigma \vDash \eta$  denotes that the RTL formula  $\eta$  is *true* for the state sequence  $\sigma$  over the linear model M. If there is no confusion, we sometimes omit M and just write  $\sigma \vDash \eta$ . Let p be an atomic proposition,  $\eta$  and  $\xi$  be RTL formulas, and D be a semantic domain of the RTL. We also assume that  $\sigma \in D$ . The relation  $\vDash$  is defined inductively as follows:

- C1.  $\sigma \vDash p \Leftrightarrow p \in I(\sigma(1))$ .

- C2.  $\sigma \vDash (\neg \eta) \Leftrightarrow \sigma \nvDash \eta$ .

- C3.  $\sigma \vDash (\eta \lor \xi) \Leftrightarrow \sigma \vDash \eta \text{ or } \sigma \vDash \xi$ .

- C4.  $\sigma \vDash (\bigcirc \eta) \Leftrightarrow$

- In the case of  $\varepsilon$ -free RTL,  $|\sigma| \ge 2$  and  $\sigma^2 = \eta$ .

- Otherwise  $\sigma^2 = n$ .

- C5.  $\sigma \vDash (\eta:\xi) \Leftrightarrow$

- If | σ| ≠ω, σ=σ₁σ₂ and there exist σ₁ and σ₂ in

D such that σ₁ ⊨ η and σ₂ ⊨ ξ.

- If  $|\sigma| = \omega$ ,  $\sigma \vDash \eta$  or there exist  $\sigma_1$  and  $\sigma_2$  in D such that  $\sigma = \sigma_1 \sigma_2$ ,  $|\sigma_1| \neq \omega$ ,  $|\sigma_2| = \omega$ ,  $\sigma_1 \vDash \eta$ , and  $\sigma_2 \vDash \xi$ .

- C6.  $\sigma \vDash (\Box \eta) \Leftrightarrow$

- If  $|\sigma| \neq \omega$ , there exist  $\sigma_i \in D$   $(1 \leq \forall i \leq m)$  such that  $\sigma = \sigma_1 \sigma_2 \cdots \sigma_m$  and  $\sigma_i \models \eta (1 \leq \forall i \leq m)$ .

- If  $|\sigma| = \omega$ , there exist  $\sigma_i \in D$   $(1 \le \forall i \le m)$  such that  $\sigma = \sigma_1 \sigma_2 \cdots \sigma_m$ ,  $\sigma_i \models \eta (1 \le \forall i \le m)$ ,  $|\sigma_i| \ne \omega (1 \le \forall i < m)$ , and  $|\sigma_m| = \omega$ ; or there exist  $\sigma_i \in D$  such that  $\sigma = \sigma_1 \sigma_2 \cdots$ , and  $\sigma_i \models \eta$  and  $|\sigma_i| \ne \omega$  for  $\forall i \ge 1$ .

Intuitively, " $\bigcirc \eta$ " indicates that  $\eta$  holds for the sequence starting from the next state. " $\eta$ : $\xi$ " means that  $\eta$  holds for the former part of the sequence and  $\xi$  holds for the latter part of the sequence. " $\boxdot \eta$ " indicates that  $\eta$  holds repeatedly.

We also use conventional abbreviations such as " $^{^{\prime\prime}}$ " for conjunction, " $\Rightarrow$ " for implication, " $\equiv$ " for equivalence, " $^{\prime\prime}$ " for tautology, and " $^{\prime\prime}$ " for invalid formula. We also assume that unary operators have higher precedence than binary operators. When there is no ambiguity, we usually omit parentheses.

If M,  $\sigma \vDash \eta$  for some linear model M and some state sequence  $\sigma \in D$ ,  $\eta$  is said to be safisfiable.

#### 2.3 Expressive Power of Regular Temporal Logic

Let  $\eta$  be an RTL formula. The set of sequences for which  $\eta$  becomes *true* is represented as  $L\langle \Sigma, I\rangle(\eta) = \{\sigma \mid \sigma \in D, \sigma \models \eta\}$ . When there is no ambiguity, we abbreviate  $L\langle \Sigma, I\rangle(\eta)$  as simply  $L(\eta)$ . According to the definition of RTL (Definition 4), we have the following lemma:

**Lemma 1.** Let p be an atomic proposition and  $\eta$  and  $\xi$  be RTL formulas. For a linear model  $M=(\Sigma, I)$  of RTL,

- 1.  $L(p) = \{s\sigma | s \in \Sigma, p \in I(s), s\sigma \in D\} \cup \{\varepsilon | \varepsilon \in D, p \in I(\varepsilon)\}$

- 2.  $L(-\eta) = D L(\eta)$

- 3.  $L(\eta \lor \xi) = L(\eta) \cup L(\xi)$

- 4.  $L(\bigcirc \eta) = \Sigma L(\eta) \cup (\{\varepsilon\} \cap L(\eta))$

- 5.  $L(\eta:\xi)=L(\eta)L(\xi)$

- 6.  $L(\Box \eta) = L(\eta)^{\dagger} \cup (L(\eta)^{\omega} \cap D)$

Let  $\mathcal{F}$  be one of the various classes of RTL (namely,  $\varepsilon$ -free finite RTL, finite RTL,  $\varepsilon$ -free infinite RTL, or infinite RTL). Let  $\mathcal{R}$  be a class of languages.  $\mathcal{F}$  is said to be expressively equivalent to  $\mathcal{R}$  if and only if the following two conditions hold:

- For any RTL formula η∈ F, L⟨Σ, I⟩(η) is an element of R.

- For any language  $R \in \mathcal{R}$ , there exist an RTL formula  $\eta \in \mathcal{F}$  and an interpretation function I such that  $L(\Sigma, I)(\eta) = R$ .

We have the following theorem about the expressive power of the four classes of RTL defined in the previous section.

# Theorem 1 (Expressive Power of Regular Temporal Logic)

- 1.  $\varepsilon$ -free finite RTL is expressively equivalent to an  $\varepsilon$ -free regular set [6].

- 2. Finite RTL is expressively equivalent to a regular set [17].

- 3.  $\varepsilon$ -free infinite RTL is expressively equivalent to an  $\varepsilon$ -free  $\infty$  regular set [14, 15].

- 4. Infinite RTL is expressively equivalent to an  $\infty$  regular set.

(Proof) We give a proof only for the fourth case. From Lemma 1, it is clear that  $L(\eta)$  is an  $\infty$  regular set for any infinite RTL formula  $\eta$ . Conversely, let R be a  $\infty$  regular set over  $\Sigma$ . Let  $AP = \{p_s | s \in \Sigma\}$  and  $I(p_s) = \{s\}$ . Let F(R) denote an infinite RTL formula  $\eta$  such that  $L(\eta) = R$ . F(R) can be calculated inductively as follows:

- 1.  $F(\emptyset) = V_F$

- 2.  $F(\{s \in \Sigma\}) = p_s \land \neg p_0 \land \bigcirc p_0$

- 3.  $F(R_1 \cup R_2) = F(R_1) \vee F(R_2)$

- 4.  $F(R_1R_2)=F(R_1):F(R_2)$

- 5.  $F(R^*)=p_0\vee \Box F(R_1)$

- 6.  $F(R^{\omega}) = \Box (F(R) \wedge Fin \wedge \neg p_0),$

where  $p_0$  is an atomic proposition such that  $I(p_0) = \{\varepsilon\}$ ,  $\neg p_0 \land \bigcirc p_0$  represents a set of all sequences whose length are exactly one, and  $Fin \triangleq \neg (V_T : V_F)$  represents a set of all finite sequences that include an empty word  $\varepsilon$ .

A set of behavior sequences (input/output sequences) of a finite automaton is equivalent to an ( $\epsilon$ -free) regular set when we are concerned only with finite behavior; it is equivalent to an  $\omega$  regular set if we are concerned only with infinite behavior; it is equivalent to an ( $\epsilon$ -free)  $\infty$  regular set if we are concerned with both. In this sense, RTL is expressively equivalent to finite automata, and any behavior sequences of any finite automaton can be completely described in RTL.

## 3. Design Verifincation of Sequential Machines

### 3.1 Description of Specification and Design

In this section we discuss how to verify the design of sequential machines by using RTL. Let us consider verification of a deterministic Mealy-type or Moore-type sequential machine with n binary input signals  $X = \{x_1, x_2, \dots, x_n\}$  and m binary output signals  $Z = \{z_1, z_2, \dots, z_m\}$ . Its behavior sequence (input-output sequence) is represented by a finite sequence  $\rho$  over  $2^{X \cup Z}$  such that  $\rho(k) \triangleq \{x_i | x_i = 1 \text{ at the } k\text{-th input}\} \cup \{z_j | z_j = 1 \text{ at the } k\text{-th output}\}$ .

We assume that a design specification is given in terms of a set of possible behavior sequences of a machine to be designed. Let us consider a finite behavior sequence of any length. Let  $p_{x_i}$  and  $p_{z_j}$  be atomic propositions associated with input signal  $x_i$  and output signal  $z_j$ , respectively, such that  $p_{x_i}$  is true iff  $x_i=1$  and  $p_{z_j}$  is true iff  $z_j=1$ . Then we can describe the set of all possible finite behavior sequences of the machine in  $\varepsilon$ -free RTL. Though we can express an infinite behavior sequence by using  $\varepsilon$ -free infinite RTL, we will discuss the verification problem for infinite behavior in a future paper. Hereafter, RTL refers to  $\varepsilon$ -free RTL.

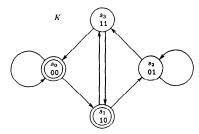

For example, let us consider design verification of the T flipflop shown in Fig. 1. We assume that the output z is 0 in the initial state. The output z changes its value if and only if the previous input x is 1.

Let  $p_x$  be an atomic proposition whose value is *true* if and only if the input x=1, and let  $p_z$  be an atomic proposition whose value is *ture* if and only if the output z=1. Then the specification of the T flipflop can be written as follows:

$$\eta \triangleq p_x \equiv (p_z \equiv \bigcirc \neg p_z)

spec \triangleq \neg p_z \land \Box (\eta \lor LEN1),

\text{where } LEN1 \triangleq \neg \bigcirc V_\tau, \quad \Diamond \xi \triangleq \xi \lor (V_\tau : \xi), \text{ and } \Box \xi \triangleq \neg \Diamond \neg \xi.$$

Fig. 1 T flipflop.

Fig. 2 Two designs of T flipflop.

$\eta$  indicates that the value of z at the next time differs from that at the current time if and only if the current value of x is 1. LEN1,  $\diamondsuit \xi$ , and  $\Box \xi$  mean that "the length of the sequence is 1," " $\xi$  will become true at some time in the future or present," and " $\xi$  is always true from now on." The specification spec of the T flipflop means that the initial value of z is 0 and  $\eta$  always holds from now on. Since this property of the T flipflop is meaningless for a time sequence whose length is 1, LEN1 is used in spec so that spec ignores a non-existing next state on the last occasion of a time period under consideration.

The design of this T flipflop is assumed to be given as either a Mealy-type or a Moore-type sequential machine, as shown in Fig. 2. The verification problem then becomes to check whether spec holds for all possible finite behavior sequences of the designed machine.

#### 3.2 Structure Model

In order to treat possible behavior sequences more easily, we define a structure model.

**Definition 5 (Structure Model).** A structure model is a 4-tuple  $K = (\Sigma, I, R, \Sigma_0)$ , where

- 1.  $(\Sigma, I)$  is a linear model of RTL.

- 2.  $R \subseteq \Sigma \times \Sigma$  is a binary relation over  $\Sigma$  and represents a transition relation between states.

- 3.  $\Sigma_0 \subseteq \Sigma$  is a set of initial states.

A structure model is a kind of Kripke model [8] with a set of initial states. For a structure model  $K = (\Sigma, I, R, \Sigma_0)$ , a finite sequence of states  $\pi = s_1 s_2 \cdots s_n \in \Sigma^{\dagger}$  is called a *finite path* from  $s_1$  if and only if  $(s_i, s_{i+1}) \in R$  for any i such that  $1 \le i < n-1$ .

The truth value of an RTL formula with respect to a structure model K is defined as follows.

**Definition 6 (Truth Value with Respect to a Structure Model).** If  $\sigma \vDash \eta$  for a finite path  $\sigma$  from a state s of a structure model K,  $\eta$  is said to be *true with respect to*  $\langle K, s \rangle \langle \langle K, s \rangle \rangle$ -true); otherwise, it is said to be *false with respect to*  $\langle K, s \rangle \langle \langle K, s \rangle \rangle$ -false). Furthermore, if  $\eta$  is  $\langle K, s_0 \rangle$ -true for some initial state  $s_0 \in \Sigma_0$ ,  $\eta$  is said to be *true over* K(K-true); otherwise,  $\eta$  is said to be *false over* K(K-false).

Let  $M=(X, Z, S, \delta, \lambda, s_0)$  be a deterministic sequential machine, where

- 1. X is a finite set of binary input signals.

- 2. Z is a finite set of binary output signals.

- 3. S is a finite set of states.

- 4.  $s_0 \in S$  is the initial state.

- 5.  $\delta:2^X \times S \rightarrow S$  is the next state function.

- 6.  $\lambda$  is the output function such that

- For Moore type;  $\lambda: S \rightarrow 2^Z$  is a total function over S.

- For Mealy type;  $\lambda: 2^x \times S \rightarrow 2^z$  and has the same domain as  $\delta$ .

The structure model K corresponding to M is constructed as follows:

$\Sigma \triangleq \{s_{i,j} | s_i \in S, j \in 2^X, \delta(j, s_i) \text{ is defined.} \}$

Fig. 3 Structure model of T flipflop.

$$I(s_{i,j}) \triangleq \begin{cases} \{p_x | x \in j\} \cup \{p_z | z \in \lambda(j, s_i)\} & \text{for Mealy type} \\ \{p_x | x \in j\} \cup \{p_z | z \in \lambda(s_i)\} & \text{for Moore type} \end{cases}$$

$$R \triangleq \{(s_{i,j}, s_{i',j'}) | s_{i,j}, s_{i',j'} \in \Sigma, \delta(j, s_i) = s_{i'}\}$$

$$\Sigma_0 \triangleq \{s_{0,j} \in \Sigma\}.$$

The structure model corresponding to the T flipflop is shown in Fig. 3. Let |E| be the number of transition edges of a sequential machine M. Then the size of the structure model K corresponding to M becomes as follows:

$$O(|\Sigma|) = O(|E|) = O(|\Sigma|2^{|X|})$$

$$O(|R|) = O(|E|2^{|X|}) = O(|\Sigma|2^{2|X|})$$

$$O(|\Sigma| + |R|) = O((|\Sigma| + |E|)2^{|X|})$$

As can be easily seen from the way in which a structure model is constructed, there is a one-to-one correspondence between a set of possible behavior sequences of M and a set of paths from an initial state of the corresponding structure model K of M. The verification problem of a sequential machine M over its corresponding structure model K becomes one of checking whether "spec is true for every finite path from any initial state of K" or whether "spec is K-false." This is done by a model-checking method described in the next section.

#### 4. Model-Checking Approach

Model checking determines whether an RTL formula  $\eta$  is K-true or not. Before describing the model checking algorithm, we first define the *derivation* of the RTL formula.

# 4.1 Derivative of an $\varepsilon$ -Free Finite Regular Temporal Logic Formula

The derivative of an RTL formula  $\eta$  by a state  $s \in \Sigma$ , denoted by  $\eta/s$ , gives a formula that should hold in the next state so that  $\eta$  may hold in the present state. It is formally defined inductively as follows:

$$p/s \triangleq \begin{cases} V_T & \text{if } p \in I(s) \\ V_F & \text{otherwise} \end{cases}$$

$$(\neg \eta)/s \triangleq \neg (\eta/s)$$

$$(\eta \lor \xi)/s \triangleq (\eta/s) \lor (\xi/s)$$

$$(\bigcirc \eta)/s \triangleq \eta$$

$$(\eta:\xi)/s \triangleq \begin{cases} \xi \lor ((\eta/s): \xi) \text{ if } s \vDash \eta \\ (\eta/s): \xi \text{ otherwise} \end{cases}$$

$$(\vdots \eta)/s \triangleq \begin{cases} (\eta/s) \lor ((\eta/s): \vdots \eta) \lor \vdots \eta \text{ if } s \vDash \eta \\ (\eta/s) \lor ((\eta/s): \vdots \eta) \text{ otherwise.} \end{cases}$$

Derivative of  $\eta$  by a sequence of states  $\sigma = s_1 s_2 \cdots s_n \in \Sigma^{\dagger}$  is defined as

$$\eta/\sigma \triangleq ((\cdots ((\eta/s_1)/s_2)\cdots)/s_n).$$

We also define that  $\eta/\varepsilon \triangleq \eta$ . Note that  $V_T/s = V_T$  and  $V_F/s = V_F$ .

From the definition of derivatives, the next lemma clearly holds:

**Lemma 2.** Let  $\sigma$  be a finite sequence over  $\Sigma$  such that  $|\sigma| \ge 2$ . Then the necessary and sufficient condition for  $\sigma \vDash \eta$  is  $\sigma^2 \vDash \eta/\sigma(1)$ .

**Theorem 2.** Let  $K = (\Sigma, I, R, \Sigma_0)$  and  $\eta$  be a structure model and an RTL formula, respectively. The necessary and sufficient condition that  $\eta$  is (K, s)-true for a state  $s \in \Sigma$  is that either  $s \models \eta$  or there exists a state s' such that  $(s, s') \in R$  and  $\eta/s$  is (K, s')-true.

(Proof) From Definition 6,  $\eta$  is  $\langle K, s \rangle$ -true if and only if  $\sigma \vDash \eta$  for some finite path  $\sigma$  on K from s. Considering Lemma 2, this is equivalent to the condition that  $s \vDash \eta$  or  $\eta/s$  is  $\langle K, s' \rangle$ -true for some state s' such as  $(s, s') \in R$ . (Q.E.D.)

In the calculation of derivatives and checking conditions stated in Theorem 2, we need to obtain the truth value of  $\eta$  for a sequence s whose length is 1. This can be obtained inductively as follows:

- 1.  $s = p \Leftrightarrow p \in I(s)$

- 2.  $s \models \eta \lor \xi \Leftrightarrow s \models \eta \text{ or } s \models \xi$

- 3.  $s \models \neg \eta \Leftrightarrow s \not\models \eta$

- 4.  $s \models \bigcirc \eta$  always holds.

- 5.  $s \nvDash \eta : \xi$  always holds.

- 6.  $s = \square \eta \Leftrightarrow s = \eta$

#### 4.2 Model-Checking Algorithm

It is easy to construct a model-checking algorithm by a depth-first search for the necessary and sufficient condition stated in Theorem 2.

## Algorithm 1 (Model-checking algorithm)

Input: a structure model  $K = (\Sigma, I, R, \Sigma_0)$  and an RTL formula  $\eta$ .

Output: if  $\eta$  is K-true then 'T' else 'F'.

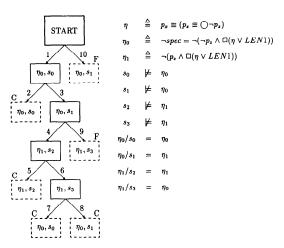

Method: by  $Verify(K, \eta)$  in Fig. 4.

In Fig. 4, Check  $(K, s, \eta)$  is a procedure that returns 'T' if  $\eta$  is  $\langle K, s \rangle$ -ture, or 'F' otherwise. Addlabel $(s, \eta, x)$  registers a label x to a tuple  $(s, \eta)$ , which means that the value of  $\eta$  is x in state s. x= 'F' means that  $\eta$  is  $\langle K, s \rangle$ -false. x= 'C' means that the truth value of  $\eta$  in state s is now under investigation. These labels are used to prevent the procedure Check from being called more than once for the same pair of s and  $\eta$ . We need not use a label to show that  $\eta$  is  $\langle K, s \rangle$ -true, because the procedure Verify returns 'T' immediately after the procedure Check returns 'T'. Label $(s, \eta)$  returns the label of  $\eta$  at s if it is already registered; otherwise it returns null.

```

procedure Verify(K, \eta)

procedure Derivation(s, \eta);

begin

begin

switch(\eta){

for all s \in \Sigma_0

case \eta \in AP:

begin

if \eta \in I(s) then return ('T',V_T);

if Label(s, \eta) \neq 'F' then

else return ('F',Vr);

if Check(K, s, \eta) = T then return T;

end

case \eta = \neg \eta_1:

(x,\xi) := \operatorname{Derivation}(s,\eta_1);

return 'F':

if x = T then return (F', \neg \xi);

end

else return ('T',¬ξ);

end of procedure

case \eta = \eta_1 \vee \eta_2:

(x_1, \xi_1) := Derivation(s, \eta_1);

procedure Check(K, s, \eta)

(x_2, \xi_2) := Derivation(s, \eta_2);

begin

if (x_1 = T') or x_2 = T' then x := T';

(x,\xi) := Derivation(s,\eta);

if x = T' then return T';

else x := 'F':

if \xi = V_T then return 'T';

return (x, \xi_1 \vee \xi_2);

case \eta = \bigcap \eta_1:

if \xi = V_F then

return ('F',\eta_1);

begin

Addlabel(s, n,'F');

se \eta = \eta_1 : \eta_2

(x,\xi) := \operatorname{Derivation}(s,\eta_1);

return 'F';

end

\xi := \xi : \eta_2;

if x = T then \xi := \xi \vee \eta_2;

Addlabel(s, \eta, C');

return ('F',ξ);

for all s' such that (s, s') \in R

case \eta = [:] \eta_1:

begin

(x,\xi) := Derivation(s,\eta_1);

x := Label(s', \xi);

\xi := \xi \vee (\xi : \eta);

if x = NIL then

if x = T' then \xi := \xi \vee \eta;

if Check(K, s', \xi) = 'T' then return 'T';

end

return (x, \xi):

Addlabel(s, n,'F');

return 'F':

end of procedure

end

end of procedure

```

Fig. 4 Model-checking algorithm.

Verify  $(K, \eta)$  calls Check  $(K, s, \eta)$  successively for each initial state  $s \in \Sigma_0$  if  $\eta$  is not yet proved to be  $\langle K, s \rangle$ -false. If the procedure Check returns 'T' at least once, the procedure Verify also returns 'T'; otherwise it returns 'F'.

Check  $(K, s, \eta)$  first calls Derivation  $(K, s, \eta)$ . Derivation  $(K, s, \eta)$  checks whether  $s \models \eta$  as well as calculating  $\eta/s$ . It substitutes  $\eta/s$  into  $\xi$  and also substitutes either 'T' or 'F' into x according to whether  $s \models \eta$  or  $s \models \eta$ . Then it returns 'T' when  $\xi = \eta/s$  is  $V_T$  or x = 'T'. If  $\xi = \eta/s$  is  $V_T$ , it labels the tuple  $(s, \eta)$  'F', and returns 'F'. Otherwise, it labels the tuple  $(s, \eta)$  'C'. Then it checks Label  $(s', \eta/s)$ , and if the tuple  $(s', \eta/s)$  is not yet labeled, it calls Check  $(K, s', \eta/s)$  recursively for each next state s' of s successively. It returns 'T' when one of the recursive calls to the procedure Check returns 'T'. If every recursive call to the procedure Check results in the return value 'F', it labels the tuple  $(s, \eta)$  'F' and then returns 'F'.

Figure 5 shows an example of model checking of the T flipflop. In Fig. 5, a solid box indicates that *Check*  $(K, s, \eta)$  is called with the argument written inside the solid box. A dashed box indicates that the tuple of the state and the formula written inside the dashed box are already labeled either 'F' or 'C'. The numbers above the edges represent the order of depth-first search over a structure model. In this example, every call to the procedure *Check* ends with a return value 'F', and *Verify* (K, -spec) returns 'F'. This means that the design shown in Fig. 2 satisfies the specification spec.

Fig. 5 Verification of T flipflop by the model-checking algorithm.

#### 4.3 Correctness and Complexity

First we show that the number of different formulas obtained by derivations of an RTL formula  $\eta$  repeatedly is at most finite.

Let  $D^*(\eta) \triangleq \{\eta/\sigma | \sigma \in \Sigma^*\}$ . In the definition of  $D^*(\eta)$  we regard two formulas as identical if they can be transformed into one another by using the relations  $V_T \lor \xi = V_T$  and  $V_F \lor \xi = \xi$ , and by the commutative, associative, and idempotence laws of ' $\lor$ '.

**Lemma 3.**  $D^*(\eta)$  is a finite set.

(Proof) It is shown inductively according to the rules for construction of RTL formulas:

- 1.  $D^*(p) = \{p, V_T, V_F\}.$

- 2.  $D^*(\neg \eta) = {\neg \xi \mid \xi \in D^*(\eta)}.$

- 3.  $D^*(\eta_1 \vee \eta_2) \subseteq \{ \xi_1 \vee \xi_2 | \xi_1 \in D^*(\eta_1), \xi_2 \in D^*(\eta_2) \}.$

- 4.  $D^*(\bigcirc \eta) = \{\bigcirc \eta\} \cup D^*(\eta)$ .

- 5. Let  $E_1 \triangleq \{ \vee [\Theta] \mid \Theta \in 2^{D^{\bullet}(\eta_2)} \}$  and  $E_2 \triangleq \{ \xi_1 : \eta_2 \mid \xi_1 \in D^{\bullet}(\eta_1) \}$ . Then,  $D^{\bullet}(\eta_1 : \eta_2) \subseteq \{ \nu_1 \vee \nu_2 \mid \nu_1 \in E_1, \nu_2 \in E_2 \}$

- 6. Let  $F_1 \triangleq \{ \vee [\Theta] \mid \Theta \in 2^{D^*(\eta) \cup \{ \cap_{\eta} \}} \}$  and  $F_2 \triangleq \{ \xi_1 : \mathbb{I} \}$   $\{ \eta \mid \xi_1 \in D^*(\eta) \}$ . Then,  $D^*(\mathbb{I} \eta) \subseteq \{ \nu_1 \vee \nu_2 \mid \nu_1 \in F_1, \nu_2 \in F_2 \}$

$\vee [\Theta]$  represents the disjunction of all RTL formulas in  $\Theta$ . Every set represented by the right-hand sides of these expressions is clearly a finite set. (Q.E.D.)

[Proof of the correctness of Algorithm 1]. Its correctness is clear from the definition of K-true and Theorem 2 except for its termination and loop handling.

Termination: From Lemma 3, the number of different RTL formulas obtained by derivations during the execution of the algorithm is finite. In addition, the procedure *Check* is called only once for the same tuple of a state and an RTL formula. Therefore, Algorithm 1 always terminates.

**Loop handling:** When Check  $(K, s, \eta)$  detects a loop (that is, when  $\xi = \eta/s$  and Label  $(s', \xi) = C'$  for some s' such as  $(s, s') \in R$ ), it just handles the loop in the same way as Label  $(s', \xi) = F'$ . The correctness of this handling is shown as follows. Let  $\sigma$  be a sequence of states from s' to s along the loop. Since Label  $(s', \xi) = C'$ ,  $\xi/\sigma = \xi$  and  $\sigma_p \nvDash \xi$  for any prefix sequence  $\sigma_p$  of  $\sigma$ . Let us assume that  $\tau \sigma_p \vDash \xi$  for some sequence  $\tau \in \{\sigma\}^{\dagger}$ . Since  $\xi/\sigma = \xi$ ,  $\sigma_p \vDash \xi$  is shown by repeated application of Lemma 2, which is a contradiction. Therefore,  $\xi$  becomes false for any finite prefix sequence of the infinite sequence generated by the loop, and we can treat this case in the same way as that of Label  $(s', \xi) = F'$ .

Next we evaluate the computational complexity of Algorithm 1. Let  $\mathcal{N} \triangleq |\mathcal{D}^*(\eta)|$  and  $\mathcal{L}$  represent the maximum number of operators contained in a formula in  $D^*(\eta)$ .  $|\eta|$  represents the number of operators in a formula  $\eta$ .

**Theorem 3.** The time complexity of Algorithm 1 is  $O((|\Sigma|(\mathcal{L}\log \mathcal{L} + \log \mathcal{N}) + |R|\log \mathcal{N})\mathcal{L}\mathcal{N})$ .

(Proof) First we evaluate the time complexity of *Derivation*  $(s, \xi)$ . The procedure *Derivation* checks whether  $s \models \xi$  holds at the same time as it calculates  $\xi/s$ . Whether or not  $s \models \xi$  can be checked in a time proportional to  $|\xi|$  by checking whether  $s \models \xi'$  for each subformula  $\xi'$  of  $\xi$  in a bottom-up fashion. In the calculation of  $\xi/s$ , it is sometimes necessary to check whether  $s \models \xi'$  for some subformulas  $\xi'$  of  $\xi$ , which should have been already obtained during the bottom-up calculation. Furthermore, in a derivative operation of an RTL formula, some subformula and/or its derivative may appear twice (in the case of a derivative of ":" or ":"). Even in such cases, the result can be obtained by adding

at most three operators for each ":" or ":" if we adopt a graphic representation of formulas that share a common subformula. Basically, therefore, can be found  $\xi/s$  in a time proportional to  $|\xi|$ . In order to guarantee the termination of the algorithm, however, we need to simplify  $\xi/s$  by using the idempotence, commutative, and associative laws of 'v'. This can be done by sorting every term in every disjunctive clause. Sorting of terms requires that formulas be compared a total of  $O(|\xi/s| \log |\xi/s|)$  times and that each comparison can be done in a time proportional to  $|\xi/s|$ . Therefore, derivation requires  $O(\mathcal{L}^2 \log \mathcal{L})$  time, because  $\xi$  and  $\xi/s$  are in  $D^*(\eta)$ .

The procedures Addlabel and Label can be realized with  $\log \mathcal{N}$  comparisons by sorting every formula in  $D^*(\eta)$ . Since each comparison requires a time proportional to  $\mathcal{L}$ , the time complexity of each of the procedures Addlable and Label is  $O(\mathcal{L} \log \mathcal{N})$ .

Furthermore, the procedure *Check* is called a total of  $O(|\Sigma|)$  times for each formula in  $D^*(\eta)$ . As a result, *Derivation* and *Addlabel* will be called at most  $|\Sigma|$  times in total. *Label* may be called |R| times in total, because it will be called for the subsequent state of each current state. Therefore, the time complexity of Algorithm 1 is  $O((|\Sigma|(\mathcal{L}\log\mathcal{L}+\log\mathcal{N})+|R|\log\mathcal{N})\mathcal{L}\mathcal{N})$ .

We have the following theorem on the Deterministic Turing Machine (DTM) space complexity of the model checking problem:

**Lemma 4.** The DTM space complexity of the satisfiability problem of finite RTL is non-elementary [6].

**Theorem 4.** The DTM space complexity of the model-checking problem for a finite RTL formula is non-elementary.

(Proof) We show that the satisfiability problem of an RTL formula can be transformed in elementary time to a model-checking problem for an RTL formula. Let AP' be a set of atomic propositions appearing in a RTL formula  $\eta$ . Let  $\Sigma$  be a set consisting of  $2^{\lfloor AP' \rfloor}$  states. Let I be a one-to-one mapping from  $\Sigma$  to  $2^{AP'}$ . We define R and  $\Sigma_0$  as  $R = \Sigma \times \Sigma$  and  $\Sigma_0 = \Sigma$ . Then for a structure model  $K_c = (\Sigma, I, R, \Sigma_0)$ ,  $\eta$  is  $K_c$ -true if and only if  $\eta$  is satisfiable.  $K_c$  can be constructed in  $O(2^{2 |\eta|})$  time.

(Q.E.D.)

### 5. Implementation of a Model Checker and Verification Examples

Although the computational complexity of the model-checking problem is non-elementary for the length of a given RTL formula, as shown in Theorem 4, Theorem 3 states that the model-checking algorithm given in Section 4.2 can execute model checking in a time proportional to the size of a give structure model (that is,  $|\Sigma| + |R|$ ) for a given fixed formula. In order to evaluate our model-checking algorithm, we implemented it on a SUN 3/60 workstation as an RTL model checker.

#### 5.1. RTL Model Checker

In the RTL model checker, RTL formulas are stored basically as labeled directed acyclic binary graphs in the usual way. Labels are associated with nodes and represent either operators or atomic propositions. The graphs that represent a given formula and its subformulas are registered in an internal table. Among the subformulas generated by derivations, those that will/may appear again later are compared with the registered formulas. If the same formula has been already registered, the registered one is used and the nodes used in the generated formula are released to save space; otherwise, the generated formula is registered in the internal table.

In addition to the model checking of a given specification written in RTL, the RTL model checker can produce a sequence of states that contradicts the specification if it is not satisfied. Furthermore, it can show why the specification is not satisfied by representing a state and a subformula that make the specification false. This facility is very useful for analyzing design errors when a specification is not satisfied.

#### 5.2 Varification of a Traffic Controller

As a test of its efficiency, the RTL model checker has been used for design verification of a traffic controller [1]. The traffic controller is stationed at the intersection of a two-way highway going north and south and a oneway road going east. It has three input signals (N, S, and E), three output signals ( $N_GO$ ,  $S_GO$ , and  $E_{-}GO$ ), and five internal signals. N (north), S (south), and E (east) indicate that there is at least one car whose driver intends to cross the intersection to the north, south, and east, respectively.  $N_{-}GO$ ,  $S_{-}GO$ , and  $E_{-}GO$ indicate that the traffic light for the corresponding direction is green. The controller is designed as a Moore machine. One design, a 'bad design,' which has some design errors, has 43 states and its corresponding structure model has 344 states, while the other (a 'good design') has 31 states and its corresponding structure model has 248 states.

The full specification *spec* for the traffic controller is written in RTL, as shown in Fig. 6. nocoli states that the traffic lights for the east direction and the northsouth direction never both become green at the same time. ic represents the input constraints that once N, S, and E have been asserted, they are never turned off until  $N_{-}GO$ ,  $S_{-}GO$ , and  $E_{-}GO$  are turned on, respectively. asn4, ass4, and ase4 represent the situation in which at least one driver intends to cross the intersection in the corresponding direction while there are no cars in directions orthogonal to it. ngoby4, sgoby4, and egoby4 state that the traffic lights will be green for the corresponding direction within four units of time including the present one. spec specifies that the traffic lights in mutually orthogonal directions never both become green at the same time, and that if a car arrives at the intersection and there are no cars in deirections orthogonal to

```

len2 ≜

\bigcirc(LEN1)

len3

\bigcap(len2)

lengt3

\neg(LEN1 \lor len2 \lor len3)

nocoli ≙

\Box(\neg(E\_GO \land (N\_GO \lor S\_GO)))

icn ≜

\neg ((\Box(N \land \neg N GO)) : \neg N)

△

\neg((\Box(S \land \neg S \Box GO)) : \neg S)

ics

\neg((\Box(E \land \neg E \Box GO)) : \neg E)

ice

\square(icn \land ics \land ice)

asn4 ≜

N \land \neg E \land lengt3

ass4 ≜

S \wedge \neg E \wedge lengt3

ase4

E \wedge \neg (N \vee E) \wedge lengt3

ngoby4

N\_GO \lor \bigcirc (N\_GO \lor \bigcirc (N\_GO \lor \bigcirc N\_GO))

sgoby4

S\_GO \lor \bigcirc (S\_GO \lor \bigcirc (S\_GO \lor \bigcirc S\_GO))

egoby4 ≜

E\_GO \lor \bigcirc (E\_GO \lor \bigcirc (E\_GO \lor \bigcirc E\_GO))

delay4 ≜

ic \Rightarrow (\Box(asn4 \Rightarrow ngoby4) \land \Box(ass4 \Rightarrow sgoby4) \land \Box(ase4 \Rightarrow egoby4))

spec \stackrel{\triangle}{=} nocoli \land delay4

```

Fig. 6 Specification of a traffic controller.

it, then the traffic light for its direction will becomes green within four units of time including the present one so long as input constraints are satisfied.

spec contains 89 operators, and the RTL model checker found that —spec is true for the bad design in 0.2 seconds when an additional 62 expression nodes are used. —spec becomes false for the good design in 1.1 seconds when an additional 322 expression nodes are used. The required time and space seem to be reasonable from a practical point of view.

#### 5.3 Verification of a DMA Controller

As an example of verification of sequential machines with larger numbers of states, degign verification has been also done for a DMA controller [2]. The DMA controller is designed as a Moore machine with five input signals and 15 output signals. One design (a 'bad design'), which contains some design errors, has 392 states and its corresponding structure model has 12,544 states. The other (a 'good design') is a corrected version and has 272 states. Its corresponding structure model has 8704 states.

Figure 7 shows the assertions for the DMA controller. The assertion as 1 states that if MemReq is always high (that is, true) then ActivateComparator is always low (that is, false), and if MemReq is always low then *MemGrant* is also always low. as 2 states that it is always true that if CpuReq is high and DmaReq is low then CpuReq will eventually become low exactly two clocks after MemFinished is asserted. as3 states that if TransferRea becomes high then DmaRea will eventually be high the next time that DeviceReady is high. as4 states that if DmaReq is high and ActivateComparator and ComparatorSet will be high at some time, then either DmaEnd or DmaCont will be high the next time that DeviceReady is high. as5 states that ActivateComparator and MemGrant never become high at the same time. as6 states that DmaType never changes its value while TransferReq is high. as 7 and as 8 state that if ComparatorSet is high then the value of DmaDone never changes until DmaEnd or DmaCont becomes high. as 9

```

len2 \( \text{\text{$\sigma}}\) \( \text{$\color{\text{$\color{1}}}\)

lengt2 \stackrel{\triangle}{=}

\neg(LEN1 \lor len2)

as1

(\Box MemReq \Rightarrow \Box \neg ActivateComparator) \land (\Box \neg MemReq \Rightarrow \Box \neg MemGrant)

as2

\Box((CpuReg \land \neg DmaReg) \Rightarrow \Diamond((MemFinished \land lengt2) \Rightarrow \bigcirc) \bigcirc \neg CpuReg))

as3

\square((\neg TransferReq \land \bigcirc TransferReq) \Rightarrow \bigcirc(\Diamond(DeviceReady \Rightarrow (LEN1 \lor \bigcirc DmaReq))))

as4 ≜

\Box(DmaReq \Rightarrow \Diamond(ActivateComparator \Rightarrow \Diamond(ComparatorSet \Rightarrow \Diamond(Comparator

(LEN1 \lor \bigcirc (DmaEnd \lor DmaCont)))))

a 45

\neg \Diamond (ActivateComparator \land MemGrant)

as6

≙

\Box(\neg(TransferReq \land \bigcirc TransferReq \land (DmaType \oplus \bigcirc DmaType)) \lor LEN1)

≙

as7

\Box((DmaDone \land ComparatorSet) \Rightarrow (DmaEnd \lor \Box DmaDone \lor (\Box DmaDone : DmaEnd)))

≙

as8

\Box((\neg DmaDone \land ComparatorSet) \Rightarrow (DmaCont \lor \Box(\neg DmaDone)\lor)

(□¬DmaDone: DmaCont)))

≙

\square(\neg(\neg ActivateComparator \land \bigcirc ActivateComparator \land ComparatorSet))

a s 9

asall \quad \stackrel{\triangle}{=} \quad as1 \wedge as2 \wedge as3 \wedge as4 \wedge as5 \wedge as6 \wedge as7 \wedge as8 \wedge as9

```

Fig. 7 Assertions for a DMA controller.

Table 1 Verification of the DMA controller.

| Assertion | #Op. | DMA Controller (5 input, 15 output)                     |               |       |                                                         |            |       |

|-----------|------|---------------------------------------------------------|---------------|-------|---------------------------------------------------------|------------|-------|

|           |      | Bad Design (392 states)<br>Structure model 12544 states |               |       | Good Design (272 states)<br>Structure model 8704 states |            |       |

|           |      | Result                                                  | Time<br>(sec) | #Node | Result                                                  | Time (sec) | #Node |

| as1       | 10   | O.K.                                                    | 0.8           | 4     | O.K.                                                    | 1.5        | 4     |

| as2       | 13   | O.K.                                                    | 46.1          | 46    | O.K.                                                    | 29.5       | 46    |

| as3       | 10   | O.K.                                                    | 16.0          | 13    | O.K.                                                    | 9.6        | 13    |

| as4       | 9    | O.K.                                                    | 18.2          | 15    | O.K.                                                    | 11.4       | 15    |

| as5       | 3    | O.K.                                                    | 14.0          | 1     | O.K.                                                    | 8.8        | 1     |

| as6       | 8    | O.K.                                                    | 18.2          | 14    | O.K.                                                    | 11.9       | 14    |

| as7       | 8    | Fail                                                    | 0.6           | 12    | O.K.                                                    | 9.9        | 12    |

| as8       | 11   | Fail                                                    | 1.0           | 12    | O.K.                                                    | 9.9        | 12    |

| as9       | 6    | Fail                                                    | 0.7           | 6     | O.K.                                                    | 10.3       | 6     |

| asall     | 86   | Fail                                                    | 3.5           | 397   | O.K.                                                    | 70.6       | 915   |

states that ComparatorSet is never high just before ActivateComparator becomes high. asall is a logical conjunction of as1 to as9.

Table 1 shows the results of verification. The column '#Op.' shows the number of operators contained in assertions. The column '#Node' shows the number of expression nodes used in the verification process, excluding the nodes needed to store the given assertions themselves. Each assertion is checked independently. The RTL model checker finds that assertions as 7, as 8, as 9, and asall are not satisfied by the bad design. The number of operators in each assertion varies from 3 to 86. The time needed to verify them varies from 0.6 to 70.6 seconds, which is acceptable from a practical point of view. In particular, design errors are detected much faster in general.

For the good design, it takes about 100 sec in total to check as 1 to as 9 independently, whereas it takes only 70 sec to verify asall. This is because that the checker handles as 1 to as 9 at the same time, and the results for a subformula of some assertion may be used in checking other assertions. On the other hand, the total number of nodes needed as 1 to as 9 is 123; whereas it is 915 for asall.

#### 6. Conclusion

In investigating the finite and/or infinite behaviors of finite automata, we have shown four classes of regular temporal logic that are expressively equivalent to finite automata. We also discussed the verification problem for sequential machines by using regular temporal logic. As one approach to this problem, we described a model-checking method in which a given sequential machine is first converted to a corresponding structure model and the correctness of a given specification written in RTL is then checked. The computational complexity of the model-checking problem is non-elementary with respect to the length of a given formula, but we also proposed an efficient model-checking algorithm that runs in a time proportional to the size of a structure model. Furthermore, we implemented a model checker based on the proposed algorithm. Examples of verification of practically sized sequential machines show that the checker runs in reasonable time and space, and we believe that the model-checking approach based on RTL is very useful for formal logic design verification.

#### Acknowledgements

The authors would like to express their appreciation to Prof. E. M. Clarke of CMU who supported this research by providing various utilities, including design data for the traffic controller and the DMA controller. They also wish to thank Dr. N. Takagi, Dr. N. Ishiura, and members Prof. Yajima's Laboratory at Kyoto University for their valuable discussions.

#### References

- 1. BROWNE, M. C., CLARKE, E. M., DILL, D. L. and MISHRA, B. Automatic verification of sequential circuits using temporal logic. *IEEE Trans. Comput.*, C-35(12) (December 1986), 1035-1044.

- CLARKE, E. M., BOSE, S., BROWNE, M. C. and GRUMBERG, O. The design and verification of finite state hardware controllers. Technical Report CMU-CS-87-145, Carnegie Mellon University (July 1987).

- 3. CLARKE, E. M. and EMERSON, E. A. Synthesis of synchronization skeletons for branching time temporal logic. In *Proc. Workshop on Logic of Programs*, Springer-Verlag (1981), 52-71.

- 4. CLARKE, E. M., ÉMERSON, E. A. and SISTLA, A. P. Automatic verification of finite state concurrent systems using temporal logic specifications: A practical approach. Technical Report CMU-CS-83-152, Carnegie Mellon University (1983).

- 5. FUJITA, M., TANAKA, H. and MOTOOKA, T. Verification with Prolog and temporal logic. In *Proc. 6th Int. Symp. Computer Hardware Description Language* (1983), 103-114.

- 6. Hiraishi, H. Design verification of sequential machines based on a model checking algorithm of  $\varepsilon$ -free regular temporal logic.

- Technical Report CMU-CS-88-195, Carnegie Mellon University (1988).

- 7. HIRAISHI, H. Design verification of sequential machines based on e-free regular temporal logic. In *Proc. 9th Int. Symp. Computer Hardware Description Language* (1989), 249-263.

- 8. Hughes, G. E. and Cresswell, M. J. An Introduction to Modal Logic. Methouen, London (1977).

- 9. Moszkowski, B. Reasoning about digital circuits. Technical Report STAN-CS-83-790, Stanford Univ., (1983).

- 10. RESCHER, N. and URQUHART, A. Temporal Logic. Springer-Verlag, 1971.

- 11. UEHARA, T., SAITO, T., MARUYAMA, F. and KAWATO, N. DDL verifier and temporal logic. In *Proc. 6th Int. Symp. Computer Hardware Description Languages* (1983), 91-102.

- 12. WOLPER, P. Temporal logic can be more expressive. In Proc. of 22nd Annual Symposium on Foundations of Computer Science (1981), 340-348.

- (1981), 340-348.

13. WOLPER, P., VARDI, M. Y. and SISTLA, A. P. Reasoning about infinite computation paths. In *Proc. 24th Symp. on the Foundations of Computer Science* (1983), 185-194.

- 14. HAMAGUCHI, K., HIRAISHI, H., YAJIMA, S. Temporal logic expressively equivalent to an  $\omega$  regular set. Technical Report, COMP 88-8, *IEICE Japan* (May 1988).

- 15. Hamaguchi, K., Hiraishi, H. and Yajima, S. Formal verification of sequential machines using an  $\omega$  model-checking algorithm of  $\infty$  regular temporal logic. Technical Report, COMP89-24, *IEICE Japan* (June 1989).

- 16. HIRAISHI, H., HAMAGUCHI, K., YAJIMA, S. Satisfiability algorithm for regular temporal logic. *Trans. IPS Japan*, 30, 3 (March 1989), 366-374.

- 17. Hiraishi, H., Yajima, S. RTL: Regular temporal logic expressively equivalent to a regular set. *Trans. IPS Japan*, 28, 2 (Feb. 1987), 117-123.