[招待論文]

# 半導体技術ロードマップの最新動向

## 穂苅 泰明

社団法人 電子情報技術産業協会

〒101-0062 東京都千代田区神田駿河台 3-11

E-mail: y-hokari@jeita.or.jp

**あらまし** 国際半導体技術ロードマップ ITRS 2001 年版が 2001 年 12 月に公開された。前回の 1999 年版の刊行から 2 年が経過し今回大幅に改定された。本稿ではロジック・メモリ技術および配線技術を中心に改定の内容と特徴を紹介する。

**キーワード** 半導体集積回路、Siデバイス、LSI、半導体ロードマップ

# Review of the ITRS 2001 Technology Roadmap

#### Yasuaki HOKARI

Japan Electronics & Information Technology Industries Association 11, Kanda-Surugadai 3-chome, Chiyoda-ku, Tokyo 101-0062, Japan E-mail: y-hokari@jeita.or.jp

**Abstract** The new edition "ITRS 2001" has bee opened for publication on Dec. 2001. The new technology trend is reviewed from the point of view of logic & memory and interconnects, compared with the old edition ITRS 1999.

Keyword Integrated Circuits, Si-Devices, LSI, Semiconductor Technology Roadmap

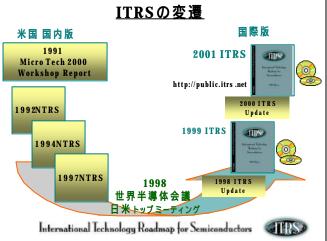

# 1. はじめに

2001 年版の ITRS(International Technology Roadmap for Semiconductors)が 2001 年 12 月に公開[1] された。 ITRS ロードマップは、1998 年に世界 5 極(米国、日本、欧州、韓国、台湾)協調で検討が開始され、初版が 1999 年に公開[2]、2年を経過し今回大幅な改定が行われた。

LSI(Large Scale Integration)技術は、リソグラフィ、成膜、エッチング、トランジスタ、配線、アセンブリなど、多くの技術から構成される。新技術が量産に適用されるまでには5年~10年もの長い時間を要する。LSI技術を継続的に発展させるためには、これら技術が周到に準備され、タイミング良く量産に適用されることが必要である。このような観点から、各技術の中長期的進展を予測するロードマップが作られている。

本稿では今回新しく公開された 2001 年版について特徴を紹介するとともに、デバイス関連技術を中心に 1999 年版との比較を交えて変更点を紹介する[3,4]

# 2. 2001 年版の特徴

2001 年版では、1999 年版で不明確であったいくつかの項目を定義することで、いつどんな技術が必要となるかを明確にしている。

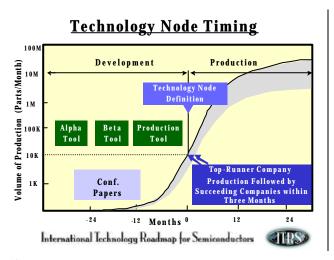

#### (1) 量産のどの時点の技術であるかを明確化

ITRSでは量産に適用された技術をベースに、いつどんな技術が必要となるかをロードマップとして示している。従って、量産のどの時点を基準にロードマップの時間軸に示すかの定義は重要である。ITRS 2001 年版では、「あるメーカがその技術を用いて生産を立上げ、月産のチップ数が1万個に達し、別のメーカが3ケ月以内に追従するとき」と定義している。

#### (2) 技術世代(テクノロジノード)数値の見直し

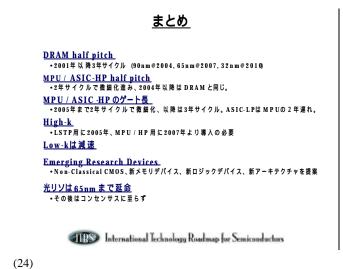

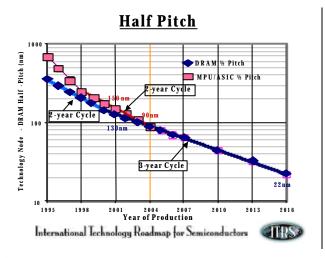

ITRS ロードマップは、R. Dennard により提唱されたスケーリング則[5]、すなわち「3年で集積密度が4倍というペースで微細化が進む」とする予測が基本となっている。技術世代は最小加工寸法(ハーフピッチ)によって表現され、ハーフピッチが0.7倍になった時点で技術世代が進んだと定義される。2001年版では2001年の130nmテクノロジノードを基準とし、この定義がより厳密に適用された結果、90nm、65nm、45nm、

32nm、22nm で進むと再定義された。

# (3) 最小加工寸法(ハーフピッチ)を定義

最小パターン寸法は回路パターンの粗密に依存することから、規則的なパターンで構成される DRAM セル部のメタル配線最小ピッチの半分(DRAM ハーフピッチ)で定義している。一方、MPU や ASIC のような不規則な回路パターンでは、同寸法のパターン形成は難しい。このため 2001 年版では、MPU/ASIC に対する最小パターン寸法として、ポリシリゲート電極パターンの最小ピッチの半分で定義した"MPU/ASIC ハーフピッチ"を新規に導入している。

#### (4) テクノロジノードの加速

1999 年版から 2 年を経過し、ロードマップに記述された数値に先行する技術が量産適用されるようになった。2001 年版ではこれを反映して数値の加速が行われ、2001 年の DRAM ハーフピッチが 1 年前倒しとなった。

# 3. デバイス技術関係のトピックス

#### 3.1. ロジック・メモリ技術

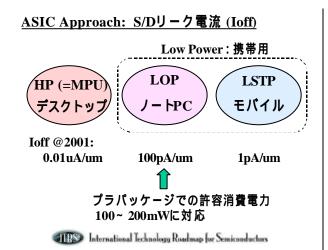

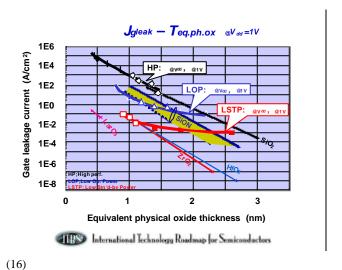

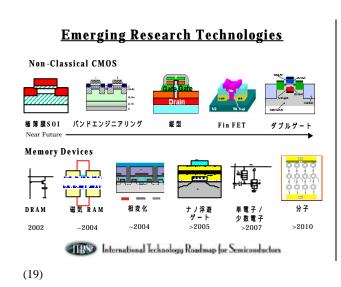

ロジックでは、Trの物理ゲート長(Ph. GL)と露光ゲート長(Printed GL)とを明確に定義するとともに、数値の大幅な改定が行われた。ポイントは、(1) Physical GLが 2001 年 65nm と 4 年加速されたこと、(2) Trが HP (High Performance), LP (Low Power)の 2 種類から HP, LOP (Low Operating Power), LSTP (Low Standby Power)の 3 種類になったこと、(3) Tr性能を向上させる新構造や手段の調査結果(Emerging Research Devices 章)を新規に追加したことである。

第(1)項は、テクノロジノードの加速と量産技術の進展を反映させたものである。第(2)項は、同一チップに高速 Tr と低消費電力 Tr を混載する SoC 化の動向を踏まえたものである。ここで大きな課題として注目されるのが、ゲート絶縁膜の薄膜化により膜に流れるリーク電流である。低消費電力 LSTP Tr のゲートリーク電流を 1pA/um に設定しているが、これを満足させるには従来の SiO2 や SiON 系膜では能力不足で、2005 年には新材料の絶縁膜(High-k 膜)が必要との予測となった。

一方、HP Tr ではドライブ能力を得るためにチャネルリーク電流(Ioff)を増加せざるを得ず、消費電力の増加が課題となる。Ioff を増加せずにドライブ能力を得る新しい手段が必要であり、第(3)項は現在知られる技術を整理し有望と思われる技術の開発を促進させようとする趣旨で追加された。調査対象としては、Tr 構造、新メモリ/ロジック、新アーキテクチャなど、多岐にわたる技術をカバーしている。

メモリに関しては、テクノロジノードが加速された ことをふまえて DRAM ロードマップが見直されたこ と、および今回新たに FeRAM のロードマップが追加されたことが特徴である。

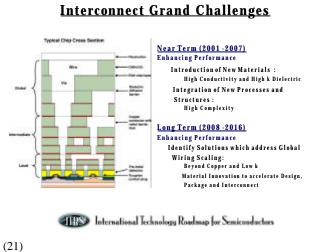

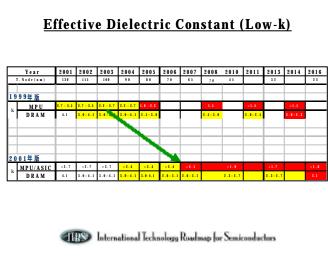

#### 3.2. 配線技術

2001 年版では、クロック周波数(Local clock)は 2007年に 6.7GHz、2016年には 28.7GHz と予測している。高速化のトレンド実現のために、配線材料には Cu を、層間絶縁膜には誘電率の低い Low-k 材料を適用するとし、配線層数は 2007年で 10層、2016年で 11層と予測しているが課題は大きい。1999年版では Low-k 材料に対する期待が大きく、誘電率の仕様が厳しすぎた。Low-k 膜の開発は困難を極めており、2001年版では1999年版の 4年遅れに緩和された値となっている。結論からすれば材料/プロセスで高速化に対処するのは厳しい状況にあり、チップ全体を高速の同一クロックで動作させるのは極めて難しい。設計側の工夫、例えば基本ブロック内を高速動作しブロック間は中速動作させるといった新しいアーキテクチャに期待したい。

#### 4. まとめ

ITRS 2001 年版の概要を述べた。1999 年版に比べ技術の前倒しと繰延べとが混在する結果となった。しかし、依然として技術開発が直面する大きな壁(Red Brick Wall)は 2005~2006 年に存在する。これを克服するべく各分野技術者の新しい発想とたゆまぬ努力に期待したい。

#### 謝辞

本稿をまとめるにあたり、STRJ 半導体技術ロードマップ専門委員会の増原利明委員長(MIRAI)、福島敏高同副委員長(富士通)、吉見信同副委員長(東芝)、その他STRJ ロードマップ関係者に多大なご協力をいただきました。この場をお借りし厚く感謝を申し上げます。

#### マ 献

- [1] ITRS2001 Web site, <a href="http://public.itrs.net/">http://public.itrs.net/</a>, および International Technology Roadmap for Semiconductors (2001 Edition), 発行 JEITA.

- [2] International Technology Roadmap for Semiconductors (1999 Edition),発行 JEITA.

- [3] STRJ(半導体技術ロードマップ専門委員会)ワークショップ, 1/15-16, 2002.

- [4] 吉見信, "国際半導体ロードマップ(ITRS2001)報告", JEITA Review, vol.3, No.5, 2002 (刊行予定).

- [5] R. Dennard et. Al.; "Design of Ion-Implanted MOSFETS with Very Small Physical Dimensions", IEEE, J. Solid State Circuits., SC-9, pp.256, 1974.

# **International Technology** Roadmap for **Semiconductors**

2001

# 半導体技術ロードマップ専門委員会 (STRJ)

International Technology Roadmap for Semiconductors

(1)

(4)

**Technology Node**

| 999版 |   |       |     |   |    |   | 2001版<br>(nm) |

|------|---|-------|-----|---|----|---|---------------|

| 100  | ⇒ | 130 x | 0.7 | ⇒ | 91 | ⇒ | 90            |

| 70   | ⇨ | 90 x  | 0.7 | ⇨ | 64 | ⇒ | 65            |

| 50   | ⇒ | 65 x  | 0.7 | ⇒ | 45 | ⇒ | 45            |

| 35   | ⇨ | 45 X  | 0.7 | ⇒ | 31 | ⇒ | 32            |

| 25   | ⇒ | 32 x  | 0.7 | ⇒ | 22 | ⇨ | 22            |

(5)

(2)

**Half Pitch** Pitch MPU/ASIC DRAM

International Technology Roadmap for Semiconductors

(3)

(6)

Trend of MOSFETs for SoC Node 350nm 250 nm 180nm 130 nm 100nm ÛHP (UHP) 10n~ HP HP HP 1n -10n (Core) Core Core (Core 100p - 1n Core (LP (LP (LP MOSFET 1p - 10p ULP (ULP 0.1p - 1p (Í/Ò): (1/0)(1/0)(1/0)(1/0)Analog (Analog (Analog) Number of gate ox. I<sub>off</sub>(A/mm) @ RT 2 2-3 2 TRS International Technology Roadmap for Semiconductors

(7) (10)

## Logic Roadmap の特徴 - 1

1. MPUの Ph. Gate Length の加速

#### 4年加速@2001

# TNサイクルの加速

(1999年版) 0.7×/3年サイクル (2001年版) 0.7×/2年サイクル (2001 - 2005の期間)

International Technology Roadmap for Semiconductors

Logic Roadmap の特徴 - 2

2. ASIC-LPを用途別に2つに分離

(1999) (2001) High Perform. HP

Low Power  $\implies$  LOP: Low Operation Power LSTP: Low Standby Power

- 3. FeRAMの Roadmapを新規に追加

- 4. Emerging Research Devices を調査し新規に追加

International Technology Roadmap for Semiconductors

(8) (11)

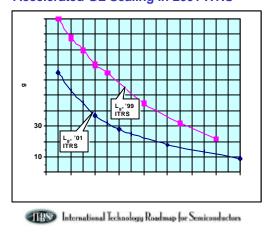

# **Accelerated GL Scaling in 2001 ITRS**

Low Power:携帯用

HP (=MPU)

デスクトップ

High speed

High Performance

Low Power

バッテリ容量からのニーズに基づく

(9)

ASIC Approach: Ioff & Ig

Ioffの取扱い

(13)

(14)

ASIC-HP

CV/I growth rateを 17%/年で維持

HP: 3倍/年で増加 -LOP: 3倍/3年で増加

LSTP: 1pA/umで維持

(2007以降3倍/3年で増加)

Ig(ゲートリーク)の取扱い

Ig max = Ioff と仮定

International Technology Roadmap for Semiconductors

|                                               | Technology Node     | 130nm   |          |          | 90nm    |         |         | 65nm    | 45nm    | 32nm                                                | 22nm    |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------|---------------------|---------|----------|----------|---------|---------|---------|---------|---------|-----------------------------------------------------|---------|--|--|--|--|--|--|--|--|--|

|                                               | Ph.GL (nm)          | 90      | 80       | 65       | 53      | 45      | 37      | 32      | 22      | 16                                                  | 11      |  |  |  |  |  |  |  |  |  |

| OP                                            | EOT (nm)            | 2.0-2.4 | 1.8-2.2  | 1.6-2.0  | 1.4-1.8 | 1.2-1.6 | 1.1-1.5 | 1.0-1.4 | 0.8-1.2 | 0.7-1.1                                             | 0.6-1.0 |  |  |  |  |  |  |  |  |  |

|                                               | El.Thick.Adj.Factor | 0.8     | 0.8      | 0.8      | 0.8     | 0.8     | 0.8     | 0.5     | 0.5     | 0.5                                                 | 0.5     |  |  |  |  |  |  |  |  |  |

| ÷                                             | Vdd (V)             | 1.2     | 1.2      | 1.1      | 1.1     | 1       | 1       | 0.9     | 0.8     | 0.7                                                 | 0.6     |  |  |  |  |  |  |  |  |  |

| $\overline{c}$                                | Ioff (pA/um)        | 100     | 100      | 100      | 300     | 300     | 300     | 700     | 1000    | 3000                                                | 10000   |  |  |  |  |  |  |  |  |  |

| S                                             | Ion (uA/um)         | 600     | 600      | 600      | 600     | 600     | 600     | 700     | 700     | 800                                                 | 900     |  |  |  |  |  |  |  |  |  |

| ٧                                             | Tech. Improvement   | 0       | 0        | 0        | 0       | 0       | 0       | 0       | 10%     | 30%                                                 | 70%     |  |  |  |  |  |  |  |  |  |

|                                               | CV/I (ps)           | 2.55    | 2.45     | 2.02     | 1.84    | 1.58    | 1.41    | 1.14    | 0.85    | 0.56                                                | 0.35    |  |  |  |  |  |  |  |  |  |

|                                               | Device Performance  |         | 1.0      | 1.3      | 1.4     | 1.6     | 1.8     | 2.2     | 3.0     | 4.6                                                 | 7.2     |  |  |  |  |  |  |  |  |  |

| I.                                            | Ph.GL (nm)          | 90      | 80       | 65       | 53      | 45      | 37      | 32      | 22      | 16                                                  | - 11    |  |  |  |  |  |  |  |  |  |

| Ŀ                                             | EOT (nm)            | 2.4-2.8 | 2.2-2.6  | 2.0-2.4  | 1.8-2.2 | 1.6-2.0 | 1.4-1.8 | 1.2-1.6 | 0.9-1.3 | 0.8-1.2                                             | 0.7-1.1 |  |  |  |  |  |  |  |  |  |

| ST                                            | El.Thick.Adj.Factor |         | 0.8      | 0.8      | 0.8     | 0.8     | 0.8     | 0.5     | 0.5     | 0.5                                                 | 0.5     |  |  |  |  |  |  |  |  |  |

| H                                             | Vdd (V)             | 1.2     | 1.2      | 1.2      | 1.2     | 1.2     | 1.2     | 1.1     | 1       | 0.9                                                 | 0.9     |  |  |  |  |  |  |  |  |  |

| SIC                                           | Ioff (pA/um)        | 1       | 1        | 1        | 1       | 1       | 1       | 1       | 3       | 7                                                   | 10      |  |  |  |  |  |  |  |  |  |

| AS                                            | Ion (uA/um)         | 300     | 300      | 400      | 400     | 400     | 400     | 500     | 500     | 600                                                 | 700     |  |  |  |  |  |  |  |  |  |

| ~                                             | 1 ecn. improvement  | 0       | . 0      | 0        | 0       | 0       | 0       | 0       | 10%     | 30%                                                 | 50%     |  |  |  |  |  |  |  |  |  |

|                                               | CV/I (ps)           | 4.61    | 4.41     | 2.96     | 2.68    | 2.51    | 2.32    | 1.81    | 1.43    | 0.91                                                | 0.66    |  |  |  |  |  |  |  |  |  |

| _                                             | Device Performance  |         | 1.0      | 1.6      | 1.7     | 1.8     | 2.0     | 2.6     | 3.2     | 5.1                                                 | 7.0     |  |  |  |  |  |  |  |  |  |

| CV/I Growth rateは 14%/年 HPと同等の技術を適用 (ゲート膜を除く) |                     |         |          |          |         |         |         |         |         |                                                     |         |  |  |  |  |  |  |  |  |  |

|                                               | High-k が必要 (LSTP)   |         |          |          |         |         |         |         |         |                                                     |         |  |  |  |  |  |  |  |  |  |

|                                               | <b>GITR</b>         | So Int  | bernatio | mal Tech | nology  | Road    | ap for  | emicon  | ductors | International Technology Roadmap for Semiconductors |         |  |  |  |  |  |  |  |  |  |

LOP,LSTPの Ph. GLは HPの 2 年遅れ

(17)

**ASIC-LP**

|                      |         |         | Long Term |         |         |         |         |         |         |         |

|----------------------|---------|---------|-----------|---------|---------|---------|---------|---------|---------|---------|

| Calendar Year        | 2001    | 2002    | 2003      | 2004    | 2005    | 2006    | 2007    | 2010    | 2013    | 2016    |

| Technology Node      | 130nm   |         |           | 90nm    |         |         | 65mm    | 45nm    | 32mm    | 22nm    |

| Ph.GL (nm)           | 65      | 53      | 45        | 37      | 32      | 28      | 25      | 18      | 13      | 9       |

| FOT (nm)             | 1.3-1.6 | 1.2-1.5 | 1.1-1.6   | 0.9-1.4 | 0.8-1.3 | 0.7-1.2 | 0.6-1.1 | 0.5-0.8 | 0.4-0.6 | 0.4-0.5 |

| El.Thick.Adi, Factor | 0.8     | 0.8     | 0.8       | 0.8     | 0.8     | 0.8     | 0.5     | 0.5     | 0.5     | 0.5     |

| Tox ele. Fa. (nm)    | 2.3     | 2.1     | 2.0       | 2.0     | 1.9     | 1.9     | 1.4     | 1.2     | 1.0     | 0.9     |

| Vdd (V)              | 1.2     | 1.1     | 1.0       | 1.0     | 0.9     | 0.9     | 0.7     | 0.6     | 0.5     | 0.4     |

| Ioff (uA/um)         | 0.01    | 0.03    | 0.07      | 0.1     | 0.3     | 0.7     | 1       | 3       | 7       | 10      |

| Ion (uA/um)          | 900     | 900     | 900       | 900     | 900     | 900     | 900     | 1200    | 1500    | 1500    |

| Tech, Improvement    | 0       | 0       | 0         | 0       | 0       | 0       | 0       | 30%     | 70%     | 100%    |

| CV/I (ns)            | 1.65    | 1.35    | 1.13      | 0.99    | 0.83    | 0.76    | 0.68    | 0.39    | 0.22    | 0.15    |

| Device Performance   | 1.0     | 1.2     | 1.5       | 1.6     | 2.0     | 2.1     | 2.5     | 4.3     | 7.2     | 10.7    |

EOTの赤はSiONの膜厚制御・信頼性に課題

CV/I Growth rate 17%年を維持

International Technology Roadmap for Semiconductors

nMOS Ion: 1999年版との比較 1600 2001 HP 1400 nMOS Ion (uA/um) 1200 2001 LOP 1000 1999 HP 800 600 2001 LST 400 1999 LP 200 0 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 (Year) International Technology Roadmap for Semic

(15) (18)

FeRAM **Capacitor Structure** 1.00E+06 1.00E+04 1.00E+02 1.00E+01 1.00E+00 Planar Stack T. Node (nm 130 115 22 DRAM (bit) 8G 32G 64G 2 5 6 M 1 G FeRAM (bit 6 4 M 128 M 4 G 4 M planar planar 1T1C 1T1C 1T1C International Technology Roadmap for Semiconductors

(20)(23)