[フェロー就任記念講演]

# VLSI 設計自動化技術開発の過去、現在、将来

### 後藤 敏

早稲田大学大学院情報生産システム研究科 〒808-0135 北九州市若松区ひびきの2-7

E-mail: goto@waseda.jp

あらまし 電子情報通信学会フェロー記念講演会の予稿である。VLSI 設計の自動化は1970年代から研究が開 始され、過去30年間あまり、レイアウト設計、論理設計、機能設計、テスト設計の各分野で大きな 発展を遂げてきた。歴史を振り返り、今後何をすべきかに関して意見を述べる。

キーワード VLSI 設計、自動設計、システム LSI、レイアウト設計、論理設計、テスト設計

# VLSI design automation; Past, Present, and Fututure

Satoshi GOTO<sup>‡</sup>

Graduate School of IPS, Waseda University, 2-7, Hibikino, Wakamatsu-ku, Kitakyushu 808-0135 Japan E-mail: goto@waseda.jp

Abstract This manuscript is written for the invited presentation of IEICE Fellow nomination.. VLSI Deign Automation Technologies have been developed for more than 30 years in the area of layout design, logic design, functional design and test design since 1970. This report will describe what we have to do in future by looking back of the history of DA technologies.

Keyword VLSI design, Design automation, System LSI, Layout design, Logic Design, Test design

### VLSI設計自動化技術開発の 過去、現在、未来

2004年12月1日

早稲田大学大学院 情報生産システム研究科 後藤 敏

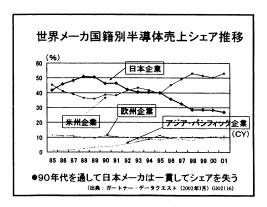

### 半導体産業の競争の<u>場の変遷</u>

80年代: 先端プロセス確立と製造力

- 旦プロセスを確立できれば、製造ライン管理カ に優れる日本型IDMが競争優位を獲得

NEC佐々木会長の講演より

90年代: 製品特化、機能特化による絶対的優位性 ●ノウハウの製造装置への取り込みにより、製造局面 での競争力確立が困難化

製品、機能を特化し、絶対的優位を実現できる企業が 競争優位を獲得

00年代:プロセス進化を活かしきる総合デザインカ ●デザイン競争力とプロセス競争力の融合がシステム

LSIの製品競争力

# システムLSIの量産までの期間 ・カラーTV: 12年 ・コンピュータ: 5年 ・携帯電話: 3年 ・PS-1: 10ヶ月 ・PS-2: 3ヶ月

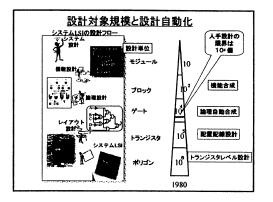

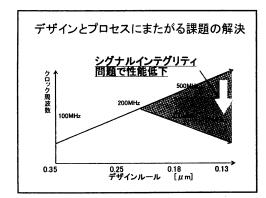

### 設計自動化の課題 ーシステムLSI 大規模化・微細化時の課題ー

- 1. 大規模化: LSI大規模化に伴い, 処理量が増大 ⇒設計が困難/時間がかかる

- 2. 高信頼化:設計対象複雑化で設計誤りの可能性大 ⇒誤り無く設計することが困難に

- 3. 高性能化:配線遅延やクロック・スキューが増大 ⇒性能が出ない

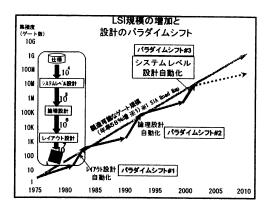

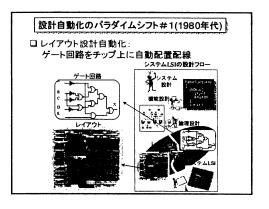

### 設計自動化のパラダイムシフト#1(1980年代)

- 1.自動配置・配線:レイアウトパターン図の自動生成 ゲートアレー、スタンダードセル、ビルデイングブロック

- 2.回路シミュレーション: SPICEプログラムの開発 バークレー校で開発し、世界で普及

- 3.論理シミュレーション:高速化手法の研究 論理シミュレーション・ハードを開発

- 4.テストパターン生成:組合わせ回路用パターン自動生成 順序回路対策(スキャンパス法の開発と実用化)

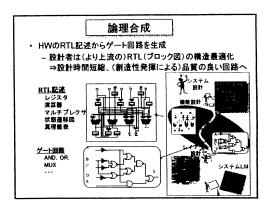

### 設計自動化のパラダイムシフト#2(1990年代)

- 1.論理合成:RT記述からゲート回路を自動合成 RTレベル(ブロック図)レベルで回路構造を最適化

- 2. 形式論理検証:回路の正しさをシミュレーションによらずに 数学的に検証。高速な検証、検証漏れなし

- 3.エミュレータ FPGA上で疑似回路を構築し、模擬実行で検証

- 4 論理合成&レイアウト連携 論理合成で配線遅延を考慮→遅延の早期収束

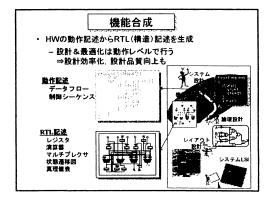

### 設計自動化のパラダイムシフト#3(2000年代)

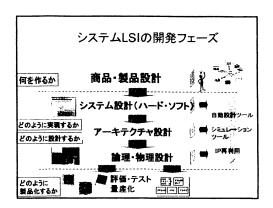

- 1. 上流設計の自動化 設計の上流化:機能合成 設計の階層化(分割設計):システム分割, フロアプラン

- 2. 高位レベルでの確認

設計資産の活用: IP(Intellectual Property)化 高位レベルでの確認:システムレベル検証 システムの擬似実行:システムエミュレーション

3 配線遅延の早期評価 機能合成~フロアプラン連携

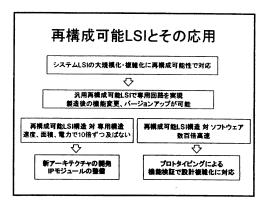

### 次なるパラダイムシフト

- ロ ソフトウエアとハードウエア設計の一体化 ・ソフトウェアからハード生成が大幅に普及

- □入力は仕様記述

- 発注者と半導体メーカとのインターフェイス仕様の仕様記述 の標準化

- □SOC設計からの脱皮

- \* SiP、SiSによる低価格開発と高性能化

- □動的な再構成可能機能をもつシステムLSI

- 高速、低消費電力で柔軟性をもったシステムLSIの設計

### システムLSI設計方法のあるべき姿

容易な設計 (コンセプトからチップへ)

1) チップ実現技術

e.g. CBIC,G/A, FPGA, ASIP, DSP, MPU 2) 設計方法論

e.g. C-based, IP reuse, Platform design

### **Target**

性能 スピード、低消費電力、チップサイズ

へに・、、 ・柔軟性 ・機能、保守性 ・設計期間(受注から市場まで)

・設計費用 (コスト,生産量.)

### システムLSIの分類 組込み型プロセッサー (e.g. ARM, V850,SH, R1000) ソフトウェア リコンフィギャラブ Xtensa, Mep ル・プロセッサー Retarnetab プログラマブル Retargetable DSP FPGA 静的 ハードウエ 勤的 DRP QuickSilver IPFlex 長いTAT CBIC ISSP, RapidChip, G/A 短いTAT プログラマブル

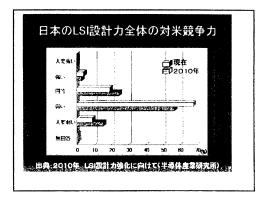

## 日本の設計技術力の強さをどこで 発揮させるか

- CADツールが米国勢に圧倒されたもとで、国内CADメーカが頑張れる領域はあるか。

- ・ 半導体メーカ自身が会社内で開発し発展させるCADツールは何か。

- ・ソフトウエア部品が米国に占領されたように、 IPコアも同じ道を歩まないか。

- インテグレーションカ(チップ化カ)だけで、日本の半導体メーカは生きていけるか。

# 半導体は米

システムLSIは 半導体(主食)と ソフトウエア(副食)