# DSM 配線とスーパーコネクトへの期待

#### 桜井 貴康

東京大学、国際・産学共同研究センター 〒153-8505 東京都目黒区駒場 4-6-1

E-mail: tsakurai@iis.u-tokyo.ac.jp

あらまし今後の電子システムを考えるとシステムインパッケージやグローバルインテグレーションの重要性が増す。そこでは、数十 $\mu$ m といったデザインルールを有するスーパーコネクト技術が活躍する。このようなスーパーコネクト技術は VLSI が直面する IR ドロップや RC 遅延といった問題を解決するにも有効である。また、ディープサブミクロン配線の諸問題の解決を考えるとき、インダクタンスなどボードやパッケージでの設計知識が役立つ可能性がある。

キーワード VLSI、DSM、配線、スーパーコネクト

## Deep Sub-Micron Interconnects and Expectation to Superconnect

Takayasu Sakurai

Center for Collaborative Research, and Institute of Industrial Science

University of Tokyo

4-6-1 Komaba, Meguro-ku, Tokyo, Japan, 153-8505

E-mail: tsakurai@iis.u-tokyo.ac.jp

Abstract Superconnect technology which is based on interconnections around 10um design rule is expected to realize new realm of electronic system integration together with System-on-a-Chip approaches. The superconnect technology will be helpful in solving deep submicron (DSM) interconnection issues of VLSI's such as IR voltage drop and RC delay problems. The accumulated knowledge database on board and package will be also useful in confronting DSM interconnection issues like inductive effects.

Key words VLSI, DSM, Interconnect, Superconnect

#### 1. Abstract

Superconnect technology which is based on interconnections around  $10\mu m$  design rule is expected to realize new realm of electronic system integration together with System-on-a-Chip approaches. The superconnect technology will be helpful in solving deep submicron (DSM) interconnection issues of VLSI's such as IR voltage drop and RC delay problems. The accumulated knowledge database on board and package will be also useful in confronting DSM interconnection issues like inductive effects.

#### 2. Scaling and Issues of Current LSI Technology

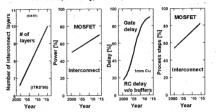

Taking a close look at the scaling law, we can see that the following three crises are leaning over the LSI technology.

- · Power crisis

- · Interconnection crisis

- · Complexity crisis

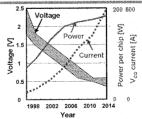

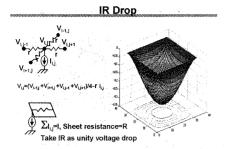

The power crisis is depicted in Fig.2. Lower operation voltage naturally increases operation current, which in turn requires thicker metal layers for the current to be distributed throughout the chip without IR-drop. One of the key approaches to low-power design is the memory embedding. By embedding memories, inter-chip communication power can be reduced by two orders of magnitude. The memory embedding, however, is an expensive option, since it increases process steps. A new system-level integration can be a solution to this problem.

As for the interconnection crisis, RC delay increase and IR-drop issue are some of the more stringent issues. Thicker metal layer used in an interposer/package/board may mitigate the problem.

Complexity crisis can only be solved by re-use of the pre-designed blocks and designing at higher abstraction level. Thus, System-on-a-Chip (SoC) where many pre-designed IP's are amalgamated at the higher abstraction is one of the candidates to cope with the complexity crisis. Future electronic systems, however, cannot be built only with the SoC, since many SoC issues have become evident as follows.

- · Huge initial investment for masks & development

- Un-distributed IP's (i.e. CPU, DSP of a certain company)

- · IP testability, upfront IP test cost

- · Process-dependent memory IP's

- Difficulty in high precision analog IP's due to noise

Process incompatibility with non-Si materials and/or MEMS

The huge investment in developing the SoC process to embed different kinds of technologies is one of the most vital issues.

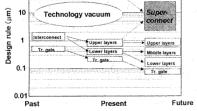

#### 3. Superconnect

Recently, however, a new system-level integration called 'superconnect' is attracting attention[1-4], which may solve SoC problems. The superconnect connects separately built and tested chips not by printed circuit boards but rather directly to construct high-performance yet low-cost electronic systems. The superconnect may use around 10 micron level design rules [4]. Sometimes LSI's in the superconnect are connected in three-dimensional fashion to achieve the higher performance and the smaller geometry. System-in-a-Package (SiP) composed of stacked chips using bonding or interposers is one realization of the superconnect. The superconnect mitigate IR-drop problems and RC delay problems.

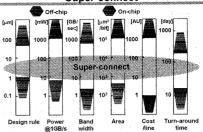

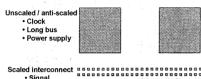

There has been a large gap between on-chip and off-chip interconnects in terms of power, density, performance, cost and turn-around-time. Basically, the large gap comes from the big difference between the design rules of on-chip and off-chip interconnects. It can be said that there is a technology vacuum at present between  $1\mu m$  level on-chip interconnect and  $100\mu m$  level off-chip interconnect. The superconnect will fill the gap between on-chip and off-chip interconnect, making use of  $10\mu m$  level design rule.

Some of the important issues in the future systemlevel integration are as follows.

- Special design tools for placement & route for co-design of LSI's and assembly

- High-density reliable substrate and metallization technology

- low-cost, available known good die (reworkablility and module testing)

#### 4. Issues in Deep Sub-Micron (DSM) Interconnects

The issues for DSM interconnects are summarized as follows:

Larger current

IR drop (static and dynamic)

Reliability (electro-migration)

Smaller geometry / Denser pattern

RC delay

Signal Integrity Crosstalk noise Delay fluctuation Higher speed

Inductance

**EMI**

Among others, IR drop and RC delay problems can have help from the superconnect technology. To fully utilize the merit of the thick metal layers of superconnect, codesign of VLSI and assembly will be necessary. As for inductive effects which appear in low resistance interconnects in VLSI's such as clock lines, power lines and wide buses, the knowledge accumulated in board and package designs will be transferred to VLSI community.

#### References

- [1] T.Sakurai, "Superconnect Technology," Trans. C of IEICE,

- [2] M.Koyanagi et al., "Neuromorphic Vision Chip Fabricated Using Three-Dimensional Integration Technology," ISSCC Digest of Tech. Papers, pp.270-271, Feb.2001.

- [3] K.Ohsawa, H.Odaira, M.Ohsawa, S.Hirade, S.G.Pierce, "3-D Assembly Interposer Technology for Next-Generation Integrated Systems," ISSCC Digest of Tech. Papers, pp.272-273, Feb.2001.

- [4] M.Kimura, "Superconnect: 21st Century LSI Production and Design Method", Nikkei Microdevices, no 180, pp.62-79, June 2000.

Scaling Law

| Transistors                                                                                                           |                                                                                                          | Scaling coefficients                         |                                                                                                                                                                                                                                                                                          | 1                                   |  |                                        |  |  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|----------------------------------------|--|--|

| V <sub>CO</sub> Tr. dimensions Drain current Gate capacitance Tr. delay Tr. power Power density Tr. density Intercon  | [V] [K] [I~1/x x/x V^1,3] [C~1/x xx] [d~CVI] [d~CVI] [P~V ~CVV/d] [p~P/x/x] [n~1/x/x]                    | 1                                            | $K=2$ $j_{to} = \frac{\mu_0}{t_{to}} \int_{L} \frac{(\xi_{to} - T_t)^2}{2} \sim \frac{\pi^2 / t_1}{2}$ T. Sabasatá A. Návedná, A jeha-pover leve MOSPET model and its optication in C. MOS invaries college and other formulas; MEEQ LSSC invaries college and other formulas; MEEQ LSSC |                                     |  |                                        |  |  |

| Type<br>Scaling scenario                                                                                              |                                                                                                          | Local<br>Scaled                              | Global<br>Anti-scaled                                                                                                                                                                                                                                                                    | vol25, no.2, pp.584-594, Apr. 1990. |  |                                        |  |  |

| Line Ihickness<br>Width<br>Separation<br>Oxide thickness<br>Length<br>Resistance<br>Dapacitance<br>RC defay/Tr. defay | (T) [W] [S] [H] [R <sub>H1</sub> ~L/W/T] [C <sub>H1</sub> ~L/W/H] [D~R <sub>H2</sub> C <sub>H1</sub> /d] | 1 Ak<br>1 Ak<br>1 Ak<br>1 Ak<br>1 Ak<br>1 Ak | k<br>k<br>t<br>t<br>t/k<br>k                                                                                                                                                                                                                                                             | ##<br>##                            |  | ************************************** |  |  |

| Current density<br>DC noise / V <sub>oo</sub>                                                                         | [N-JWTRA]                                                                                                | -                                            | **                                                                                                                                                                                                                                                                                       |                                     |  |                                        |  |  |

## Scaling Law

Favorable effects Size x1/2 Voltage x1/2 Electric Field v1 Speed Cost x1/4

Unfavorable effects Power density x1.6 RC delay/Tr, delay x3.2 Current density x1.6 Voltage noise x3.2 Design complexity x4

#### Issues in System-on-Chip

- Un-distributed IP's (i.e. CPU, DSP of a certain company)

- Low yield due to larger die size

- Huge initial investment for masks & development

- IP testability, upfront IP test cost

- Process-dependent memory IP's

- Difficulty in high precision analog IP's due to noise

- Process incompatibility with non-Si materials and/or MEMS

#### SoC vs. SiP

- Smaller area Shorter interconnect Optimized process for each die (Analog, DRAM, MEMS...) Good electrical isolation

- Through-chip via

- Heat dissipation is an

## Superconnect example based on three-dimensional assembly

#### Issues in superconnect

- · Special design tools for placement & route for codesign of LSI's and assembly

- High-density reliable substrate and metallization technology

- · Low-cost, available known good die (reworkablility and module testing)

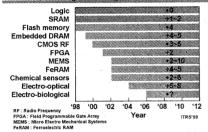

## Technologies integrated on a chip

## New system level integration

- SoC : High-performance but issues remain

- Printed circuit board (PCB): Low-performance

- New system level integration : Superconnect

- Connects separately built and tested chips not by the PCB but rather directly to construct high-performance yet low-cost electronic systems

- May use around 10 micron level design rules

Super-connect Package Package 10 Technology vacuum

Nikkel microdevices

Super-connect

#### Interconnect determines cost & perf.

P: Power, D: Delay, A: Area, T:Turn-around

#### DSM interconnect design issues

Larger current

IR drop (static and dynamic) Reliability (electro-migration)

Smaller geometry / Denser pattern RC delay Signal Integrity

Crosstalk noise Delay fluctuation

Higher speed Inductance EMI

#### VDD, Power and Current Trend

## Interconnect Cross-Section and Noise

• Signal

1V 20W → 20A current 2% noise on VDD & VSS → ~0.02V / 20A → ~10µm thick Cu Thick layer interconnect, area pad, package are co-designed.

## Interconnect parameters trend

onductor Industry Association road totes.sematech.org/1997pub.htm

#### RC delay and gate delay

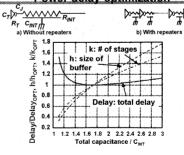

### Repeaters

#### Buffered interconnect delay

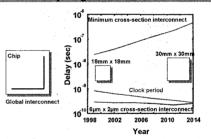

### RC delay of global interconnections

## Power delay optimization

#### Skin Depth and R Increase

### Shorter interconnect in 3-D assembly

System on a chip

3-D assembly

$\frac{\# \ of \ devices \ in \ d(3D)}{\# \ of \ devices \ in \ d(2D)} = \frac{1}{3} \left( 2 \frac{d}{h} + \frac{h}{d} \right)$

$\approx \frac{2}{2}(\#of stacked chips in d)$

d: Manhattan distance

h: Height between chips

### Inductive Effects in Clock Lines

Board design practice is imported in LSI.

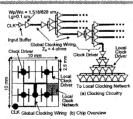

#### H-tree clock distribution

M.Mizuno, K.Anjo, Y.Sumi, H.Wakabayashi, T.Mogami, T.Horiuchi, M.Yamashina, "On-Chip Multi-GHz Clocking with Transmission Lines," ISSCC, pp.366-367, Feb. 2000

#### Reverse temperature dependence

Photograph of 32bit FA 0.3µm CMOS

K.Kanda, K.Nose, H.Kawaguchi, and T.Sakurai, "Design Impact of Positive Temperature Dependence of Drain Current in Sub 1V CMOS VLSI's", CICC99, pp. 563-566, May 1999.

### LSI in 2014

| Year                   | Unit      | 1999 | 2014  | Factor |

|------------------------|-----------|------|-------|--------|

| Design rule            |           | 0.18 | 0.035 |        |

| Tr. Density            | /cm2      | 6.2M | 390M  | 30     |

| Chip size              | mm2       | 340  | 900   | 2.6    |

| Tr. Countperchip ( )   |           | 21M  | 3.6G  |        |

| DRAM capacity          | 1         | 1G   | 1T    | 1000   |

| Local clock on a chip  | Hz        | 1.2G | 17G   |        |

| Global clock on a chip | Hz        | 1.2G | 3.7G  | 3.1    |

| Power                  | W         | 90   | 183   |        |

| Supply voltage         | V         | 1.5  | 0.37  |        |

| Current                | . A       | 60   | 494.6 |        |

| Interconnection levels |           | 6    | 10    | 1.7    |

| Mask count             |           | 22   | 28    | 1.3    |

| Cost / tr. (packaged)  | en ts     | 1735 | 22    | 0.01   |

| Chip to board clock    | Hz        | 500M |       |        |

| # of package pins      |           | 810  | 2700  |        |

| Package cost           | cents/pin | 1.61 | 0.75  | 0.5    |

International Technology Roadmap for Semiconductors 1998 update sponsored by the Semiconductor Industry Association in cooperation with European Electronic Component Association (EECA), Electronic Industries Association of Japan (EIAL), Korea Semiconductor Industry Association (KSIA), and Taiwan Semiconductor Industry Association (TSIA), International Technology Roadmap for

### Possible electronic system in 2014

MPU; Logic Configurable units

- Sensors/actutors

- 0.035µm 3.6G Si FET's with VTH & VDD control

- Locally synchronous 17GHz clock, globally asynchronous

- Chip / Package / Board system co-design for power lines, clocks, and long wires (superconnect)