## [招待論文] Design-Manufacturing Interface for .13 um and below

Andrzej Strojwas

Carnegie Mellon University, Pittsburgh, PA15213 & PDF Solutions Inc. San Jose, CA9511

E-mails: ajs@ece.cmu.edu & ajs@pdf.com

## **Extended Summary:**

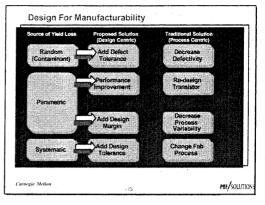

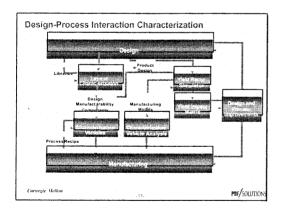

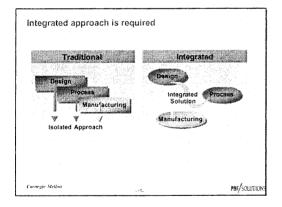

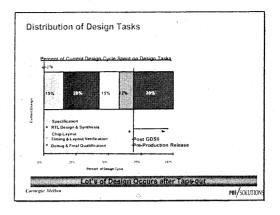

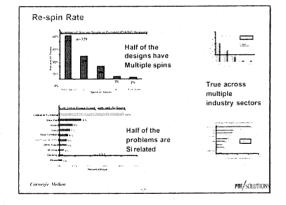

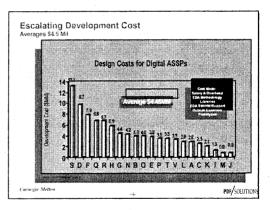

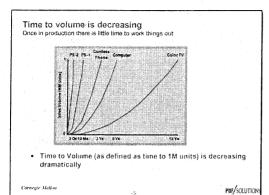

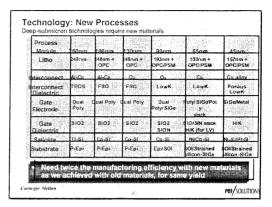

This talk will present the requirements for the design-manufacturing interface for the upcoming generations of ULSI technologies. We will start by presenting an overview of trends in semiconductor industry; accelerated roadmap which leads to further miniaturization, the increasing role of manufacturing fluctuations, shrinking time to market, product complexity (including SOC) and the overall disaggregation of semiconductor industry (emergence of fabless companies and increasing role of foundries in manufacturing). Then we will discuss the present, isolated approach to process development, product design and manufacturing. We will illustrate the current practices by several examples of state-of-the-art Design For Manufacturability (DFM) approaches showing both the EDA tools and databases.

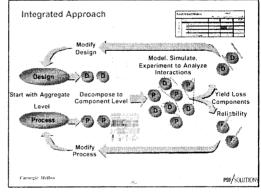

We will then propose requirements for the integrated approach to DFM, which will include the following features:

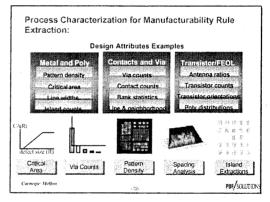

- Process characterization (including characterization vehicles) to identify the key yield loss reasons (systematic, parametric, random defects)

- Abstraction of manufacturability/reliability design rules including sub-wavelength litho (OPC, PSM) and realistic worst-case files

- Cost modeling and forecasting.

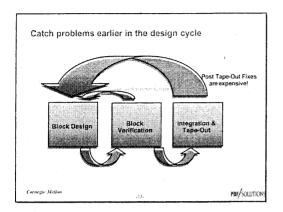

These DFM interface capabilities will re-define the design flow and will pose new requirements on the EDA. They will enable much more *predictive design* synthesis and much more *realistic* verification of the system before its manufacturing. The next part of the talk will propose such a design flow utilizing this DFM interface. We will focus on the following:

- Technology choice (forecasting of performance, yield, cost and ramp-up)

- Constraint propagation to high-level synthesis system

- High-level design decisions using technology abstraction (monolithic vs. 2.5D, choice of IP cores, etc.)

- Estimation of timing, signal integrity, power statistical distributions

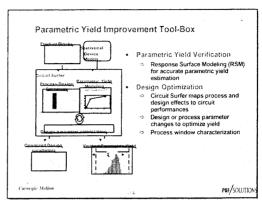

- Circuit design optimization for SOC including mixed-signal components (design centering, timing optimization)

- Layout optimization (including model-based OPC).

We will conclude the talk by discussing the technical and organizational challenges that must be overcome to successfully implement the new design-manufacturing interface.

## Design-Manufacturing Interface for .13 um and below Andrzej J. Strojwas Carnegie-Meillon University & PDF Solutions, Inc.

DFM Workshop. November 26, 2002

## Problems Design marginality □ IC design not robust enough, too sensitive to process fluctuations or environmental factors (supply voltage, temperature) Process-related yield losses: □ misprocessing (e.g., equipment-related) □ systematic effects □ random defects Testing issues: □ insufficient fault coverage in testing (test escapes) □ incomplete testing (does not fully represent IC operation in the field -e.g., simultaneous switching in the system not taken into account) □ test-related yield losses (incorrect testing) Reliability: □ transistors □ interconnect Cameric Mellon