6J - 03

# メニーコア上での離散ウェーブレット変換の SIMD命令を用いた階層的並列処理

Hierarchical Parallel Processing Using SIMD Instructions for Discrete Wavelet Transform on Manycore Processor

#### 西倉 佑騎↑

吉田 明正†

Yuki Nishikura

Akimasa Yoshida

### はじめに

ベクトル演算ユニットを搭載した Intel Xeon Phi[1] は OpenMP[2] によるループ並列処理と AVX-512[3] による SIMD 並列処理を併用して演算を高速にすることが期待 されている.

本稿では,画像圧縮等に用いられる2次元離散ウェー ブレット変換プログラムを対象とし,画像データの行 レベルの計算に OpenMP によるループ並列処理を適用 し, さらに各行のデータとドベシィ数列との内積演算に SIMD 並列処理を適用して,階層的な並列処理を実現す る. 本性能評価では, AVX-512 を搭載する Intel Xeon Phi のメニーコア (68 コア) を利用し,提案手法を実装 した C プログラムにより並列実行したところ高い実効 性能が達成され,提案手法の有効性が確認された.

#### 離散ウェーブレット変換の階層的並列処理

2次元離散ウェーブレット変換と SIMD 命令を用いた 階層的並列処理手法について述べる.

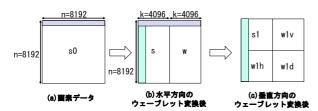

### 2.1 Ingrid-Daubechies ウェーブレット変換

Ingrid-Daubechies ウェーブレット変換 [4] は,多重解 像度解析を伴って画像圧縮に用いられるが、本稿では図  $1({\mathbf a})$  のようなレベル j(j=1) の計算のみ扱う . 画像デー タと $p_k$ (数列長=16)と $q_k$ (数列長=16)を使用し,式(1)と式(2)により求める. 今回のプログラムでは図1のよ うな $n \times n$  の画像 (n=8192) を入力とし, ウェーブレッ ト変換によって、図 1(b) のような  $n \times k(k=4096)$  のス ケーリング係数  $\mathbf{s}$  ,  $n \times k$  のウェーブレット展開係数  $\mathbf{w}$ を求める.同様にsとwに対して垂直方向にウェーブ レット変換を適用し,図1(c)のs1,w1h,w1v,w1dを求め る .  $\mathrm{s1}$  には  $\mathrm{s0}$  の低域成分 ,  $\mathrm{w1h}$  には水平方向の高域成 分, w1v には垂直方向の高域成分, w1d には水平・垂直 方向の高域成分が現れる.

$$s_k^{(j)} = \sum \overline{p_{n-2k}} s_n^{(j-1)} \tag{1}$$

$$s_k^{(j)} = \sum_n \overline{p_{n-2k}} s_n^{(j-1)}$$

$$w_k^{(j)} = \sum_n \overline{q_{n-2k}} s_n^{(j-1)}$$

(2)

図 1 2 次元ウェーブレット変換の概念.

#### 2.2ウェーブレット変換の OpenMP によるループ並 列処理

2次元離散ウェーブレット変換プログラムにおいて図 1(a) の行単位で Intel Xeon Phi のメニーコアを用いて, OpenMP によるループ並列処理を行う. 並列コードは 指示文#pragma omp parallel for schedule(dynamic,64) により実現する、ダイナミックスケジューリングのチャ ンクサイズ=64 としており,図 1(a) のような 8k 画像 では8192行を64行単位で各コアにダイナミックスケ ジューリングしている.

### 2.3 ウェーブレット変換の SIMD(AVX-512) による SIMD 並列処理

Intel Xeon Phi プロセッサでは AVX-512(512bit) のべ クトル演算ユニットが搭載されている.主な組み込み関 数は表 1 の通りである . AVX-512 は 512bit 幅の ZMM レジスタを使用して演算を行う.

本節では, OpenMP により各コアに割り当てられた 行データに対して水平方向のウェーブレット変換の過程 即ち図 1(a) の配列 s0 の各行を入力として , ドベシィの 数列  $p_k$  に対する内積演算を行い,図 1(b) 左側のスケー リング係数 s を求める過程を説明する.

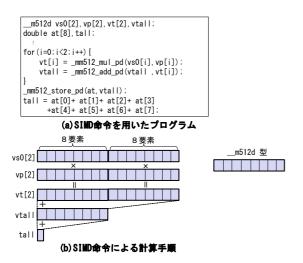

各行の画素データに対してドベシィの数列  $p_k$  (数列長 =16) との内積を求める際に, AVX-512 の SIMD 命令 を用いる、図 2(a) に AVX-512 コードを適用したものを 示す.このコードによってスケーリング係数の1つ(こ の例では変数 tall) を求めることができる. AVX-512 で は ZMM レジスタを用いるため, double 型データの場 合8要素を同時に演算可能である.16要素の内積(図 2(b) の vs0[0]・vp[0] と vs0[1]・vp[1]) の場合,8要素単 位の内積を vt[0] 及び vt[1] として求めて, それらの総和 を vtall に求め, vtall の8要素の和を tall に求める.

これらの方法により , OpenMP によるループ並列処 理と AVX-512 による SIMD 並列処理を階層的に行うこ とが可能になる.

表 1 AVX-512 の主な組み込み関数 (double 型) .

| ロード | _mm512_load_pd(a)                |

|-----|----------------------------------|

| ストア | $_{\rm mm512\_store\_pd(a)}$     |

| 加算  | _mm512_add_pd(mm512d a,mm512d b) |

| 乗算  | _mm512_mul_pd(mm512d a,mm512d b) |

## 3 Intel Xeon Phi 上での性能評価

本稿では,2次元離散ウェーブレット変換プログラム を用いて性能評価を行う. 関連研究として, GPU上で の離散ウェーブレット変換の階層的並列処理 [5] が行われているが、本研究のような SIMD 命令は用いられてい なかった.

<sup>†</sup>明治大学大学院先端数理科学研究科ネットワークデザイン専攻 Graduate School of Advanced Mathematical Sciences

図 2 2 次元ウェーブレット変換プログラムにおける SIMD 並列処理 .

#### 3.1 性能評価環境

本性能評価では,画像圧縮の対象として画像データ (8k:8192\*8192) を用いて,表 2 の Intel Xeon Phi サーバ上で実行した.画素値としては Y,Cb,Cr に変換された Y 成分のウェーブレット変換の処理時間を測定した.また OpenMP によるループ並列処理と AVX-512 による SIMD 並列処理の効果を確認するために最適化オプションは-O0 としている.

表 2 性能評価に用いる Intel Xeon Phi サーバの構成.

| マシン    | Intel Xeon Phi Knights Landing Server |

|--------|---------------------------------------|

| プロセッサ  | Intel Xeon Phi Processor 7250         |

| CPU コア | 68 コア (1.4GHz)                        |

| メモリ    | 48GB                                  |

| OS     | CentOS OS 7.4                         |

| 処理系    | icc18.0.1                             |

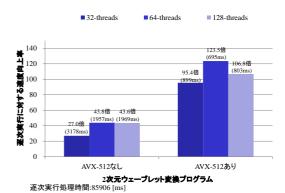

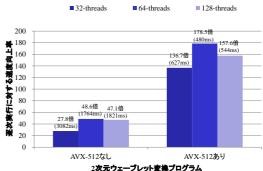

3.2 階層的並列処理 (AVX-512 あり) による性能評価本節では,OpenMP によるループ並列処理と AVX-512 による SIMD 並列処理を組み合わせた階層的並列処理による実行結果を示す.8k(8192\*8192) の画像データに対して double 型と float 型の演算を適用した結果を図3,図 4 に示す.

double 型演算において,AVX-512 なし・64 スレッド実行では,実行時間は 1957[ms] となり逐次実行比で 43.8 倍であった.それに対して,AVX-512 あり・64 スレッド実行では,実行時間は 695[ms] となり逐次実行比で 123.5 倍であった.

AVX-512 の場合, float 型データであれば 16 要素を同時に扱えるため, 精度が下がるが float 型演算でも性能評価を行った. AVX-512 なし 64 スレッド実行では, 実行時間は 1764[ms] となり逐次実行比で 48.6 倍であった. それに対して, AVX-512 あり 64 スレッド実行では, 実行時間は 480[ms] となり逐次実行比で 178.5 倍であった.

これらの結果から OpenMP による並列処理と AVX-512 による並列処理を組み合わせた階層的並列処理手法の有効性が確認できた.

# 4 おわりに

本稿では,2次元離散ウェーブレット変換プログラムに対して画像データの行レベルの計算にOpenMPによる

図 3 8k 画像における離散ウェーブレット変換の階層的 並列処理 (double 型).

逐次実行処理時間:85833 [ms]

図 4 8k 画像における離散ウェーブレット変換の階層的並列処理 (float 型).

ループ並列処理を適用し,さらに各行のデータとドベシィ数列との内積演算に SIMD 並列処理 (AVX-512) を実現する階層的並列処理手法を提案した. Intel Xeon Phi 上で性能評価を行ったところ,ループ並列処理と SIMD 並列処理を組み合わせた階層的並列処理では,8k サイズの画像データにおいて 64 スレッド実行で 123.5 倍 (double型) と 178.5 倍 (float型) の速度向上が得られた.これらの結果から SIMD 命令 (AVX-512) を用いた階層的並列処理の有効性が確認された.

今後の課題として,大規模アプリケーションに本手法 やタスク駆動型粗粒度並列処理[6]を応用することが挙 げられる.

# 参考文献

- [1] Intel Xeon Phi . https://ark.intel.com/content/www/jp/ja/ark/products/94035/intel-xeon-phi-processor-7250-16gb-1-40-ghz-68-core.html, 2019.

- [2] OpenMP . https://www.openmp.org/ , 2018 .

- [3] ジム・ジェファース, ジェームズ・レインダース, アビナッシュ・ソダーニ. インテル Xeon Phi プロセッサーハイパフォーマンス・プログラミング Knights Landing エディション. カットシステム, 2017.

- [4] 中野宏毅, 山本鎭男, 吉田靖夫. ウェーブレットによる信号処理と画像処理. 共立出版, 1999.

- [5] 吉川一輝,高平真由,吉田明正.マルチ GPU 上での画像圧縮における離散ウェーブレット変換の階層的並列処理,情報処理学会第16回情報科学技術フォーラムI-014,2018.

- [6] A.Yoshida, A.Kamiyama, H.Oka. A Task-Driven Parallel Code Generation Scheme for Coarse Grain Parallelization on Android Platform. Journal of Information Processing, Vol.25, pp.426-437, 2017.