5H-03

# ThruChip Interface を用いたバスによる衝突検知

程超然†, 宮田知輝‡, 門本淳一郎‡, 天野英晴‡, 黒田忠広‡ †慶應義塾大学理工学部 ‡慶應義塾大学理工学研究科

#### 1.序論

半導体技術の進歩により、単一チップ上への多数の計算コアの集積が可能となっている。これらの計算コア間の結合手段として Network-on-Chip (NoC)が注目されている。しかし、コア数の増加に伴って NoC の規模は年々増大しており、配線遅延や消費電力、それに伴う発熱が問題となっている。これらを解決する手段として、チップの 3-D 実装が挙げられている。チップを立体的に積層することでチップ間やコア間の配線長が短縮され、配線遅延が削減される。それにより、リピータバッファ数が減り、消費電力や発熱の問題が緩和される。3-D 実装を実現するために、多くの先行研究では TSV とマイクロバンプが用いられているが、これらの手法に伴う機械的な加工プロセスによる実装コストの増大が課題となっている.

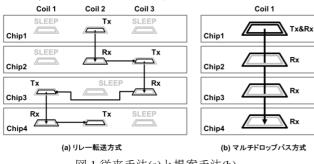

ThruChip Interface はコイル間の磁界結合を利用したチップ間通信技術である。コイルはチップ内の金属配線で形成されるため、機械的な加工プロセスは必要なく、低コストで3D 実装を実現することができる。従来、磁界結合で3枚以上のチップ間通信をおこなう際は、リレー伝送方式が用いられてきた[1].2枚のチップ間で通信をおこない、データを順次伝送することで、複数チップ間での通信を可能にしている(図1(a)).しかし、この方式ではチップ内のリレー転送毎にリンクのレイテンシがns単位で増大する。また、上下にあるチップのコイルからのクロストークノイズを防ぐため、3つのコイルが必要となり、ネットワーク機構は複雑になる。

図 1 従来手法(a)と提案手法(b)

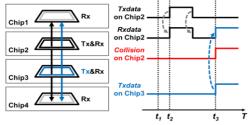

図2磁界変化を利用した衝突検知手法

A Wireless Communication Bus Using ThruChip Interface with Collision Detection Scheme

Chaoran Cheng†, Tomoki Miyata‡, Junichiro Kadomoto‡, Hideharu Amano‡ and Tadahiro Kuroda‡

- † Faculty of Science and Technology, Keio University

- ‡ Graduate School of Science and Technology, Keio University

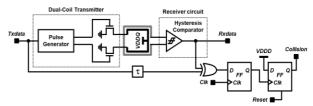

図3送受信回路

### 2.誘導結合を用いたデータ衝突検知機構

本論文で提案するマルチドロップバス方式は、積層さ れた複数のチップにあるコイル間で一度に通信をおこな う方式である(図 1 (b)). 各チップ内のコイルを中心が揃 うように配置する. 送信コイルが誘起する磁束はすべて の受信コイルを貫き,一度に全てのチップへデータを伝 送する. 通信に用いるコイルは 1 個/chip/ch となる. リ ンクのレイテンシは 0.1 ns 以下であり, 3 次元ネットワ ークのアーキテクチャはシンプルにできる. 本論文では, 磁界変化を利用した衝突検知手法を提案する. 受信コイ ルの内側に送信コイルを形成すると,送信コイルが誘起 する磁束は他のチップ上のコイルだけでなく,送信コイ ルと同じチップ内の受信コイルも貫く. したがって, あ る送信コイルが送信したデータは,他のチップ上の受信 コイルだけでなく,同じチップ上の受信コイルにも伝送 される. 同一チップ上で送信データと受信データとを比 較することで他のチップが送信したデータとの干渉の有 無を確認することができる(図2).

送受信機と衝突検知回路の回路図を図 3 に示す. 送信 機にはデュアルコイル送信機 を採用する[2]. デュアル コイル送信機 は NMOS トランジスタひとつのみでコイ ルを駆動するため Hブリッジ送信機と比較して消費電力 や回路面積の点で秀でている[3]. 受信機にはヒステリシ スコンパレータを用いる. これによって, クロックなし に非同期でデータを復元することができる. 磁界結合マ ルチドロップバスにおいて、データの送受信に関わらな いコイルは、開回路となっている必要がある. そうでな い場合には、コイルに渦電流が流れて磁界の変化が妨げ られ、受信信号の振幅が減少する. デュアルコイル送信 機では送信データの遷移時以外には送信コイルは開回路 となっておりループを形成していない. また, ヒステリ シスコンパレータを使った受信機では、受信コイル端が ヒステリシスコンパレータのトランジスタのゲート端子 に入力されており, 受信コイルは常に開回路となってい る. したがって、送信コイルや受信コイルに磁界の変化 を打ち消すような渦電流は流れず、磁界の変化を妨げな い. 衝突検知をおこなうため、XOR ゲートを利用して送 信回路に入力するデータと受信したデータを比較してい る. また, 送信データと受信データの位相のずれは遅延 回路によって補正する.

表 1 実測結果

| 通信距離 | 最大     | 消費電力 | 電力効率     |

|------|--------|------|----------|

| [µm] | データレート | [mW] | [pJ/bit] |

|      | [Gb/s] |      |          |

| 90   | 1.2    | 0.18 | 0.15     |

| 180  | 0.8    | 0.72 | 0.9      |

| 270  | 0.8    | 1.1  | 1.4      |

### 3. 実測結果

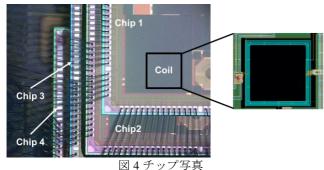

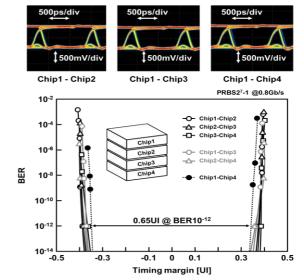

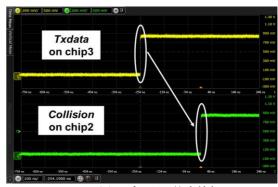

テストチップを 65 nm SOI CMOS プロセスで製造した (図 4). 製造したチップを 4 枚積層し、積層チップ間で の通信特性を評価した. 各チップの厚さは 80 um まで薄 く加工され、それぞれのチップは 10 um の接着剤で接着 されている. したがって、隣接するチップ間の通信距離 は 90 um となっている. まず,送受信機の特性を確認す るため,シリアル信号を送信機に直接入力して通信実験 をおこなった、通信実験には PRBS7 信号を用いた、上 下のチップへの通信(Chip1-Chip2, Chip2-Chip3, Chip3-Chip4)では、転送速度 1.2 Gbps で BER<10-12 を達成し、 送信回路の電源電圧は 0.45 V, 送信回路の消費電力は 0.18 mW, エネルギー効率は 0.15 pJ/bit となった. 2つ上, 2つ下のチップとの通信(Chip1-Chip3, Chip2-Chip4)では, 転送速度 0.8 Gbps 時に BER<10-12 を達成し、送信回路の 消費電力は 0.72 mW, エネルギー効率は 0.9 pJ/bit となっ た. 3つ上, 3つ下のチップとの通信(Chip1-Chip4)では転 送速度 0.8 Gbps 時に 0.8 Gbps 時に BER<10-12を達成し, 送信回路の消費電力は 1.1 mW, エネルギー効率は 1.4 pJ/bit となった. 4 枚チップ間バス通信のタイミングマー ジンと各受信データのアイダイアグラムを図5に示す. 電源電圧 1.2 V, 転送速度 0.8 Gbps の条件下で, BER=10-12におけるタイミングマージンは 0.65 UI であっ た. さらに、衝突検知回路の動作を実測で確認した. 出 力波形を図 6 に示す. Chip3 に入力する Txdata 遷移に対 応して、Chip2の衝突検知信号 Collision が立ち上がるこ とを確認できた. 信号経路の違いなどを補正した結果, Chip3 における Txdata の遷移から 5 ns 以内に Collision 信 号が立ち上がり、衝突検知がおこなえることが明らかに なった.

また、SerDes 回路やクロック生成回路も含む I/O 回路全 体を動作させ、Chip1-Chip2 間でのパケット転送実験を おこなった. 電源電圧 1.2 V,内部クロック周波数 2 GHz の条件下において, 入力データと出力データの比較をお こなった. Txwrite 立ち上げごとにランダムで入力データ を変更したところ、1000回以上連続での入出力データ整 合を確認し、ミスは一度も確認されなかった. 同一条件 での BER 実測結果から PER<10-10 と算出できた.

図5BERバスタブとアイパターン

図6データの衝突検知

#### 4.結論

本論文では、磁界結合を用いたマルチドロップバスと 磁界を利用した衝突検知方式を提案した. 65 nm SOI CMOS プロセスで製造した 4 枚のテストチップを積層し て実験をおこなった. 送信回路は電源電圧 0.45-1.2 V, 転送速度 0.8-1.2 GHz の範囲で BER<10-12 を達成し、エネ ルギー効率は隣接する上下チップとの通信の場合に 0.15 pJ/b, 2 つ上, 2 つ下のチップとの通信の場合に 0.9 pJ/b, 3つ上, 3つ下のチップとの通信の場合に 1.4 pJ/b であっ た. 衝突検知回路は正常に動作した. また, パケット転 送をおこない、1000回以上連続でのデータ整合を確認し た. 同一条件での BER から PER<10-9 と算出できた.

## 参考文献

[1] M. Saito, N. Miura, T. Kuroda, "A 2Gb/s 1.8pJ/b/chip inductive-coupling through-chip bus for 128-die NAND-flash memory stacking," IEEE International Solid-State Circuits

Conference, Dig. Tech. Papers, pp. 440–441, Feb. 2010. [2] N. Miura, et al., "A 0.55V 10fJ/bit inductive-coupling data link and 0.7V 135fJ/cycle clock link with dual-coil transmission scheme," IEEE Journal of Solid-State Circuits, vol. 46, no. 4, pp. 965-973, Apr. 2011.

[3] A. Razziz, et al., "A 352Gb/s inductive-coupling DRAM/SoC interface using overlapping coils with phase division multiplexing and ultra-thin fan-out wafer level package," IEEE Symposium on VLSI Circuits, Dig. Tech. Papers, pp. 29-30, June 2014.