IPSJ Transactions on System LSI Design Methodology Vol. 1 116-125 (Aug. 2008)

Regular Paper

# Accurate Estimation of the Worst-case Delay in Statistical Static Timing Analysis

Haruhiko Terada,<sup>†1</sup> Takayuki Fukuoka,<sup>†1</sup> Akira Tsuchiya<sup>†1</sup> and Hidetoshi Onodera<sup>†1</sup>

In this paper, we propose an approximation method for the statistical MAX operation such that it results in a normal distribution good for the worst-case delay analysis. The important operation in SSTA is SUM and MAX of distributions. In general, the delay variation is modeled as normal distribution. The result of SUM operation of two normal distributions is also normal distribution. On the other hand, the result of MAX operation is not normal distribution. Thus approximation to normal distribution is commonly used. We also explain that the proposed MAX operation at each gate also contributes to the accurate estimation in the worst-case delay analysis of the whole circuit. Experimental results show that the proposed method leads to a good approximation for a normal distribution, and the approximation improves the accuracy of the worst-case delay analysis. In a circuit example, the errors of worst-case delay computed by the previous method are about 20%, and the errors computed by the proposed method are under 5%.

# 1. Introduction

With the rapid progress of technology scaling, the number of components on a circuit explodes exponentially. It is becoming more and more difficult to predict a timing behavior of a circuit for accurate estimation of its timing yield. A transistor-level circuit simulation such as SPICE can be used for accurate estimation of a circuit behavior under a specific input transition. However, its cost is expensive and it is prohibitive to cover all possible combinations of input transitions. At this time, static timing analysis (STA) is an only viable method to predict a timing characteristic of a whole circuit where the latest arrival time (LAT) and the earliest arrival time (EAT) at each gate are propagated from the primary inputs to the primary outputs of the circuit.

In recent years, variability of scaled devices becomes a big concern<sup>1)</sup>. A conventional STA estimates the worst-case delay of a circuit based on the performance corner characteristic of each component. This treatment is effective on the assumption of global variability (die-to-die, wafer-to-wafer, lot-to-lot) where all components deviate toward the same direction. However, random variability within a die becomes dominant in a scaled technology, and hence the assumption of the global variability results in an overly pessimistic estimation. In order to consider random variability within a die, statistical static timing analysis (SSTA) has been attracting a wide attention<sup>2)-7</sup>.

Most of the SSTA techniques fall into one of two categories: block-based timing analysis or path-based timing analysis<sup>8</sup>). In this paper, we focus on the block-based approach which is a natural extension of conventional STA algorithm.

The SSTA deals with the LAT and EAT as random variables with certain probability distributions. Fundamental operations in SSTA are the statistical sum and maximum (SUM and MAX) of LAT/EAT distributions at each gate. In many cases, delay distributions are assumed to be Gaussian (normal) and LAT and EAT are also expressed in normal distributions. The Gaussian approximation greatly simplifies statistical operations on random variables. For example, under the assumption of normal distributions, SUM operation can be performed in an exact way, since the operation is linear and hence a resulting distribution becomes normal. In contrast, MAX is a non-linear operation and a resulting distribution does not become normal in a strict sense. Therefore we need to approximate it to a normal distribution.

A conventional method for the approximation is to match the first and second order moments of the two distributions such that the mean and the variance of the two distributions becomes the same. This is a natural approach from the standpoint of fitting the whole shape to a normal distribution. However, in SSTA especially for the timing analysis of application specific circuits (ASICs), important information to be analyzed is timing yield or, in another word, the worst-case delay that corresponds to a certain value of CDF such as 99% or 99.87%. From the standpoint of the worst-case delay analysis, the conventional method for statistical MAX operation that produces a normal distribution with

<sup>†1</sup> Department of Communications and Computer Engineering, Kyoto University

matched mean and variance does not lead to a good approximation, which will be shown later.

In this paper we propose an approximation method for the statistical MAX operation such that it results in a normal distribution good for the worst-case delay analysis. A similar concept has been proposed in Ref. 5) where the normal approximation is made that matches the CDF values at the best and the worst-cases of  $\mu \pm 3\sigma$  where  $\mu$  and  $\sigma$  represent the mean and the standard deviation of the approximated normal distribution. However, the method in Ref. 5) handles only the MAX of independent normal distributions without correlation. Also, the rationale of the approximation is not discussed. In this paper we explain that the proposed MAX operation at each gate also contributes to the accurate estimation in the worst-case delay analysis of the whole circuit. Experimental results show that the proposed method leads to a good approximation for a normal distribution resulted from MAX operation of normal distributions with and without correlation, and the approximation improves the accuracy of the worst-case delay analysis.

The remainder of this paper is organized as follows. In Section 2 we discuss a conventional approximate method of SUM and MAX operations for normal distributions. In Section 3, we propose a method for MAX operation that improves the accuracy for the worst-case analysis. In Section 4, we evaluate the accuracy of the proposed method in comparison with the conventional approach based on the Monte Carlo analysis. In Section 5, we discuss the reason why the proposed method for MAX operation at each gate leads to the improvement of the overall accuracy in the worst-case delay analysis of the whole circuit, followed by an experimental demonstration using a simple circuit model. Section 6 concludes the discussion.

# 2. Statistical Operations of Normal Random Variables

In this section, we describe fundamental operations in SSTA; SUM and MAX, and explain a conventional approximation method for MAX operation.

The purpose of SSTA is the statistical analysis of the latest (and the earliest) signal arrival time. In SSTA, similar to STA, statistical SUM and MAX operations are repeated from primary inputs to outputs and the LAT of the whole circuit is finally calculated. The EAT is also obtained in a similar way by using the minimum operation of the distribution (MIN operation) instead of the MAX operation. From now on, for simplicity, we focus our discussion on the LAT analysis with MAX operation. The same discussion can be made on the EAT analysis with the MIN operation. Also, we assume that all delay distributions are normal.

We first look at a SUM operation. Given two normal distributions  $x = N(\mu_x, \sigma_x^2)$  and  $y = N(\mu_y, \sigma_y^2)$ , the mean E[s] and the variance V[s] of the sum s = SUM[x, y] are represented as follows:

$$E[s] = \mu_x + \mu_y \tag{1}$$

$$V[s] = \sigma_x^2 + \sigma_y^2 + 2\rho_{xy}\sigma_x\sigma_y \tag{2}$$

where  $\rho_{xy}$  is a correlation coefficient between x and y. The SUM operation is linear and hence this treatment is exact.

Next, we explain a conventional method of MAX operation<sup>9)</sup>. Given two normal distributions x and y, the maximum h = MAX[x, y] is approximated to a normal distribution that has the mean E[h] and the variance V[h] as follows:

$$E[h] = \mu_x \Phi(\beta) + \mu_y \Phi(-\beta) + \alpha \phi(\beta) \tag{3}$$

$$V[h] = (\mu_x^2 + \sigma_x^2)\Phi(\beta) + (\mu_y^2 + \sigma_y^2)\Phi(-\beta) + (\mu_x + \mu_y)\alpha\phi(\beta) - E[h]^2$$

(4)

where  $\phi$  and  $\Phi$  are the probability density function (PDF) and the cumulative distribution function (CDF) of the normal distribution, respectively, defined as follows:

$$\phi(x) = \frac{1}{\sqrt{2\pi}} \exp\left[-\frac{x^2}{2}\right] \tag{5}$$

$$\Phi(x) = \int_{-\infty}^{x} \phi(y) \mathrm{d}y. \tag{6}$$

Parameters  $\alpha$  and  $\beta$  are defined as follows:

$$\alpha = \sqrt{\sigma_x^2 + \sigma_y^2 - 2\sigma_x \sigma_y \rho_{xy}} \tag{7}$$

$$\beta = \frac{\mu_x - \mu_y}{\alpha}.\tag{8}$$

Then, the correlation coefficient between h and an arbitrary normal distribution

$\bigodot$  2008 Information Processing Society of Japan

w is derived as follows where the correlation coefficients between x and w, y and w are  $\rho_{xw}$ ,  $\rho_{yw}$ , respectively:

$$\rho_{h,w} = \frac{\sigma_x \rho_{xw} \Phi(\beta) + \sigma_y \rho_{yw} \Phi(-\beta)}{\sigma_h}.$$

(9)

## 3. Worst-case Oriented Approximation of MAX Operation

Among the fundamental operations of SUM and MAX for normal distributions, the SUM can be calculated exactly. However, an error may be observed in the MAX operation when the resulting non-normal distribution is approximated to normal. In this section we discuss the approximation error in the resulting normal distribution by the MAX operation. Then we propose an approximate method that put emphasis on the accuracy of the worst-case value.

## 3.1 Approximation Error

In a conventional method, the mean and the variance of an approximated normal distribution resulted from the MAX operation are derived from the first moment and the second moment of the MAX-operated distribution<sup>9)</sup>. From another point of view, the conventional method approximates the shape of the whole distribution to normal. However, in ASIC design, the most important timing information is the worst-case value of the LAT that corresponds to a certain value of the CDF such as 99% or 99.87%. The 99.87% point of the CDF corresponds to  $\mu + 3\sigma$  of a normal distribution, and one of frequently used values for the worst-case delay. In this paper, we also use 99.87% point of the CDF for the worst-case delay, but we can use any other values for the definition.

The LAT of a circuit can be obtained by repetitive operations of SUM and MAX over all the gate in the circuit. The result of the MAX operation has a non-normal distribution due to non-linear nature of the operation. There is no guarantee that the 99.87% point of the CDF for a MAX-operated distribution corresponds to the  $\mu+3\sigma$  point of the normal distribution derived from the moments. In other words, the mean and the variance obtained by the conventional method are not adequate for the estimation of the worst-case value. Therefore, in the next subsection we propose a method for approximating a result of the MAX operation to a normal distribution such that the estimate error of the worst value of the distribution becomes minimal.

## 3.2 Proposed Method

We propose a method to obtain the mean and the variance of an approximated normal distribution of the MAX operation in order to minimize the error at the worst-case value. In the proposed method, the mean value is obtained from the first moment of the distribution because it is the primary parameter that characterizes the shape of the distribution. This is the same with the conventional method and the mean is expressed by Eq. (3). On the other hand, the variance is derived from the actual value of the worst-case delay such that the distance from the estimated mean and the actual worst-case delay is equal to a pre-defined value such as  $3\sigma$  in this case. The worst-case value can be accurately obtained in the case that the correlation coefficient is either 0, 1, or -1. If the correlation has a value between those discrete values, the worst-case value is approximated as a weighted average of them, as explained next.

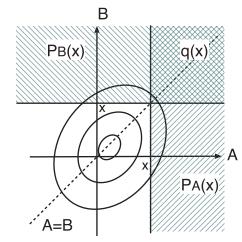

Given two normal random variables  $A = N(\mu_A, \sigma_A^2)$ ,  $B = N(\mu_B, \sigma_B^2)$  and maximum of them MAX[A, B], the probability that MAX[A, B] is larger than a certain value x is equal to the probability that either A or B is larger than x. That is, assuming q(x) be the probability that both A and B are larger than x, and  $P_A(x)$ ,  $P_B(x)$  be the probabilities that each of A and B is larger than x, the probability P(x) that MAX[A, B] is larger than x is expressed as follows:

$$P(x) = P_A(x) + P_B(x) - q(x).$$

(10)

If the correlation coefficient between A and B is 0 (non-correlation), q(x) can be expressed as follows:

$$q(x) = P_A(x)P_B(x). \tag{11}$$

If the correlation coefficient is 1,

$$q(x) = \min[P_A(x), P_B(x)] \tag{12}$$

where  $\min[P_A(x), P_B(x)]$  is the smaller value of  $P_A(x)$  and  $P_B(x)$ . If the correlation coefficient is -1, q(x) is as follows:

$$q(x) = 0. \tag{13}$$

If A and B has a positive correlation coefficient  $\rho(0 < \rho < 1)$ , we approximately derive q(x) from the q(x) values at  $\rho = 0$  and  $\rho = 1$  according to the value of  $\rho$  on a prorate basis, that is

if

$$P_A(x) \ge P_B(x)$$

$q(x) = \rho P_B(x) + (1 - \rho) P_A(x) P_B(x)$

(14)

if

$$P_A(x) < P_B(x)$$

$q(x) = \rho P_A(x) + (1 - \rho) P_A(x) P_B(x).$  (15)

$P_A(x), P_B(x)$  is calculated as

$$P_A(x) = 1 - \text{CDF}\left(\frac{x - \mu_A}{\sigma_A}\right) \tag{16}$$

$$P_B(x) = 1 - \text{CDF}\left(\frac{x - \mu_B}{\sigma_B}\right) \tag{17}$$

where CDF(x) represents a CDF of a normal distribution <sup>10</sup>.

In Eq. (10), the x that satisfies P(x) = 0.13% is the worst-case value of MAX[A, B]. There is no analytical solution for a reverse-function of P(x), and therefore we need a numerical search or an approximation method.

An example of the method for approximately obtaining x that satisfies P(x) = 0.13% is explained next. If  $\mu_A + 3\sigma_A > \mu_B + 3\sigma_B$  holds, it can be thought that the point that corresponds to the worst-case value of MAX[A, B] is in the neighborhood of  $\mu_A + 3\sigma_A$ . Therefore, in the region around the worst-case value, we approximate MAX[A, B] to a normal distribution with the mean of  $\mu_A$  and the standard deviation of  $\sigma_m$  which is slightly larger than  $\mu_A$ . This assumption leads to the following equation:

$$P(x) = 1 - \text{CDF}\left(\frac{x - \mu_A}{\sigma_m}\right) = \text{CDF}\left(-\frac{x - \mu_A}{\sigma_m}\right).$$

(18)

By calculating P(x) at  $\mu_A + 3\sigma_A$ , we have

$$P(\mu_A + 3\sigma_A) = \text{CDF}\left(\frac{-3\sigma_A}{\sigma_m}\right)$$

(19)

which results in

$$\sigma_m = -\frac{3\sigma_A}{\text{CDF}^{-1}(P(\mu_A + 3\sigma_A))}.$$

(20)

Therefore, x can be obtained by the following expression:

$$x = \mu_A + 3\sigma_A \frac{-3}{\text{CDF}^{-1}(P(\mu_A + 3\sigma_A)))}.$$

(21)

If  $\mu_A + 3\sigma_A < \mu_B + 3\sigma_B$ , x is obtained accordingly by replacing A in Eq. (21) with B.

When the cumulative probabilities in certain two points are given, a normal distribution is uniquely defined. We assume the mean obtained by Eq. (3) to be

$\mu_{\rm max},$  and calculate standard deviation  $\sigma_{\rm max}$  from the following equation:

$x = \mu_{\max} + 3\sigma_{\max}.$ (22) The correlation coefficient between an arbitrary normal distribution and

MAX[A, B] is derived in the same way as Eq. (9).

In the calculation of the MAX operation, the computations of CDF and  $\text{CDF}^{-1}$  requires more time than simple mathematical operations such as addition and multiplication. The calculation of CDF can be done by a polynomial approximation <sup>10</sup>). Also,  $\text{CDF}^{-1}$  can be obtained by an initial guess using a polynomial approximation followed by a numerical search with quick convergence <sup>11</sup>). In our experiment, the cost of  $\text{CDF}^{-1}$  calculation is about twice of CDF. The proposed method needs three CDF and one  $\text{CDF}^{-1}$  calculations whereas the conventional method requires one CDF calculation, which approximately indicates the cost impact of the MAX operations.

In this subsection, we have assumed that the  $3\sigma$  point of the CDF as the worstcase delay. As explained earlier, we can choose any other points for the worst-case delay. For example, if we use another  $\sigma$  point, the same algorithm can be applied except for changing the sigma values in Eqs. (19)–(22) to the corresponding value.

## 4. Accuracy Evaluation

In this section, the accuracy of estimated worst-case values of the MAX[A, B] obtained by the proposed method and the conventional method are examined in comparison with the worst-case value derived by Monte Carlo analysis.

Given the normal distributions A and B, the accuracy may depend on the differences in the means, variances, and correlation of the two distributions. We therefore evaluate the accuracy in the following three conditions.

## Purpose and condition of evaluation

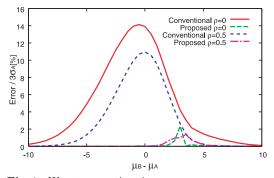

- (1) Error versus Difference of  $\mu_A$  and  $\mu_B$  $\mu_B - \mu_A$  is set to a variable, while  $\mu_A = 0$ ,  $\sigma_A = 3$ ,  $\sigma_B = 2$ , and  $\rho = 0$  or 0.5.

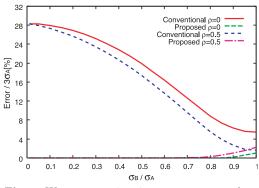

- (2) Error versus Ratio of  $\sigma_B$  to  $\sigma_A$  $\sigma_B$  is set to a variable, while  $\mu_A - \mu_B = 0$ ,  $\sigma_A = 3$ , and  $\rho = 0$  or 0.5.

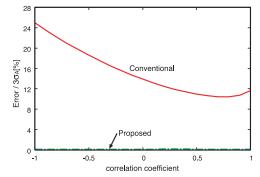

- (3) Error versus Correlation coefficient between A and B  $\rho$  is set to a variable, while  $\mu_A - \mu_B = 0$ ,  $\sigma_A = 3$ , and  $\sigma_B = 2$ .

$\bigodot$  2008 Information Processing Society of Japan

**Fig. 1** Worst-case estimation error versus  $\mu_B - \mu_A$ .

**Fig. 2** Worst-case estimation error versus  $\sigma_B/\sigma_A$ .

We assume the distribution of MAX[A, B] obtained by Monte Carlo method (1,000,000 trials) to be the true value and compared an error of our method and the conventional method under these three conditions. The amount of error is normalized by the variation of A ( $3\sigma_A$ ).

We show a result in **Figs. 1**, **2** and **3**. In Fig. 1, the error of the conventional method increases with a decrease in the difference of the means  $(|\mu_B - \mu_A|)$ . In Fig. 2, the error of the conventional method increases with a decrease in the ratio of  $\sigma_B$  to  $\sigma_A$ . In Fig. 3, the error of the conventional method becomes large when the correlation coefficient is negative. From those figures, the error of the conventional method reaches 25% in some cases, whereas the error of the

Fig. 3 Worst-case estimation error versus Correlation coefficient between A and B.

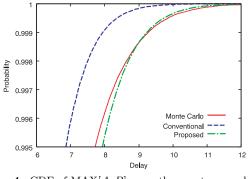

Fig. 4 CDF of MAX[A, B], near the worst-case value.

proposed method is less than 1% on average and 2% at the maximum. In all cases except for some exceptions, the proposed method provides far better accuracy over the conventional method. A possible source of errors in the proposed method includes the approximated derivation of the worst-case value by Eq. (21). Also, the limited number of trials in the Monte Carlo analysis may contribute to some amount of the errors in this experiment.

An example of the distribution shapes near the worst-case value is shown in **Fig. 4**. Three lines correspond to the CDF of MAX[A, B] obtained by the Monte Carlo, the proposed, and the conventional methods when  $\mu_A = \mu_B = 0$ ,  $\sigma_A = 3$ ,  $\sigma_B = 2$ , and  $\rho = 0$ . The proposed method provides a good approximation around

the worst corner.

# 5. Application to SSTA

In the previous section, experimental results show that the proposed method improves the approximation accuracy of MAX operation in the vicinity of the worst-case value compared with the conventional method. However, in SSTA, what is of prime importance is the accurate LAT estimation of the whole circuit, especially the worst-case value at primary outputs. In this section, we first explain that the accurate estimation of the worst-case delay at each gate also contributes to the accurate estimation of the worst-case delay for the whole circuit using a graphical representation of MAX and SUM operations. We then evaluate the accuracy of the worst-case delay of a circuit experimentally using a simple circuit model.

# 5.1 Graphical Representation of MAX and SUM Operations

In SSTA, we assume that each gate has delay distributions with correlation and we calculate the worst-case LAT value of the circuit that corresponds to a certain value of CDF by repetitive application of MAX and SUM operations. In the proposed method for MAX operation, resulting MAX-ed distribution is approximated to a normal distribution that has the same CDF value at the worstcase point. This provides a good approximation around the worst-case corner. However, the approximation is not necessarily good in the area far from the worstcase corner. In this subsection, we examine the characteristics of the MAX and SUM operations, and show that a good approximation emphasizing the accuracy around the worst-case corner is also important for accurate calculation of MAX and SUM operations in SSTA.

# 5.1.1 MAX Operation

We examine the accuracy of the worst-case value estimation obtained from a sequence of MAX operations.

**Figure 5** shows a concept of Eq. (10) using two-dimensional PDF of distributions A and B. The ellipsoids in Fig. 5 represent contours with equal probabilities. The cumulated probability of the upward-hatched area corresponds to  $P_A(x)$ , that of the downward-hatched area corresponds to  $P_B(x)$ , and the intersection of the two hatched areas corresponds to q(x). That is, the upper

**Fig. 5** Concept of upper probability P(x) of MAX[A, B].

probability of MAX[A, B] with respect to x, which is Eq. (10), is the cumulated probability of the whole hatched area in Fig. 5, and its value is independent from the distribution shape in the area without hatching.

The worst-case value of MAX[A, B] is the x that satisfies P(x) = 0.13%. From Fig. 5 it is clear that  $P_A(x) \leq P(x)$  and  $P_B(x) \leq P(x)$  hold. Therefore such xis located outside the worst-case values of the two distributions. In other words it is not necessary to know the distribution shape inside the worst-case values of A and B for the calculation of the worst-case value x. Instead, we should know accurate distribution outside the worst-case value for the MAX operation, which is achieved by the proposed method.

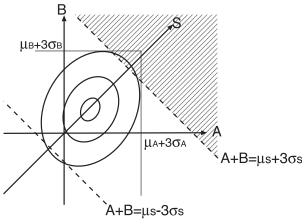

# 5.1.2 SUM Operation

In SSTA, the SUM operation is performed on the result of MAX operation and another normal distribution that represents gate or interconnect delay. **Figure 6** shows a concept of the sum of distributions A and B (S = A + B) using twodimensional PDF. When we assume the worst-case value of S to be  $\mu_S + 3\sigma_S$ , its upper probability is the cumulated probability of the shaded area shown in Fig. 6. To obtain the worst-case value of S accurately, the distributions A and B should be approximated to normal such that the distribution shape in the shaded

**Fig. 6** Concept of upper probability of SUM[A, B].

area is accurate.

In the shaded area, the highest probability appears at the closest point to the center of the two-dimensional Gaussian distribution. In the case that the correlation between A and B is positive, the point with the highest probability locates near the point of  $(\mu_A + 3\sigma_A, \mu_B + 3\sigma_A)$ . Because the proposed method provides accurate estimation of the distribution shape in the neighborhood of the worst corner, we can expect a good accuracy in the SUM operation. Should the correlation between A and B be negative, the accuracy might degrade because the point with the highest probability moves away from the point of  $(\mu_A + 3\sigma_A, \mu_B + 3\sigma_A)$  toward the center of the distribution. However, it is not clear whether negative correlation between adjacent gates may happen in a practical situation. We can conclude that the proposed method is also effective for the SUM operation.

## 5.2 Accuracy Evaluation of Circuit-level LAT Analysis

In this subsection we experimentally show that the proposed method improves the estimation accuracy of the worst-case LAT value of the whole circuit. Using a simple delay model and a circuit that includes small number of two-input gates, we calculate the distribution of LAT by the proposed and the conventional method, and evaluate the accuracy at the worst-case value.

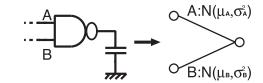

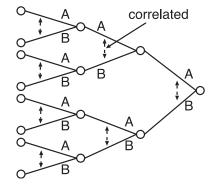

We can handle the problem to obtain the LAT of a combinational circuit as

Fig. 7 2-input gate delay model and MAX operation.

Fig. 8 Circuit model of 3-stage 2-input gates.

the longest path problem of a graph. For example in **Fig. 7**, if we assume delays from input to output of each gate are represented by A and B and assign these variables to each branch of the graph, the LAT of the circuit is MAX[A, B].

In this evaluation, we examine the graph of a circuit that consists of three stages of two input gates shown in **Fig. 8**. The leftmost eight nodes are inputs, and the rightmost node is the output. We assign the normal distributions  $A(\mu_A = 10, \sigma_A = 1)$  and  $B(\mu_B = 10, \sigma_A = 2)$  to each branch of the graph, and calculate the LAT of the whole circuit by MAX and SUM operations. We assume the correlation coefficient  $\rho$  between two delays of each gate. The same value is used for the coefficient  $\rho$  at each gate. The true distribution is obtained by the Monte Carlo method (1 M trials). We compare the LAT estimation error of the proposed method to that of the conventional method at the worst-case value (99.87% point). The amount of error is normalized by the variation of LAT (50% to 99.87%).

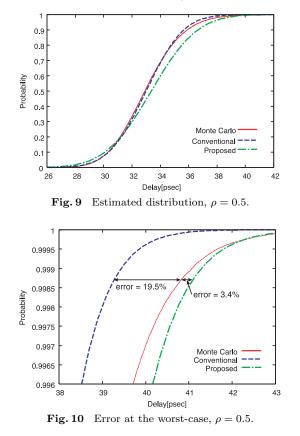

The estimated CDF at  $\rho = 0.5$  is shown in **Figs. 9** and **10**. The whole CDF is shown in Fig. 9 and a magnified view around the worst corner is displayed in Fig. 10. There is 19.5% error at the worst-case value of the LAT by the conventional method. In contrast, the error of the proposed method is 3.4%. We also evaluate under the condition of  $\rho = 0.2$  and 0.8, and the error is shown in **Table 1**. The error of the proposed method is 5-6 times less than that of the conventional method. Both methods have smaller error when the correlation is stronger. From these experimental results, we confirm that the proposed method estimates the worst-case LAT value of the circuit accurately.

| Table 1   Error at worst-case [%]. |              |          |

|------------------------------------|--------------|----------|

| ρ                                  | Conventional | Proposed |

| 0.2                                | 21.0         | 4.6      |

| 0.5                                | 19.5         | 3.4      |

| 0.8                                | 17.8         | 3.1      |

ro- 1

-

## 6. Conclusion

In this paper we propose an approximation method for the statistical MAX operation such that it results in a normal distribution good for the worst-case delay analysis.

We examine the accuracy of estimated worst-case values of the MAX[A, B] obtained by the proposed method and the conventional method in comparison with the worst-case value derived by Monte Carlo analysis. While the conventional method has up to 25% error at the worst-case value, the proposed method reduces the error to less than 2%.

We also explain that the proposed MAX operation at each gate also contributes to the accurate estimation in the worst-case delay analysis of the whole circuit.

Then, using a simple delay model and a circuit that includes small number of two-input gates, we calculate the distribution of LAT by the proposed and the conventional method, and evaluate the accuracy at the worst-case value. There is 20% error at the worst-case value of the LAT by the conventional method. In contrast, the error of the proposed method is less than 5%. From these experimental results, we confirm that the proposed method estimates the worst-case LAT value of the circuit accurately.

# References

- 1) Nassif, S.: Design for variability in DSM technologies, *Proc. IEEE Int. Symp. Quality Electronic Design*, pp.451–454 (2000).

- 2) Sapatnekar, S.: *Timing*, Kluwer Academic Publishers (2004).

- Chang, H. and Sapatnekar, S.: Statistical timing analysis under spatial correlations, *IEEE Trans. Computer-Aided Des. Integr. Circuits Syst.*, Vol.24, No.9, pp.1467–1482 (2005).

- 4) Dharchoudhury, A. and Kang, S.: Worst-case analysis and optimization of VLSI circuit performances, *Computer-Aided Design of Integr. Circuits and Syst.*, pp.481–

492 (1995).

- 5) Hashimoto, M and Onodera, H.: A performance optimization method by gate resizing based on statistical static timing analysis, *IEICE Trans. Fundamentals*, Vol.E83-A, No.12 (2000).

- 6) Visweswariah, C., Ravindran, K., Kalafala, K., Walker, S.G. and Narayan, S.: First-order incremental block-based statistical timing analysis, *Proc. DA Conf.*, pp.331–336 (2004).

- 7) Li, X., Le, J., Gopalakrishnan, P. and Pileggi, L.T.: Asymptotic probability extraction for non-normal performance distributions, *IEEE Trans. Computer-Aided Design of Integr. Circuits and Syst.*, Vol.26, No.1, pp.16–37 (2007).

- 8) Srivastava, A., Sylvester, D. and Blaauw, D.: *Statistical Analysis and Optimization* for VLSI: Timing and Power, Springer (2005).

- 9) Clark, C.E.: The greatest of a finite set of random variables, *Operations Research*, Vol.9, No.2, pp.145–152 (1961).

- 10) Cody, W.J.: Algorithm 715: SPECFUN-a portable FORTRAN package of special function routines and test drivers, ACM Trans. on Mathematical Software, Vol.19, pp.22–30 (1993).

- 11) Kennedy, W.J. and Gentle, J.E. Statistical Computing, marcel dekker (1980).

(Received December 25, 2007) (Revised March 17, 2008) (Accepted May 1, 2008) (Released August 27, 2008)

(Recommended by Associate Editor: Kei Hirose)

Haruhiko Terada received the B.E. degree in Electrical and Electronic Engineering from Kyoto University, Kyoto, Japan, in 2007. He is a student member of IPSJ.

**Takayuki Fukuoka** received the B.E. and M.E. degrees in Communications and Computer Enginnering from Kyoto University, Kyoto, Japan, in 2006 and 2008, respectively.

Akira Tsuchiya received the B.E., M.E. and Ph.D degrees in Communications and Computer Engineering from Kyoto University, Kyoto, Japan, in 2001, 2003, and 2005, respectively. Since 2005, he has been an Assistant Professor in the Department of Communications and Computer Engineering, Graduate School of Informatics, Kyoto University. His research interest includes mod-

eling and design of on-chip high-performance interconnects. He is a member of IPSJ, IEICE and IEEE.

IPSJ Transactions on System LSI Design Methodology Vol. 1 116-125 (Aug. 2008)

Hidetoshi Onodera received the B.E., and M.E., and Dr. Eng. degrees in Electronic Engineering from Kyoto University, Kyoto, Japan, in 1978, 1980, 1984, respectively. He joined the Department of Electronics, Kyoto University, in 1983, and currently a Professor in the Department of Communications and Computer Engineering, Graduate School of Informatics, Kyoto University. His research interests include design technologies for Digital, Ana-

log, and RF LSIs, with particular emphasis on high-speed and low-power design, design and analysis for manufacturability, and SoC architectures. Dr. Onodera served as the Program Chair and General Chair of ICCAD and ASP-DAC. He was the Chairman of the Technical Group on VLSI Design Technologies, IEICE, Japan, and the Chairman of the IEEE Kansai SSCS Chapter, and the Chairman of the SIG-SLDM (System LSI Design Methodology), IPSJ, Japan. He is currently the Chairman of the IEEE Kansai CASS Chapter. He served as the Editor-in-Chief of IEICE Transactions on Electronics, and currently he is serving as the Editor-in-Chief of IPSJ Transactions on System LSI Design methodology.