# FPGAを用いた6画面タイルドディスプレイシステム

岩田 拳太郎<sup>1,a)</sup> 成見 哲<sup>1</sup>

概要:本研究では FPGA による 6 画面を用いたタイルドディスプレイを開発した. 複数のディスプレイをタイル状に並べるタイルドディスプレイ技術は様々なものがあるが,業務用ディスプレイは高価であり,ソフトウェアによる手法ではディスプレイ間の同期が取れないという問題がある. 本システムでは FPGA ハードウェアを用いることで,システム構築の費用を抑えることに加え,PC を介することなくスマートフォンなどの HDMI 出力可能なデバイスから手軽に利用出来る. また,6 画面構成のため映画のような横長の映像に適しているシステムとなっている.

# 6-screen tiled display system using an FPGA

KENTARO IWATA<sup>1,a)</sup> TETSU NARUMI<sup>1</sup>

**Abstract:** In this research, we developed a tiled display system with six LCD panels. A tiled display, which is composed of multiple small displays in a grid, can be implemented by several methods. However, businessuse LCD panels for a tiled display is too expensive. Software oriented methods cannot synchronize multiple panels. Our system can solve these problems with FPGA hardware as well as supporting HDMI input from smartphones without PCs. A six-panel system is suitable for watching movies since its aspect ratio is wider than normal LCD panels.

# 1. はじめに

ディスプレイをタイル状に並べて安価に大画面を構成するタイルドディスプレイは、駅のデジタルサイネージ等で使われている。通常はベゼルが狭くタイル表示機能のある業務用ディスプレイを使用することが多いが、50インチ程度で1枚あたり数十万円と高価である。コンシューマー向けテレビであれば同サイズで10万円以下で手に入るが、タイル表示機能はない。

安価なディスプレイを使用してタイル表示する方法はいくつかある。例えば PC に NVIDIA 社の GPU (Graphics Processing Unit) である Quadro NVS 810 [1] を装着すると 8 画面表示が可能になるが,PC が不可欠であり GPU も高価格である。SAGE2 [2] のようなネットワークを介してソフトウェアで制御する方法もあるが,画面同期をハードウェア制御していないためディスプレイ間での表示タイミングのずれが発生する。いずれの方式でも,スマホやデジカメなどの HDMI 出力可能なデバイスからの表示を行うことは出来ない。

本研究では FPGA (Field Programmable Gate Array) を 用いて 6 画面のタイルドディスプレイシステムを開発した. FPGA デバイスは、HDMI で使われる TMDS 信号を直接 入出力できるため画像処理等で使われることが多い [3].

ハードウェアで実装することでソフトウェアでは実現できないディスプレイ間の同期を実現することに加え、HDMI 出力可能なデバイスなら直接接続できるという汎用性がある. また、液晶テレビや PC 用ディスプレイを VESA マウンタに取り付けるという簡易な方法で実現出来るため、安価であるだけでなく持ち運びが容易という利点がある. プロジェクタよりも高輝度であるためイベント等での使用に適している.

# 2. これまでに開発が行われてきたシステム

当研究室では FPGA を用いた様々なタイルドディスプレイシステムを開発してきた. サンドイッチマンのように人が担いで使える 4 画面のモバイルタイルドディスプレイ [4,5] や,ステレオ表示に対応した 4 画面のタイルドディスプレイ [6],縦型 3 画面のタイルドディスプレイ [7] などである. 特に最後のシステムでは,Digilent 社の Zybo ボード [8] に開発した HDMI コネクタ増設ボードを装着し,画面回転に対応するために外部メモリへの映像の読み書きに対応した.

これまでのシステムの共通する特徴としては、HDMI 出力可能なデバイスであれば使用可能であるという点、ベゼルコレクションが行える点が挙げられ、汎用性に優れたシステムとなっている。しかし、メモリへのアクセス速度によるボトルネックという問題がある。そのため、入出力可能な解像度は最大でも  $1280 \times 720$  の HD 画質となっている。3 画面タイルドディスプレイに関しては、難波らによっ

電気通信大学

The University of Electro Cominication

a) kentaro.linux@gmail.com

図 1 6 画面タイルドディスプレイ

図 2 FPGA ボードと増設コネクタ

てこのシステムは改良が行われ, 画質の向上, 任意実数倍拡大を行うことに至った [9]. しかし, 解像度の向上は行われなかった. また, いままでのシステムはすべて 4 画面以下になっており, 多画面への対応は行われていない.

# 3. 6画面タイルドディスプレイ

### 3.1 概要

本研究では既存のシステムの 6 画面への拡張を行った.これまでよりも高解像度である,  $1920 \times 1080$  の解像度で 60Hz の映像が入力可能である. なお, 実際に 6 画面に映る映像は  $1920 \times 720$  の横長の解像度になっている. これは 6 画面に出力したうえで, 一画素のアスペクト比を変更しないようにしたためである. 上下が見切れてしまうが, 映画などのそもそも横長の映像を映すのに適している. 図 1,2 は開発した 6 画面タイルドディスプレイシステムである.

本研究では Digilent 社の Nexys Video ボード [10] を用いた.この FPGA ボードは Zybo ボードよりも多くの I/O ピンを持っているため,HDMI コネクタを増設することにより 6 画面出力が可能である. 反面, 外部メモリが低速という弱点がある.

## **3.2 HDMI** コネクタの拡張

Nexys Video ボードには HDMI コネクタが入力用と出力用にそれぞれ一つづつしかついていない. そのため HDMI コネクタの拡張を行った. Nexys Video ボードには Pmod と呼ばれる汎用 IO コネクタが 4 つ存在する. そのコネクタの内, HDMI 出力ができる TMDS 信号が出力可能なものが 3 つあり, その Pmod に HDMI コネクタ拡張ボードを接続することで HDMI コネクタの増設を行った. また Nexys Video には FMC(FPGA Mezzanine Card) コネクタと呼ばれる拡張用コネクタが存在する. そのコネクタに HDMI 拡張ボードを接続することでさらに HDMI コネクタを増設した. 図 2 に拡張後の Nexys Video を示す. 最大 8 出力が可能になった.

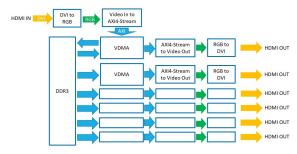

図 3 FPGA 内のブロック図

# 3.3 内部回路

内部回路の開発には Xillinx 社が提供する IP コアを用いた. 図 3 に FPGA 内のブロック図を示す. 主に用いた IP コアは 5 つあり、「DVI to RGB」と「Video In to AXI4-Stream」の 2 つを用いて HDMI 信号をシリアルからパラレルに変換し、そのデータを AXI\*1の形式に変換している. 「RGB to DVI」と「AXI4-Stream to Video Out」はその逆を行う IP コアである. 「VDMA」は映像データ専用のDMA 転送を行うメモリアクセス用 IP コアであり、この IP コアと出力に使う IP コアの 3 つを 6 組使用している. 6 つの「VDMA」は基本的にはメモリ読み出しのみを行うが、「VDMA」のうち 1 つだけはメモリ書き込みも行うようにしている.

6つの「VDMA」は1フレームの描画をする際に同時にメモリから画像データを読み込んでいる。これにより、ディスプレイ間の映像を同期することを可能にしている。

なお、これらの IP コアの使用には「MicroBlaze」と呼ばれる FPGA 上で実装された CPU を用いることが必要である. C 言語でプログラムを記述し、「VDMA」や出力映像の信号のタイミングを生成する「Video Timing Generator」の制御を行った.

#### 3.4 ピクセルクロックの割り増し

入力用の「VDMA」には上記の通り  $1920 \times 1080$  の映像をメモリにバッファするようにさせ、出力用の「VDMA」には 1 画面当たり  $640 \times 360$  の解像度で出力させた。 $640 \times 360$  の解像度でディスプレイに出力させると、通常ならピクセルクロックが約 18.75MHz になってしまい、映像が表示されなかった。しかし HDMI 信号にある映像を送っていないブランク部分を意図的に増やすことで出力が可能となった。具体的には  $640 \times 480$  の SD 画質の映像と同じピクセルクロック (25.0MHz) になるように、水平方向のタイミングは変更せずに垂直方向のブランク部分を 120 ライン分増やした。

## 4. まとめと今後の課題

本研究では、従来の問題点であったメモリへのアクセス速度の問題を VDMA を用いることで適切な転送を行わせることにより改善することに成功した。その結果、Full HD 解像度への対応を行うことに至った。また、FPGA ボードを変更することで 6 画面への対応を行った。

現状の問題点、課題は以下のものが挙げられる.

#### 4.1 一般的な解像度への対応

現在のシステムではディスプレイへの出力に一般的で

<sup>\*1</sup> IP コア間で用いられる通信プロトコル

ない解像度を用いている。そのため、一般的な解像度に拡大する処理が必要だと考えられる。例えば  ${

m HD}$  画質である 1280x720 の解像度であれば世の中のほとんどすべてのディスプレイで使用可能な解像度である。このような解像度まで拡大を行うことができれば、どのようなディスプレイにおいても使用可能なシステムになると考えられる。

### 4.2 さらなる高画質化

現状は Full HD 解像度への対応はできているが,多画面 化とともに大画面化が予想される本システムにおいては さらなる高画質化が望ましいと考えられる. そこで一般的 な解像度への拡張時には通常の拡張処理ではなく,ピクセ ル間を補完するような処理が望ましい. それにより大画面 へ映したとしても,よりきれいな映像になることが期待で きる

同時にシステムとしてより高解像度に対応することも課題の一つである. 現在のシステムの入力は Full HD 解像度であり、メモリへのアクセス速度をこれ以上向上させるのは現状難しい. しかし、データ量を減らすことで高解像度に対応が可能だと考えている. PC 用のディスプレイはその多くが 50Hz, 60Hz にしか対応していないが、一般的なテレビは 30Hz でも出力可能なものが多い. 30Hz で出力するようにすることで、データ量の半減が可能となる. また使用している映像データを RGB 形式から YCbCr\*2にすることでデータ量をさらに半減することが可能である. これらを実装することでデータ量を現状の 4 分の 1 までに減らし、解像度を 4K にすることが期待できる.

#### 参考文献

- [1] NVIDIA NVS 810, http://www.nvidia.co.jp/object/nvs-product-overview-jp.html

- [2] http://sage2.sagecommons.org/

- [3] Hisakawa Suzuki et al. "ExPixel FPGA: multiplex hidden imagery for HDMI video sources", ACM SIG-GRAPH 2015 Posters, Article No. 71 (2015)

- [4] 安枝 光・堀田将也・成見哲,「モバイルタイルドディスプレイの開発」,情報処理学会 第 76 回全国大会 (2014)

- [5] Tetsu Narumi, "An FPGA-Based Tiled Display System for a Wearable Display", The Fifth International Conference on Informatics and Applications (ICIA2016)

- [6] 堀田将也・嶋田貴行・大和田瑛美華・成見哲,「FPGA を 用いた 3D タイルドディスプレイシステム」,第 19 回バー チャルリアリティ学会大会 (2014)

- [7] 堀田将也、「FPGA を用いた 3D タイルドディスプレイシステムの開発」、電気通信大学情報・通信工学科 修士論文 (2014)

- [8] DIGILENT Zybo, https://japan.xilinx.com/ products/boards-and-kits/1-4azfte.html

- [9] 難波宗介,「FPGA を用いた縦置き 3 画面タイルドディ スプレイシステムの高解像度化」,電気通信大学 情報・通 信工学科 卒業研究 (2015)

- [10] DIGILENT Nexys Video,https://reference. digilentinc.com/reference/programmable-logic/ nexys-video/start

<sup>\*\*</sup> 人の目が色の輝度に敏感で色味に鈍感だという性質を利用して データ量を減らす形式