# 電流スターブ型発振器を用いた周波数変動の しきい値電圧変換手法

岸田 亮1 古田 潤1 小林 和淑1

概要:集積回路素子の微細化により,経年劣化などによる寿命予測が困難になっている.本論文では電流スターブ型発振器により,周波数変動をしきい値電圧変動に変換する手法を提案する.電流スターブ型発振器は電源線と,発振器の仮想電源線との間に被測定トランジスタが挿入された構造である.発振器をインバータではなく,NORにすることで,従来の問題であった発振器で起こる経年劣化を抑制し,被測定トランジスタのみの影響を観測することができる.測定した周波数をしきい値電圧に変換して外挿した結果,10年後の劣化率は指数関数と対数関数で見積もりに差があり,PMOSで6倍,NMOSで3倍異なった見積もりとなる.

## Threshold Voltage Conversion Method of Frequency Fluctuations Using Current Starved Ring Oscillators

Ryo Kishida<sup>1</sup> Jun Furuta<sup>1</sup> Kazutoshi Kobayashi<sup>1</sup>

Abstract: It has been difficult to predict lifetime of integrated circuits with the miniaturization of electronic devices. In this paper, Threshold voltage  $(V_{\rm th})$  conversion method of frequency fluctuations are proposed using current starved ring oscillators (ROs). Measured transistors are inserted between supply voltage line (VDD) and virtual VDD in the ROs. ROs are not composed by inverters but NORs to suppress aging degradation in ROs and only effects of measured transistors are observed. Measured frequencies are converted to  $V_{\rm th}$  and extrapolated. Estimations of  $V_{\rm th}$  degradations are different between exponential and logarithm functions. Exponential estimation is six and three times larger than logarithm in PMOS and NMOS respectively in ten years.

#### 1. 序論

我々が普段から使用している電化製品のほぼ全てに集積回路が使われている.電化製品の性能向上には集積回路の高性能化が必要不可欠である.集積回路を構成している素子は半導体のトランジスタであり,トランジスタの微細化により集積回路の性能が向上してきた.微細化による性能向上の例として,単位面積あたりに搭載できるトランジスタ数が増加する高集積化,1つ1つの素子の消費する電力が少なくなる低消費電力化,CPUの動作速度向上などがある[1].微細化は年を追うごとに進んでおり,初めて集積回路が発明された当時のトランジスタのゲート長が 10  $\mu$ m か

ら,2017年現在で 10 nm になっている [2] . ゲート長が 3 桁小さくなっていることは,面積にすると 6 桁小さくなっていることと同じであり,その分搭載されているトランジスタ数が増加していることを意味している.このように微細化が驚異的な速度で進んできたのは,微細化すればするほど性能向上とコスト削減という相乗効果的なメリットが得られるためである.しかし,微細化によるデメリットも存在する.その内の 1 つが Bias Temperature Instability (BTI) とよばれる経年劣化である [3] . BTI が微細化により顕在化している主な理由は,ゲート酸化膜の薄膜化と電圧スケーリングが微細化に追いついていないために,酸化膜にかかる実効電界が大きくなっているためである [4] . 開発された当初の酸化膜電界が  $5\times10^5$  V/cm だったのに対して,30 年後には  $6\times10^6$  V/cm と 1 桁増加している.BTI は

京都工芸繊維大学 電子システム工学専攻

Department of Electronics, Kyoto Institute of Technology

酸化膜電界が大きいほどより発生するため,近年では無視できない信頼性問題となっている.BTI は時間経過に伴ってしきい値電圧が増加する現象であり,このしきい値電圧増加によって回路動作中に誤動作がおこる.自動車など人命を預かる機器で故障が起こると致命的な問題となる.

BTI は経年劣化現象であるため,長期間の測定と劣化見積もりが必要である.単体トランジスタの測定では1つ1つの素子を評価できるが,多くの素子を測定するのが難しく,統計的評価に向いていない [5].数多く測定するには発振器とカウンタをチップに搭載して集積化するといいが,CMOS 構造上,NMOS と PMOS の影響を分離するのが難しい [6].さらに,発振器で測定されるのは発振周波数であるが,一般的にしきい値電圧の変動量で評価されることが多い.本稿では,電流スターブ型の発振器を用いることで,NMOS と PMOS の影響を分離し,測定した周波数をしきい値電圧へ変換する手法を提案する.発振器は NOR 型にすることで,被測定トランジスタ以外の BTI を抑制する.

本稿の構成を述べる.2 節で BTI について詳しく述べる.3 節では BTI の影響を調べるために試作した回路について述べ,4 節で BTI の測定結果を示す.5 節において,提案するしきい値電圧変換手法を述べ,その手法を用いて 10年後の劣化見積もりを行う.最後に 6 節で結論を述べる.

## 2. Bias Temperature Instability (BTI)

本節では BTI の発生原理を含んだ BTI の概要と,2種類ある NBTI (Negative BTI) と PBTI (Positive BTI) について述べる.

## 2.1 BTI の概要

BTI は経年劣化の主要因の1つである[3]. MOSFET に電圧や温度によるストレスを加えると,時間経過に伴ってしきい値電圧が劣化する.このしきい値電圧劣化が遅延時間の増加や,発振周波数減少などといった悪影響をもたらし,回路の誤動作につながる.BTIには劣化現象だけではなく回復現象が存在する.ストレスを取り除くと,劣化していたしきい値電圧が元にもどる.しかし,劣化したしきい値電圧が完全に回復するわけではなく,回復不可能な成分も存在する.回復不可能な成分はBTIの発生原理から説明できる.

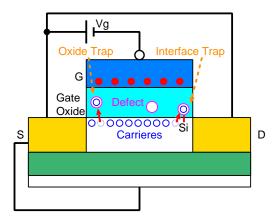

BTI の発生原理として Atomistic Trap-based BTI (ATB) モデルによるキャリアの捕獲および放出が考えられている [7], [8] . 図 1 に ATB モデルによるしきい値電圧変動を表した電界効果トランジスタ断面の模式図を示す.図 1 中の Oxide Trap のように,ゲート酸化膜の欠陥がチャネルのキャリアを捕獲することで,ゲートの実効電界が減少するため,結果としてしきい値電圧が劣化する.欠陥には捕獲および放出するまでの時定数が存在する.時定数は  $10^{-9}$  ~  $10^9$  s に幅広く分布するとされている.放出するまでの時

図 1 Atomistic Trap-based BTI (ATB) モデル・酸化膜中の欠陥 がチャネルのキャリアを捕獲することで, しきい値電圧が劣化 する.

定数が  $10^9$  s のように長い欠陥が一度キャリアを捕獲すると,半永久的にキャリアを捕獲し続けることになる.こういった欠陥では一度捕獲されたキャリアは放出されないため,ストレスを取り除いても回復しない.時定数の分布は対数一様分布であるとされている.

もう 1 つの BTI 発生原理として,酸化膜とボディ界面の結合が切断されることも考えられている [9] . 図 1 の Interface Trap のように結合が切れることによって,先と同様にしきい値電圧が増加する.これら 2 つがどちらも原因であるとしている先行研究もある [10] . この先行研究によると,酸化膜欠陥のキャリア捕獲による劣化は,しきい値電圧が時間 t に対して  $t^n$  で増加し,界面の結合切断による劣化は  $\log(t)$  で増加すると述べられている.ここで,n は時間指数と呼ばれる定数で約 0.14 である.どちらのモデル式も現在までよく使われており,実験値とよく合うことが知られている.本稿の劣化予測モデル式は,これに従って 2 つのモデル式それぞれを用いて行う.

#### 2.2 BTI の種類

BTI には NBTI (Negative BTI) と PBTI (Positive BTI) の 2 種類に分類される.NBTI は PMOS でゲート・ソース間電圧が負であるとき ( $V_{\rm gs} < 0$  V) に発生する経年劣化現象である.一方で PBTI (Positive BTI) も存在し,こちらは NMOS で  $V_{\rm gs} > 0$  V となるときに発生する.65 nm プロセスでは PBTI は顕在化していなかった.65 nm プロセスでは PBTI は顕在化していなかった.65 nm プロセスで用いられている SiON のゲート酸化膜では,NMOS では欠陥が発生しにくいためである.しかし,45 nm 以下のプロセスから high-k と呼ばれる高誘電率のゲート酸化膜を用いるようになったため,PBTI が顕在化してきた [11].high-k とは Hf (ハフニウム)を用いた SiON より約 5 倍高い誘電率をもつ材料である.high-k を用いる理由はゲート酸化膜の薄膜化に限界がきたためである.酸化膜厚を薄くするとゲートリーク電流が多く流れて消費電力が増大し,ゲート電界による制御が難しくなる.酸化膜の材料に

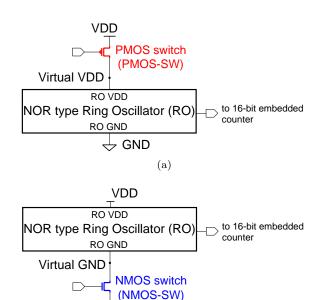

図 2 電流スターブ型リングオシレータ. (a) PMOS 型.電源線 (VDD) とリングオシレータの電源線 (RO VDD) との間に PMOS を挟んだ構造. (b) NMOS 型. グラウンド (GND) と リングオシレータのグラウンド (RO GND) との間に NMOS を挟んだ構造.

(b)

ightleftarrow GND

SiON より高い誘電率の high-k を用いることで,酸化膜を厚くしても SiON と同等の酸化膜容量を維持できる.しかし,high-k では NMOS でも欠陥が多くなり,PBTI が顕在化した.本稿で試作するプロセスは 65 nm であるが,埋め込み酸化膜を持つ SOI (silicon-on-insulator) であり,しきい値電圧調整のために,酸化膜に high-k が使われている.ゲートリーク抑制が目的ではないが,PBTI 顕在化の原因である high-k が使われているため,本稿で用いるプロセスでも PBTI が発生する.

## 3. 測定回路

本節で BTI による発振周波数変動をしきい値電圧変動 に変換するために試作した回路について述べる.

#### 3.1 電流スターブ型リングオシレータ

図 2 のような電流スターブ型のリングオシレータ(RO)を用いる。図 2(a) の PMOS 型では,電源線(VDD)と RO の電源線(RO VDD)との間に PMOS を挟んだ構造である.この挟んだ PMOS スイッチ(PMOS-SW)のしきい値電圧が劣化すると,RO VDD の電圧が下がり,RO の発振周波数が減少する.発振周波数を記録するカウンタが RO の出力とつながっており,カウンタの値を読み取ることで評価する.図 2(b) は NMOS 型の電流スターブ型 RO である.NMOS 型はグラウンド(GND)と RO のグラウンド(RO GND)との間に NMOS を挟んでいる.この NMOS のしきい値電圧が劣化すると,RO GND の電位が増加し,

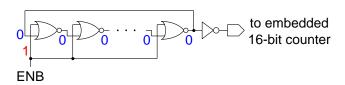

図 3 NOR 型 11 段リングオシレータ測定回路 . ENB が 1 のとき は全 NOR の出力は 0 となり , 発振が停止する . ENB が 0 の ときはインバータと同じ動作をするため , リングオシレータと して発振する .

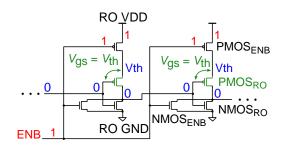

図 4 トランジスタレベルでの NOR 型リングオシレータ . 発振が停止するストレス状態でも ,  ${

m PMOS_{RO}}$  のゲート・ソース間電 圧  $(V_{

m gs})$  はしきい値電圧  $(V_{

m th})$  程度なので ,  ${

m NBTI}$  が抑制される .

PMOS 型と同様に発振周波数が減少する.

#### 3.2 NOR 型リングオシレータ

リングオシレータは NOR を鎖状につないだ 11 段リン グオシレータを用いる、図3にNOR型ROを示す.この NOR型ROが,図2の"NOR type Ring Oscillator"に搭 載されている. NOR の2つある入力端子のうち,1つは 発振制御用端子 (ENB) につなぐ. もう一方の端子は前段 NOR の出力端子につなぐ. インバータではなく NOR を用 いた理由は,発振停止時にROのBTIを抑制するためであ る.図4のトランジスタレベルのNORを用いてBTIを抑 制するための方法を説明する . ENB が 1 のとき , 全 NORの出力は0となり,発振が停止してストレス状態となる. このとき , RO として動作する  $PMOS_{RO}$  と  $NMOS_{RO}$  のし きい値電圧が劣化すると,発振周波数が減少する.しかし, 発振停止時の  $\mathrm{PMOS}_{\mathrm{RO}}$  のゲート・ソース間電圧  $(V_{\mathrm{gs}})$  は しきい値電圧  $(V_{

m th})$  程度であるため ,  ${

m NBTI}$  が抑制される .  $m NMOS_{RO}$  の  $V_{gs}$  は 0 V であるため , PBTI は発生しない . 入力を ENB につないでいる  $PMOS_{RO}$  と  $NMOS_{RO}$  のし きい値電圧が変動しても,発振周波数は変化しない.発振 周波数は PMOS<sub>RO</sub> と NMOS<sub>RO</sub> のゲート遅延時間によっ て決まるためである . ENB が 0 のときは , 全ての NOR は インバータと同じ動作をするため、リングオシレータとし て動作する.このとき,出力は0と1を交互に繰り返し て発振する.RO の電源またはグラウンドの電位が変動す ることによって,発振周波数が変動するため,リングオシ レータの発振周波数を時間経過毎に測定することで, BTI の影響を評価する.

図 5 試作チップ写真. リングオシレータが 70 個搭載されており, その平均値を評価する.

試作チップの写真を図 5 に示す .65 nm の SOI (siliconon-insulator) プロセスである .1 チップに同じ構造のリングオシレータを 70 個搭載しており , その平均値で評価する .

## 4. 測定結果

はじめに BTI の測定方法を述べた後に,3節で説明した回路を用いて発振周波数を測定した結果を示す.

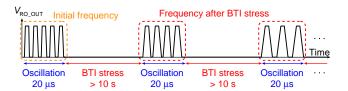

#### 4.1 測定方法

図 6 に測定の流れを示す.最初に,ENB を 0 にして初期発振周波数を測定する.発振させる時間はカウンタが桁あふれせず,かつ多くの発振回数を記録するために  $20~\mu s$ とする.初期発振周波数を測定した後は ENB を 1 にして発振を止める.このときに,電流スターブ型 RO として挟んだトランジスタに BTI ストレスが与えられる.ストレスを与える時間は 10~ 秒または 50~ 秒とし,BTI ストレスによる劣化を支配的にする.ストレスを与えた後,再び  $20~\mu s$  発振させる.ストレス後に測定される発振周波数は,BTI ストレスにより減少する.発振とストレスを交互に繰り返すことで,時間経過によりどれぐらい発振周波数が減少するかを確認する.

同じチップにおいて別条件で測定する場合,電源を30分以上切ってから行う.これは,BTIによる劣化が蓄積している可能性があり,回復させるために電源を切って.変更する条件以外は同条件で測定するためである.BTIを加速させるために,電源電圧は2.0 V,温度は120 °C で行う.

#### 4.2 BTI 測定結果

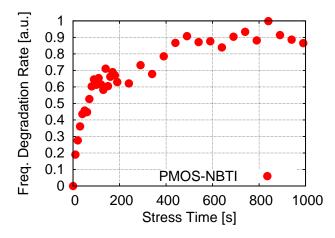

図 7 に NBTI が発生する PMOS 型での測定結果を示す. 横軸は与えたストレス時間,縦軸は周波数劣化率  $(D_{\rm rate})$ であり,以下の式 (1) で計算した値である.

$$D_{\text{rate}} = \frac{F_0 - F(t)}{F_0} \tag{1}$$

ここで, $F_0$  は初期発振周波数 ,F(t) は各時刻 t における周波数である.この値が大きいほど,より周波数が減少し,BTI により劣化していることを表す.図 7 の結果から,時間経過とともに  $D_{\mathrm{rate}}$  が増加しているため, $\mathrm{NBTI}$  が発生

図 6 BTI 測定の流れ.発振と BTI ストレスを交互に繰り返し, ストレス後にどれぐらい発振周波数が減少しているかを確認 する

図 7 PMOS 型リングオシレータにおける発振周波数の NBTI 測定 結果 . 電圧 , 温度ともに標準よりも増加させて劣化を加速させ て行っている . 時間経過とともに劣化していることがわかる .

していることがわかる.次節で,この測定結果をしきい値 電圧変動量に変換する.

## 5. しきい値電圧変動量変換

BTI によって減少する周波数が,どれぐらいのしきい値電圧変動となるかを調べるための変換を行う.初めに,回路シミュレーションを用いてしきい値電圧を変化させたときの周波数変動を確認し,得られた結果から測定結果に外挿し,10年後のしきい値電圧変動量を見積もる.

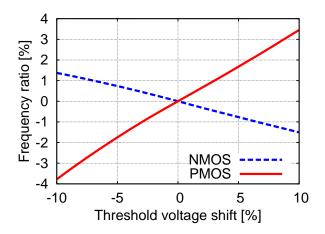

### 5.1 回路シミュレーションによるしきい値電圧変動

しきい値電圧  $(V_{

m th})$  を回路シミュレーションで変動させたときに,どれぐらいの周波数変動となるかを確認する.作成したレイアウトからトランジスタおよび配線の寄生抵抗と容量成分を抽出した回路をシミュレーションに用いる.スターブされたトランジスタ ( PMOS-SW, NMOS-SW ) のしきい値電圧を変動させて,発振周波数がどれぐらい変動するかをシミュレーションする.図 8 にしきい値電圧変動シミュレーションの結果を示す.横軸は変動させた  $V_{

m th}$  、縦軸は  $V_{

m th}$  を変動させていないときを基準とした発振周波数の比率である.PMOS,NMOS ともに  $V_{

m th}$  に対して線形に変動している.このシミュレーションより得られた周波数比率としきい値電圧の関係式は PMOS が式 (2) ,NMOS が式 (3) である.

図 8 しきい値電圧変動シミュレーション結果.しきい値電圧に対して線形に周波数が変動している.

$$F_{\rm P} = 0.384V_{\rm th} \tag{2}$$

$$F_{\rm N} = -0.134V_{\rm th}$$

(3)

ここで, $F_{\rm P}$ , $F_{\rm N}$  はそれぞれは PMOS と NMOS の周波数 比率であり,図 7 の縦軸である  $D_{\rm rate}$  に対応する.式(2),(3)の周波数比率としきい値電圧はどちらも変動割合で表している.

#### 5.2 測定結果の $V_{\rm th}$ への変換

前節で求められた式 (2) , (3) を用いて , 周波数変動をしきい値電圧変動量へ変換する . 変換した結果を最小二乗法を用いて近似し , 10 年後の劣化を見積もる . 近似には以下の 2 つの式をそれぞれ用いる .

$$f(t) = mt^n + l (4)$$

$$g(t) = a\log(t+1) + b \tag{5}$$

ここで,t は時間であり,f(t) は指数関数に比例する近似式,g(t) は対数関数に比例する近似式, $a,\ b,\ l,\ m,\ n$  はすべてフィッティングパラメータである.これらの式は先行研究に基づいたものである.

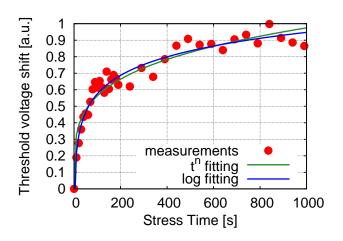

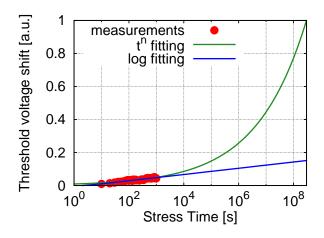

図 9 に先の図 7 の測定結果をしきい値電圧変動量に変換した結果を示す.横軸が時間で,縦軸がしきい値電圧変動量である.これを 10 年後まで外挿した結果を図 10 に示す.横軸を対数軸にしている.10 年後  $(3\times 10^8~{\rm s})$  の  $V_{\rm th}$  劣化率は指数関数と対数関数で異なることがわかる.指数関数の 10 年後  $V_{\rm th}$  劣化率は対数関数に比べて約 6 倍悲観的に見積もることがわかる.

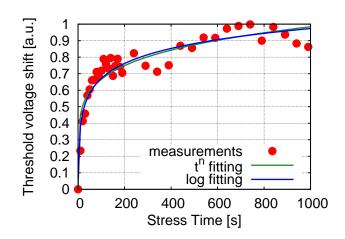

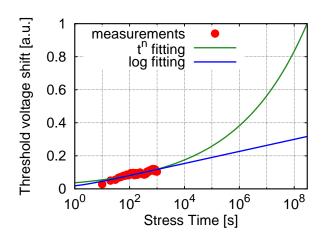

NMOS 型におけるしきい値電圧変動量への変換結果を図 11 に ,10 年後まで外挿した結果を図 12 に示す . NMOS 型 も PMOS 型と同様に変換ができ ,10 年後の指数関数による劣化率見積もりは対数関数に比べて 3 倍大きく見積もる .

図 9 PMOS 型のしきい値電圧変動量への変換結果 . 図 7 を  $V_{\rm th}$  に変換し , 2 つの式それぞれを用いて近似した .

図 10 PMOS 型のしきい値電圧変動量の 10 年後見積もり、10 年 後の劣化率は指数関数と対数関数で約 6 倍見積もりに差が 出る.

図 11 NMOS 型のしきい値電圧変動量への変換結果.

図 12 NMOS 型のしきい値電圧変動量の 10 年後見積もり.

## 6. 結論

電流スターブ型リングオシレータを用いた発振周波数のしきい値電圧変換手法を提案した、電流スターブ型により NMOS と PMOS の BTI への影響を分離することができ, NOR 型を用いることでスターブされた被測定トランジスタ以外の BTI を抑制した、測定結果から得られた BTI による周波数劣化をしきい値電圧劣化に変換し,指数関数と対数関数2つの近似式を用いて10年後の劣化見積もりを行った、近似式によって劣化見積もりに大きく差異が生じ,指数関数による見積もりは,対数関数よりも悲観的に見積もり,10年後の劣化率見積もりは対数関数の3~6倍大きくなる.

謝辞 本研究は JSPS 科研費 15H02677 の助成を受けて 実施したものである.本研究に用いたチップはルネサスエ レクトロニクスにより試作されたものであり,東京大学大 規模集積システム設計教育研究センターを通し,シノプシ ス株式会社,日本ケイデンス株式会社,メンター株式会社 の協力で行われたものである.

## 参考文献

- M. Bohr, "The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era", *IEDM*, (2011), pp. 1.1.1–1.1.6.

- [2] S. Yang, Y. Liu, M. Cai, J. Bao, P. Feng, X. Chen, L. Ge, J. Yuan, J. Choi, P. Liu, Y. Suh, H. Wang, J. Deng, Y. Gao, J. Yang, X.-Y. Wang, D. Yang, J. Zhu, P. Penzes, S. C. Song, C. Park, S. Kim, J. Kim, S. Kang, E. Terzioglu, K. Rim, and P. C. Chidambaram, "10nm High Performance Mobile SoC Design and Technology Co-Developed for Performance, Power, and Area Scaling", VLSI Tech., (2017), p. T6.2.

- [3] V. Huard, C. Parthasarathy, C. Guerin, T. Valentin, E. Pion, M. Mammasse, N. Planes, and L. Camus, "NBTI Degradation: From Transistor to SRAM Arrays", IRPS, (2008), pp. 289–300.

- [4] D. K. Schroder and J. A. Babcock, "Negative bias tem-

- perature instability: Road to cross in deep submicron silicon semiconductor manufacturing", *Journal of Applied Physics*, Vol. 94, No. 1, pp. 1–18, (2003).

- [5] J. Franco, B. Kaczer, M. Toledano-Luque, P. J. Roussel, G. Groeseneken, B. Schwarz, M. Bina, M. Waltl, P. J. Wagner, and T. Grasser, "Reduction of the BTI Time-Dependent Variability in Nanoscaled MOSFETs by Body Bias", IRPS, (2013), pp. 2D.3.1–2D.3.6.

- [6] W. H. Choi, S. Satapathy, J. Keane, and C. H. Kim, "A Test Circuit Based on a Ring Oscillator Array for Statistical Characterization of Plasma-Induced Damage", CICC, (2014), p.14-3.

- [7] H. Kukner, S. Khan, P. Weckx, P. Raghavan, S. Hamdioui, B. Kaczer, F. Catthoor, L. Van der Perre, R. Lauwereins, and G. Groeseneken, "Comparison of Reaction-Diffusion and Atomistic Trap-Based BTI Models for Logic Gates", *IEEE Trans. on Dev. and Mat. Rel.*, Vol. 14, No. 1, pp. 182–193, (2014).

- [8] B. Kaczer, S. Mahato, V. V. de Almeida Camargo, M. Toledano-Luque, P. J. Roussel, T. Grasser, F. Catthoor, P. Dobrovolny, P. Zuber, G. Wirth, and G. Groeseneken, "Atomistic Approach to Variability of Bias-Temperature Instability in Circuit Simulations", IRPS, (2011), pp. XT.3.1–XT.3.5.

- [9] S. Mahapatra, S. De, K. Joshi, S. Mukhopadhyay, R. K. Pandey, and K. V. R. M. Murali, "Understanding Process Impact of Hole Traps and NBTI in HKMG p-MOSFETs Using Measurements and Atomistic Simulations", *IEEE Electron Device Letters*, Vol. 34, No. 8, pp. 963–965, (2013).

- [10] C. Ma, H. J. Mattausch, K. Matsuzawa, S. Yamaguchi, T. Hoshida, M. Imade, R. Koh, T. Arakawa, and M. Miura-Mattausch, "Universal NBTI Compact Model for Circuit Aging Simulation under Any Stress Conditions", *IEEE Transactions on Device and Materials Reliability*, Vol. 14, No. 3, pp. 818–825, (2014).

- [11] S. Zafar, Y. Kim, V. Narayanan, C. Cabral, V. Paruchuri, B. Doris, J. Stathis, A. Callegari, and M. Chudzik, "A Comparative Study of NBTI and PBTI (Charge Trapping) in SiO2/HfO2 Stacks with FUSI, TiN, Re Gates", VLSI Tech. Symp., (2006), pp. 23–25.