# データの重要度を利用したキャッシュメモリの省電力化

千代延 昭宏 藤井 誠一郎 佐藤寿 倫 村

データの重要度を利用する省電力キャッシュメモリについて検討する.本稿で検討するキャッシュメモリはレイテンシと消費電力の異なる領域を持つ.クリティカルパス情報や時間的局所性で決定されるデータの重要度を利用して,省電力を指向したデータの配置を行う.このキャッシュメモリに対し,読み出す領域を考慮したアクセスを行うことで,処理性能を維持しつつ省電力化を目指す.シミュレーションによる評価の結果,データの重要度決定には時間的局所性を用いる方が良いこと,すべての領域が高速な  $\rm L1$  ,  $\rm L2$  キャッシュメモリと比較して,平均で約  $\rm 10\%$ の処理性能低下で約  $\rm 14\%$ の  $\rm ED^2P$  削減を達成できることが分かった.

# Low Power Cache Memories Prioritizing Data

AKIHIRO CHIYONOBU, † SEIICHIRO FUJII†† and TOSHINORI SATO†††

Considering the priorities of data could improve power efficiency of cache memories. The cache memories investigated in this paper have different ways regarding access latencies and power consumption. Two priorities based on criticality and locality are utilized to determine data location. Several cache access policies are evaluated to reduce power consumption with maintaining processor performance. The detailed simulations show that the priority based on locality is better in power efficient than that based on criticality and that 14% of the improvement in  $ED^2P$  is achieved with only 10% of performance loss.

# 1. はじめに

集積回路技術の進展により,プロセッサの処理性能は向上してきた.一方で,集積回路技術の進展はプロセッサ設計に新たな問題をもたらしている.それは消費電力である.動的消費電力だけでなく,これまで無視できていた静的消費電力も非常に大きくなっている.このため,我々はプロセッサの処理性能だけでなく,その消費する電力を考慮に入れた設計を行う必要に迫られている.

プロセッサの動的消費電力  $P_{active}$  は負荷の充放電によって消費する電力で,以下の式で表される.

$$P_{active} \propto f \times C_{load} \times V_{dd}^2 \tag{1}$$

ここで ,f はクロック周波数 , $C_{load}$  は負荷容量 , $V_{dd}$  は 電源電圧である . 一方 , 静的消費電力  $P_{leak}$  は半導体 の特性上流れてしまうリーク電流によって発生する 電力である . リーク電流にはゲートリーク , ジャンク

† 九州工業大学大学院情報工学研究科 Graduate School of Computer Science and System Engineering, Kyushu Institute of Technology

†† 日立アドバンスドデジタル

$\operatorname{Hitachi}$  Advanced Digital, Inc.

††† 九州大学システム LSI 研究センター System LSI Research Center, Kyushu University ションリーク, サブスレッショルドリークなどがあるが, 本稿では対象をサブスレッショルドリークに限定する. リーク電流のうちサブスレッショルドリークによる静的消費電力は,以下の式で表される.

$$P_{leak} \propto 10^{-\frac{V_{th}}{S}} \times V_{dd} \tag{2}$$

ここで,S はサブスレッショルドファクタ, $V_{th}$  はしきい値電圧を示す.プロセッサの動的消費電力の削減を図るならば,式 (1) の電源電圧を低下させることが効果的である.しかし,電源電圧の低下は次式 (3) に示すゲート遅延の増加を招く.

$$t_{pd} \propto \frac{V_{dd}}{(V_{dd} - V_{th})^{\alpha}} \tag{3}$$

式 (3) において  $\alpha$  はキャリア移動度の飽和を表すパラメータである.ゲート遅延の増加はプロセッサの動作周波数低下につながり,処理性能が低下する.ゲート遅延の増大を抑えるには,しきい値電圧を同時に低くすることが考えられる.しかし式 (2) から容易に分かるように,しきい値電圧の低下は静的消費電力を飛躍的に増加させる.また,静的消費電力は回路の待機時にも発生する.したがって,動的消費電力だけでなく静的消費電力も削減する必要がある.

この問題に対して本研究では,プロセッサの消費電

力の大部分を占めるキャッシュメモリに着目している. 動的消費電力については,従来どおり電源電圧の削減 によって省電力化を図る.一方静的消費電力について は,リーク電流の削減によって省電力化を図る.リーク 電流削減の方法の1つは,リーク電流の小さなトラン ジスタでキャッシュを構成することである.しかしこの 手法ではアクセスレイテンシが増大してしまう. そこ で以下の手法が考えられる.低レイテンシなウェイの 領域と高レイテンシなウェイの領域を用意する.低レ イテンシなウェイの領域は,高い電源電圧が供給され, しきい値電圧の低いトランジスタで構成される.この ためアクセス時の電力とリーク電流は大きい.一方, 高レイテンシなウェイの領域は、低い電源電圧が供給 され,しきい値電圧の高いトランジスタで構成される. このためアクセス時の電力とリーク電流が抑えられる. これらの領域のうち、低レイテンシな領域には重要度 の高いデータを配置する.一方,重要度の低いデータ は高レイテンシな領域に配置する.このようにデータ 配置の最適化を行うことで処理性能を低下させずに動 的消費電力と静的消費電力を削減可能になる16).

プロセッサのキャッシュメモリ以外の各ユニットの動的,静的消費電力を削減することも重要である.しかしすでに様々な検討が行われていることを考慮して,本稿ではキャッシュメモリのみを省電力化の対象とする.

本稿の構成は以下のとおりである.次章でデータの 重要度を定義し,3章でデータの重要度を利用する省 電力キャッシュメモリについて説明する.4章でキャッ シュメモリ内のデータの移動について述べた後,5章 でキャッシュアクセスの方法について検討する.6章 で省電力キャッシュメモリを評価する.7章で関連研 究を紹介し,8章でまとめる.

# 2. データの重要度

本稿で検討する省電力キャッシュアーキテクチャでは,データの重要度に応じてデータの配置場所を決める.よって,キャッシュメモリ内のデータの重要度を決める必要がある.データの重要度を決める方法として,時間的局所性に基づく方法とクリティカルパス情報に基づく方法とを検討する.

# 2.1 時間的局所性に基づく方法

時間的局所性に基づく方法では,プログラムの時間的局所性に着目する.プログラムには,最近アクセスしたデータに近い将来再びアクセスする可能性が高いという時間的局所性が存在する.最近アクセスされたデータほど再びアクセスされる可能性が高く,過去にアクセスされたデータになるほど再びアクセスされる

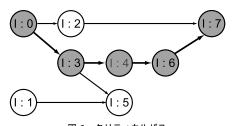

図 1 クリティカルパス Fig. 1 Critical path.

可能性が低くなる.この特性に着目して,最近アクセスされたデータの重要度を過去にアクセスされたデータよりも高いとする.つまり,MRU(Most Recently Used)で重要度を定める.

# 2.2 クリティカルパス情報に基づく方法

クリティカルパス情報を用いてデータの重要度を決定する場合には,クリティカルパス上のメモリアクセス命令によってアクセスされたデータの重要度をそうでない命令によってアクセスされたデータよりも高いとする.

クリティカルパスとは命令間の依存関係を結んだ鎖のうち最長のものを結んだ実行パスであり,プログラムの実行時間を決定する命令列である $^{15)}$ .図 1 に命令列中に現れるクリティカルパスを表すデータフローグラフの例を示す.図 1 において矢印は命令間の依存関係を示す.つまり,依存している命令は矢印の始点にある依存先の命令実行が終了しない限り実行できない.すべての命令のレイテンシが  $^1$  サイクルであるとすると,最も長いパスである命令  $^1:0 \to 1:3 \to 1:4 \to 1:6 \to 1:7$  を結んだパスがクリティカルパスとなる.実行中のプログラムのクリティカルパス情報を獲得する方法としてクリティカルパス予測器 $^{5),13),17}$  とパス情報テーブル (PIT: Path Information Table ) $^{15)}$  が提案されている.

本稿ではクリティカルパスを用いてデータの重要度を決める場合,クリティカルパス上に存在するメモリアクセス命令によって起こるキャッシュメモリへのアクセスをクリティカルアクセス,クリティカルパス上に存在しないメモリアクセス命令によって起こるキャッシュメモリへのアクセスをノンクリティカルアクセスと呼ぶ.また,それぞれのアクセスで供給されたデータをクリティカルデータ,ノンクリティカルデータと呼ぶ.

# 3. 省電力キャッシュアーキテクチャ

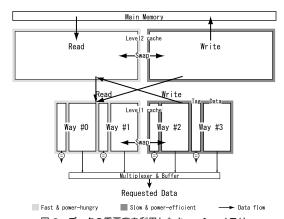

図2に本稿で検討している省電力キャッシュアーキテクチャを示す.ライトバック方式のキャッシュメモ

図 2 データの重要度を利用したキャッシュメモリ Fig. 2 The cache memory prioritizing data.

リを想定している。本キャッシュメモリでは、キャッシュメモリの持つウェイを低レイテンシと高レイテンシなウェイはしきい値電圧の低いトランジスタで構成され、高い電源電圧を供給される。このため、アクセスに必要な電力と回路のリーク電流は大きいが、データ供給は高速に行われる。一方、高レイテンシなウェイはしきい値電圧の高いトランジスタで構成され、低い電源電圧を供給される。このため、アクセスに必要な電力と回路のリーク電流は小さくなる。しかし、データ供給は低速に行われる。以後本稿では、低レイテンシなウェイの集合を高速な領域、高レイテンシなウェイの集合を低速な領域と呼ぶ。

このキャッシュメモリでは,セット内のデータの重要度をラインごとに識別できなければならない.これはデータの読み出しがラインごとに行われるためである.時間的局所性を利用してデータの重要度を決める場合,LRU (Least Recently Used)情報を用いて重要度を識別する.このとき,LRU 情報は高速・低速な領域ごとに管理されるとする.クリティカルパス情報を利用してデータの重要度を決める場合,クリティカルデータであるかノンクリティカルデータであるかを識別するための1ビットのフラグがラインごとに必要である.

図 2 は,プロセッサと主記憶の間にレベル 1 (L1) とレベル 2 (L2) の二階層のキャッシュメモリを配置 し,かつ,それぞれを高速・低速な領域に分割している場合を表している.各矢印はキャッシュメモリ内でのデータ移動の方向を示す.

プロセッサは L1 キャッシュメモリの高速・低速な 領域の両方に読み出し・書き込みの処理を行える. -方 L1 キャッシュメモリは, 読み出しは L2 キャッシュ メモリのどちらの領域からでも可能であるが,書き込みは L1 キャッシュメモリの低速な領域から L2 キャッシュメモリの高速な領域へしか行えない.データを素早くプロセッサに供給するため,L2 キャッシュメモリから読み出されるデータは必ず L1 キャッシュメモリの高速な領域へ置かれる.同様に主記憶から読み出されるデータは L2 キャッシュメモリの高速な領域へ置かれる.主記憶への書き込みは L2 キャッシュメモリの低速な領域からのみ可能である.L2 キャッシュメモリの低速な領域からのみ可能である.L2 キャッシュメモリの間速な領域からのみ可能である.L2 キャッシュメモリの間速な領域へきの点を考慮して L1 キャッシュメモリのの速な領域へ書き戻され,次に L2 キャッシュメモリのの速な領域へ追い出されるとする.

以上の点を考慮して,検討するキャッシュメモリは 図 2 に示したデータ移動を行うとする.図 2 に示したデータの配置,移動方法が最適かどうかは不明であるが,本稿ではこの最適性についてではなく,図 2 に示した構成のキャッシュメモリ,データの配置方法を採用した際の効果について述べる.

以上のようなデータ移動が生じるため,L2キャッシュメモリの高速な領域へは最近参照されたデータが集まり,低速な領域へは長期間参照されていないデータが集まる。L1キャッシュメモリへのアクセス方法や追い出されるデータの決定方法が変化しても,自然に最近参照されたデータがL2キャッシュメモリの高速な領域へ集まる。このように,L2キャッシュメモリではもともと時間的局所性に基づくデータ配置が行われる構成になっていることを考慮して,時間的局所性でデータの重要度を決めるとする。一方,L1キャッシュメモリは最近使われたデータが自然に高速な何メニストリは最近使われたデータが自然に高速な何ようにアーキテクチャ上の優位が存在しないため,クリティカルパス情報と時間的局所性を利用して重要度を決定することが可能である.

本キャッシュアーキテクチャのように各レベルを高速・低速な領域に分割することを考える場合,L1 キャッシュメモリの低速な領域をL2 キャッシュメモリ,L2 キャッシュメモリの高速な領域をL3 キャッシュメモリといったように分割した領域を利用して新たな記憶階層を構築することも考えられる.本研究では上位階層に存在するデータは下位階層にも存在するキャッシュメモリを想定している.また,分割前と分割後のキャッシュメモリの総容量を変化させないとすると,分割した領域で階層化を行った場合キャッシュメモリ内でアクセス可能なデータ量が減少する.これはキャッシュ

ミスの増加につながり,処理性能への影響が考えられる.このため,本研究では分割後の領域で新たな記憶 階層を構築する構成はとらない.

# 4. キャッシュメモリ内のデータ移動

本章では重要度に基づいてキャッシュメモリ内のデータを移動する方法について説明する.

# 4.1 時間的局所性に基づいた重要度の場合

時間的局所性を用いてデータの重要度を決める場合のデータの移動方法について説明する.時間的局所性を用いてデータの重要度を決める場合,各セットごとにLRUを適用して移動させるデータを決める.低速な領域のデータがアクセスされた場合,高速な領域の最古にアクセスされたデータが低速な領域へ追い出される.低速な領域のデータは高速な領域へ移される.高速な領域にあるデータがアクセスされた場合は,高速・低速な領域間でデータの移動は起こらない.

4.2 クリティカルパス情報に基づく重要度の場合 クリティカルパス情報に基づいたキャッシュメモリ 内のデータ移動について説明する.初めにクリティカルアクセスの場合について説明し,次にノンクリティカルアクセスの場合について説明する.

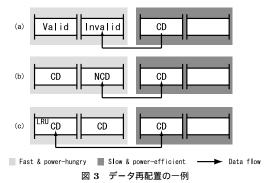

クリティカルアクセスの場合は高速な領域からデータが供給されることが理想である.したがって,供給されたデータがもともと高速な領域にあった場合はデータの移動は必要ない.しかしクリティカルアクセスされたデータが低速な領域にあった場合は,次回以降のアクセスは高速な領域からデータが供給された方がパフォーマンスに悪影響を与えない.よって,データを移動させる.まず,当該アクセスは低速な領域からが一タを供給する.データ供給後,今後は高速な領域からデータを供給できるようにデータを移動させる.高速な領域の置き換え対象となるデータの決定方法を図3を用いて説明する.図中のCDはクリティカルデータをNCDはノンクリティカルデータをNCDはノンクリティカルデータを表す.

- (1) 同一セットに有効なデータが存在しなければ, 高速な領域の空きセットへデータを移動する (図3(a)).

- (2) 同一セットにノンクリティカルデータが存在した場合は、そのデータと置き換える(図3(b)).

- (3) 同一セットにクリティカルデータしかなかった 場合,置き換え対象のデータは LRU で決定される(図3(c)).

ノンクリティカルアクセスの場合は,アクセス時間に余裕がある.アクセスの際の動的消費電力を削減するためには,低速な領域からデータが供給されること

Fig. 3 An example of data allocation.

が望ましい、したがって、供給されたデータがもともと 低速な領域にあった場合はデータの移動を行う必要が ない、しかしノンクリティカルアクセスされたデータ が高速な領域にあり、低速な領域にクリティカルデー タが存在する場合は低速な領域へ移動させた方が良い 場合がある、低速な領域の置き換え対象のデータは以 下のように決定される、

- (1) 同一セットにクリティカルデータが1つしか存在しなかった場合,そのデータと置き換える。

- (2) 複数クリティカルデータが存在した場合,置き 換え対象のデータは MRU で決定される.

一方,同一セット内のデータがすべてノンクリティカルデータであった場合,置き換える必要はない.この場合,置き換えを抑制した方がデータの移動にかかるレイテンシや電力を削減できるからである.

# 4.3 キャッシュミスとデータの移動

L1 キャッシュメモリでミスが起こり, L2 キャッシュ メモリヘデータの書き戻しが必要な場合のデータの移 動について説明する.まず L2 キャッシュメモリへ当 該データが要求される.同時に,L1 キャッシュメモ リの低速な領域の該当するセットから最も重要度の低 いデータが L2 キャッシュメモリへ追い出される.L1 キャッシュメモリから追い出されたデータは L2 キャッ シュメモリの高速な領域へ書き込まれる.L2 キャッ シュメモリの高速な領域に当該データが存在する場 合は,書き込みのみが行われる.同様に低速な領域に データが存在する場合は,まず領域間でデータの移動 が行われる.その後,高速な領域に書き込みが行われ る .L2 キャッシュメモリから供給されるデータは ,L1キャッシュメモリの高速な領域に置かれる.このデー タの置き場所を空けるため, L1 キャッシュメモリの 高速な領域のデータを低速な領域へ移動させる.この ようにして L2 キャッシュメモリから供給されたデー タは, L1 キャッシュメモリの高速な領域からプロセッ

サへ供給される.

続いて、L2 キャッシュメモリでもミスが起こった場合を説明する.まず主記憶に当該データの要求がされる.同時に L1 キャッシュメモリの場合と同様に低速な領域からデータを主記憶へ追い出す.このデータは LRU で決まる.次に主記憶から供給されるデータの配置場所を空けるため,L2 キャッシュメモリの高速な領域の該当するセットから最も重要度の低いデータが低速な領域へ移動される.このようにして主記憶から供給されたデータは,L2 キャッシュメモリの高速な領域から L1 キャッシュメモリへ供給される.

# 4.4 データ移動方法の実装

本キャッシュメモリで必要なセット間でのデータ移動には、各セットどうしが1対1でつながっているのが望ましい.しかし、その実現のためには膨大な付加回路が必要となるうえ、付加回路の消費する電力も莫大なことが予想される.よって、低コストなデータの入れ替えを実現する必要がある.

この問題に対処するため, キャッシュメモリへの読 み出し・書き込み動作に着目する. 入れ替わるデータ は今回のアクセスで読み出されたデータと入れ替え 先のデータである.新たなハードウェアとして,プロ セッサ-L1 キャッシュメモリ間, L1 キャッシュメモ リ-L2 キャッシュメモリ間にそれぞれ 2 ラインを保持 できるバッファを付け加える.今回のアクセスで読み 出されたラインは、そのバッファに一時保管される、 同様に置き換え先のデータをバッファに読み出した後、 キャッシュメモリに書き込む要領で読み出したライン があったウェイとは異なるウェイにデータを書き込む. 以上でデータの入れ替えが完了する.この方式の場合, 新たに必要となるハードウェアは2ラインを保存でき るバッファだけである.このことからセット間を1対 1で結ぶよりも格段に小さなコストでデータの入れ替 えを実現可能になる.入れ替えが完了するまでは次の メモリアクセス命令はキャッシュメモリヘアクセスで きないとする.

この L1 キャッシュでの領域間データ移動がクリティカルとなり、パイプライン処理に大きな悪影響を及ぼすことはないと考えられる.このデータ移動がクリティカルとなるのは、ロード命令が連続し、しかもそれらがすべてデータ移動を必要とするときに限られる.参照の局所性を考慮すると、連続してデータ移動が必要な場合は稀であると思われる.

多くのウェイを持つキャッシュでメモリでは , LRU 制御を実装するコストを抑えるために疑似  $LRU^{11)}$  を用いることがある . 本稿で LRU 情報は , 高速な領域 ,

もしくは低速な領域から追い出されるデータを決定するために用いられる.高速な領域へ移動されるデータは,時間的局所性で無条件に,もしくはアクセス命令のクリティカリティといったLRUではない情報で決定される.疑似LRU情報は8ウェイのセットアソシアティブキャッシュの場合でも,正しいLRU情報と同等の情報を利用することができる<sup>11)</sup>.このため,各領域から追い出されるデータを決定する際に用いるLRU情報として疑似LRUを用いても問題ない.

# 5. キャッシュメモリへのアクセス方法

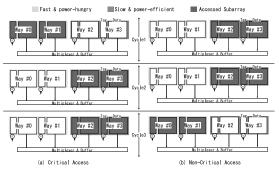

高速な領域のアクセスに要するレイテンシを 1 サイクル,低速な領域のアクセスに要するレイテンシを 2 サイクルと仮定してキャッシュメモリのアクセス手順を説明する.図 4,図 5,図 6 において,Way#0,Way#1 が高速な領域,Way#2,Way#3 が低速な領域であるとする.

# 5.1 クリティカルパス情報に基づくアクセス

クリティカルパス情報を利用してデータの重要度を 決定する場合, L1 キャッシュメモリの高速な領域には クリティカルデータが, 低速な領域にはノンクリティ

図 4 命令の重要度を利用したアクセス Fig. 4 The access using instruction criticality.

図 5 段階的アクセス Fig. 5 Phased access.

図 6 高速型段階的アクセス Fig. 6 Fast phased access.

カルデータが集まる.本キャッシュメモリのこの性質を利用して,L1 キャッシュメモリのアクセスする領域を決定する.

図 4 左側にメモリアクセス命令がクリティカルアクセスである場合を,右側にノンクリティカルアクセスである場合をそれぞれ示す.図中の Cycle# はアクセスが起こって何サイクル目かを表している.クリティカルアクセスである場合,まず L1 キャッシュメモリの高速な領域にアクセスする.高速な領域でヒットした場合,1 サイクルでデータを読み出せる.しかし高速な領域に該当するデータが存在しなかった場合,低速な領域に2 サイクルかけてアクセスする.低速な領域にもデータが存在しなかった場合,L2 キャッシュメモリにアクセスする.一方,ノンクリティカルアクセスの場合は,低速な領域,高速な領域,L2 キャッシュメモリの順にアクセスする.

本アクセス方法はアクセスする領域を区切っていることから,最初にアクセスした領域にデータが存在した場合,キャッシュアクセス時の動的消費電力を抑えることが可能である.しかし,データが最初にアクセスした領域とは逆の領域にあった場合,ヒットレイテンシが大きくなってしまう.またキャッシュミスの判明も遅れるので,ミスペナルティも大きくなる.

本アクセス方法はクリティカルパス情報に基づくアクセスを行う.しかし3章で述べたように,我々が提案する省電力キャッシュの L2キャッシュメモリは時間的局所性を用いてデータが配置されている.このため,L2キャッシュのアクセス時にクリティカルパス情報に基づく本アクセス方法を用いてもその効果が期待できない.よって,L1キャッシュで本アクセス方法を用いている場合でもL2キャッシュメモリへのアクセスは,5.2節もしくは5.3節で説明する方法を用いるとする.

#### 5.2 段階的アクセス

ライン読み出しをタグ比較の後に遅らせて,参照ラ インだけをサブアレイから読み出すことでキャッシュメ モリの省電力化を図る方式が提案されている4),7),14). このキャッシュメモリを段階的キャッシュメモリとい う. 段階的キャッシュメモリのタグは,1サイクルで 読み出しを行えるように高速な領域と同じしきい値の トランジスタと電源電圧で作られている.これまでの キャッシュメモリでは,データ読み出しがタグ読み出 しと同時に行われていた.これに対し,段階的キャッ シュメモリはタグ比較を行った後に必要なウェイだけ を読み出す、ミスした場合はラインは読み出されない、 この方法はタグ比較、データ読み出しを逐次的に行っ ている.このため,ヒットした場合に従来よりも余分 なアクセス時間が必要となる.しかし,ミスした場合 は無駄なライン読み出しが発生しないので消費電力を 節約できる.

本アクセス方法を採用したヒットする場合の様子を図5に示す.タグ読み出しに1サイクルかかると仮定している.図において,左側は高速な領域でヒットする場合、右側は低速な領域でヒットする場合をそれぞれ表す.本アクセス方式では,1サイクル目にタグのみを読み出し比較を行う.その後ヒットする場合は必要なデータのみ読み出す.ミスする場合も1サイクル目でミスが判明する.よって5.1節で説明したアクセス方法に比べ,ミスペナルティを少なくすることが可能となる.本アクセス方法は L1, L2 キャッシュメモリのどちらにも適用可能である.

本アクセス方法は、クリティカルパス情報に基づくアクセスとは異なりヒットする場合のレイテンシを実行前に見積もることができない、これは後続命令のスケジューリングに影響を与える、これに対しては、ウェイ予測<sup>6)</sup>を用いることで対応できる、ウェイ予測をデータキャッシュに適用した際の予測精度は平均で86%と非常に高い<sup>6)</sup>ので、アクセスが予測された領域のレイテンシに従って後続命令をスケジュールすることで、後続命令への影響をなくすことができる・ウェイ予測を行うために用いるウェイ予測器の消費する電力は非常に小さい<sup>9)</sup>、よって、このための電力的なオーバヘッドは、検討するキャッシュアーキテクチャによる省電力効果で打ち消すことが期待できる・

#### 5.3 高速型段階的アクセス

前述した段階的キャッシュメモリを用いたアクセス 方法を改良する.前節で述べた方法をそのまま採用す ると,キャッシュミスペナルティを削減できる反面, 高速な領域のレイテンシが増加してしまう.これはタ

グ比較,ライン読み出しを段階的に行うためである. そこで,高速な領域は従来のようにタグ比較とライン 読み出しを同時に行う.一方,低速な領域はタグ比較 のみ高速な領域と同時に行えるよう,段階的アクセス を導入する.低速な領域は,タグ領域が低しきい値電 圧で高速な領域と同時にタグ比較が可能だが,ライン 部分は高しきい値で読み出し時間がかかる.以上のよ うな実装をすることで,前節で説明した方式よりも高 速な領域のヒットレイテンシを削減できる. 本アクセ ス方式を図6に示す.高速な領域にデータが存在した 場合,1 サイクルでデータが供給される. キャッシュ ミスする場合も 1 サイクルでミスすることが判明す る.このことから,5.2 節で説明したアクセス方式のミ スペナルティを軽減可能という利点を保ちつつ、高速 にデータを供給可能になっていることが分かる.段階 的アクセスと同様に本アクセス方法は L1, L2 キャッ シュメモリのどちらにも適用可能である.また,後続 命令のスケジューリングにはウェイ予測情報を用いる.

# 6. 評 価

# 6.1 本章の評価に用いた環境

SimpleScalar Tool Set 3) に省電力キャッシュメモリを組み込んだ環境で評価を行う.評価に用いるプロセッサの構成を表 1 に示す.キャッシュメモリ内でのデータ移動には,各レベルの高速・低速な領域へのアクセス時間を足した8サイクル,40サイクルの入れ替えペナルティをそれぞれ要するとした.このため入れ替えが起こる場合,ヒット,もしくはミスレイテンシに各ペナルティが加算される.

命令セットは MIPS R10000 の ISA を拡張した

SimpleScalar/PISA である.使用するベンチマークプログラムは SPEC 2000 CINT の中の 7 本で,それぞれの入力は表 2 に示すとおりである.いずれのプログラムもはじめの 10 億命令をスキップし,続く 5 億命令をシミュレーションする.評価にはキャッシュメモリへのヒット率,プロセッサの処理性能,キャッシュメモリのエネルギー,エネルギー遅延二乗積(Energy-Delay Square Product:  $ED^2P$ ) を用いる.

$ED^2P$  はパワー削減による遅延の増加と省電力効果のトレードオフを定量的に評価するために用いられる指標である.電圧制御を用いて省電力化を試みる場合の評価に適している $^8$ ).  $ED^2P$  は,高速・低速な領域がそれぞれ何回ずつ使用されたかをカウントし,その回数とそれぞれのアクセスごとに消費するエネルギー,リーク電流による消費エネルギー,プログラム実行に要した時間から求めることとした.高速・低速な領域は $70\,\mathrm{nm}$ のテクノロジを想定し,アクセス時のエネルギーとリーク電流は $\mathrm{CACTI4.1^{12}}$  を利用して求める.高速・低速な領域のしきい値電圧には $\mathrm{CACTI}$ の定める値を用い,それぞれ $0.19\,\mathrm{V}$ , $0.29\,\mathrm{V}$  である.高速な領域の電源電圧は, $\mathrm{ITRS}$  のロードマップ $^{10}$ )か

表 2 ベンチマークプログラム Table 2 Benchmark programs.

| Benchmark            | Input Set      |  |

|----------------------|----------------|--|

| gzip                 | input.source   |  |

| vpr                  | net.in arch.in |  |

| gcc                  | 166.i          |  |

| parser               | ref.in         |  |

| vortex               | lendian1.raw   |  |

| bzip                 | input.source   |  |

| $\operatorname{mcf}$ | inp.in         |  |

表 1 プロセッサ構成 Table 1 Processor configuration.

|                  | <u>-</u>                                                                                 |  |  |

|------------------|------------------------------------------------------------------------------------------|--|--|

| Clock Frequency  | $6\mathrm{GHz}$                                                                          |  |  |

| Fetch Bandwidth  | 8 instructions                                                                           |  |  |

| Branch Predictor | 1 K-set 4-way set-associative BTB, 4 K-entry 12-history-length gshare predictor,         |  |  |

|                  | 64-entry return address stack, 6-cycle miss penalty, updated at commit stage             |  |  |

| Insn. Windows    | 128-entry instruction queue, 64-entry load/store queue                                   |  |  |

| Issue Width      | 8 instructions                                                                           |  |  |

| Commit Width     | 8 instructions                                                                           |  |  |

| Functional Units | 6 Int, 3 FP, 4 Ld, St                                                                    |  |  |

| Latency          | iALU 1/1, iMUL 8/1, iDIV 32/1, fADD 4/1, fCMP 4/1, fCVT 4/1, fMUL 4/1,                   |  |  |

| (total/issue)    | fDIV 32/1, fSQRT 32/1, Ld/St 2/1                                                         |  |  |

| Register Files   | 32 32-bit Int registers, 32 32-bit FP regsters                                           |  |  |

| Insn. Cache      | 32 KB, 4-way, 32 B blocks, 1-cycle hit latency, 18-cycle miss penalty                    |  |  |

| Data Cache       | 32 KB, 4-way, 32 B blocks, 4-port, write-back, non-blocking load,                        |  |  |

|                  | hit under miss, 3-cycle fast hit latency, 5-cycle slow hit latency, 8-cycle swap penalty |  |  |

| L2 Cache         | unified, 1 MB, 8-way, 64 B blocks, 18-cycle fast hit latency, 22-cycle slow hit latency, |  |  |

|                  | 40-cycle swap penalty                                                                    |  |  |

| Main memory      | 80-cycle latency                                                                         |  |  |

表 3 アクセスあたりのエネルギー (pJ) Table 3 Energy per access (pJ).

|    |      | Tag  | Data   |

|----|------|------|--------|

| L1 | Fast | 0.65 | 11.83  |

|    | Slow | 0.53 | 9.78   |

|    | Swap | 2.36 | 43.21  |

| L2 | Fast | 0.42 | 43.36  |

|    | Slow | 0.21 | 21.64  |

|    | Swap | 1.27 | 130.00 |

表 4 リーク電流 (mW) Table 4 Leakage current (mW).

|    |      | Tag  | Data   |

|----|------|------|--------|

| L1 | Fast | 0.36 | 6.60   |

|    | Slow | 0.24 | 4.44   |

| L2 | Fast | 0.99 | 101.11 |

|    | Slow | 0.76 | 77.77  |

ら 70 nm のハイパフォーマンス向けトランジスタで 用いる電源電圧を参照し、1.1 V とした.今後は電源 電圧のスケーリング幅が小さくなることを考慮して、低速な領域の電源電圧は1.0 V とした.CACTI から 求めた1回あたりのアクセスエネルギーを表3、リーク電流を表4にそれぞれ示す.表には1ウェイあたりの結果を示す.なお、データ入れ替え時に消費するエネルギーは各領域への読み出し・書き込み分のエネルギーの合計とした.データの重要度決定にクリティカルパス情報を用いる場合、PIT を用いる.時間的局所性を用いる場合はLRU 情報を用いる.

# 6.2 L1 キャッシュメモリへ適用した場合

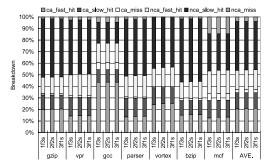

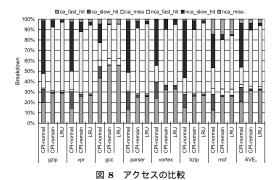

まず省電力キャッシュアーキテクチャを L1 キャッ シュメモリへ適用する場合のヒット率を図7に示す. 図は、クリティカルパス情報に基づいてアクセスする 領域の順番を決定する場合の結果である. 図中の縦 軸はキャッシュアクセスの内訳とヒット率を表す. 横 軸は各ベンチマークごとの結果とその平均を示して いる.ラベルのf,sの前の数字はそれぞれ高速・低 速なウェイの数を示している. たとえば 1f3s は高速 ウェイ数が 1,低速ウェイ数が 3 であることを表す. ca はクリティカルアクセス, nca はノンクリティカ ルアクセス, fast は高速ウェイヒット, slow は低速 ウェイヒット, miss はキャッシュミスという意味で ある. 望ましいキャッシュヒットである ca\_fast\_hit, nca\_slow\_hit は高速・低速なウェイ数に関係なくそれ ぞれ約 21%と約 42%である. 一方, データの移動が必 要になる ca\_slow\_hit, nca\_fast\_hit はそれぞれ約 14%と約17%であった.ca\_slow\_hit,nca\_fast\_hit が起こっていることから、同一セットにアクセスする 命令の重要度に変化があることが分かる. 高速・低速

図 7 クリティカルパス情報を用いたアクセスをした場合の内訳 Fig. 7 Access breakdown when using critical path information

なウェイ数が変わっても各ヒット率 , ミス率に大きな変化は見られない . ヒット率に変化が見られない点 , 低速なウェイが多い方がリーク電流に起因する電力の削減効果を考慮して , 今後は高速なウェイが 1 , 低速なウェイが 3 の L1 キャッシュについて評価を行っていくこととする .

図7に示した結果では,ca\_slow\_hit,nca\_fast\_hit がそれぞれ約 14%と約 17%あることから,データの 移動に要するペナルティの影響が懸念される、そこ で,スワップ頻度の低減のためにノンクリティカルア クセス時に高速な領域でヒットした場合,低速な領 域へデータの移動を行わないようにした.これは以 下の理由による、クリティカルアクセスされたデータ はただちにプロセッサへ供給されないと性能へ悪影 響を与える.このため,低速な領域にクリティカルア クセスがあった場合,次回のアクセスからは当該デー タを高速な領域から供給するために当該データは移 動されなければならない、しかし、ノンクリティカル アクセスされるデータが高速に供給されても,性能 へ与える影響は小さいことが期待できるからである. これによりデータの移動が必要なキャッシュアクセス は ca\_slow\_hit 時のみとなる.この方式とデータの 重要度を時間的局所性で決する方式を適用した場合 の結果を図8に示す.図において横軸はベンチマー クごとの結果と平均を,縦軸はアクセスの内訳を表 している.CPI-normal は図7に示した改良前の結 果を, CPI-remain は nca\_fast\_hit 時にデータを低 速なウェイに移動させなかった場合の結果をそれぞれ 表し,LRU は時間的局所性を用いてデータの重要度 を決定した場合の結果を表している.改良前と比較し て CPI-remain では, ca\_slow\_hit, nca\_slow\_hit の割合が減って, ca\_fast\_hit, nca\_fast\_hit の割合 が増えている.改良前に平均で全アクセスの21%に対 して必要だったデータの移動が改良後には平均で全ア

Fig. 8 Access comparison.

図 9 クリティカルパス情報を用いたアクセスをした場合の処理性能 Fig. 9 Performance result when used critical path information for cache access.

クセスの 8%にまで抑えられている.LRU の場合,高速な領域のデータがアクセスされると当該データは高速な領域にとどまり,低速な領域のデータがアクセスされるとただちに高速な領域へ移動される.このため,アクセスの傾向はデータの移動を抑制した場合と似ている.移動が必要なアクセスは平均で約3%と非常に少ないが,nca\_fast\_hit の割合が非常に多い.クリティカルパス情報を用いてアクセスする領域を決める場合,アクセスは各領域に対して順番に行われる.したがってnca\_fast\_hit は,低速な領域→高速な領域の順にアクセスされる.この時間が大きいとプログラムのクリティカルパスが入れ替わってしまい,処理性能へ影響を与える可能性がある.

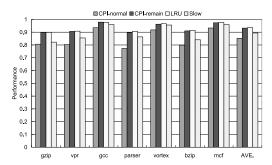

次に、検討するアーキテクチャが処理性能に与える影響を見る.処理性能を図 9 に示す.すべてのウェイが高速な場合の結果で正規化されており、グラフが高いほど処理性能が高いことを示している.Slow はすべてのウェイが低速な場合を示す.すべてのウェイが高速,低速なキャッシュへのアクセスは,従来どおりタグ領域とデータ領域へ並列アクセスを行う.データの入れ替えを抑制しない CPI-normal は、クリティカルパス情報に従った領域選択によるアクセスペナル

図 10 重要度決定方法ごとのエネルギー Fig. 10 Energy results.

ティとデータの入れ替えペナルティによって Slow よりも処理性能が低下してしまう.一方 CPI-remain とLRU の場合,nca\_fast\_hit 時にはデータ供給までにペナルティがかかるものの,どちらも処理性能低下を抑えることができている.これは,これらのデータ配置方法がデータの移動にかかるペナルティを抑制できることと,クリティカルパスに与える影響を小さくできることによる.つまり,nca\_fast\_hit 時にかかるペナルティはクリティカルパスに悪影響を与えるほど大きくない.またどちらの場合も ca\_fast\_hit が増加していることから,クリティカルアクセスされたデータが高速な領域から供給される機会が増している.これが処理性能に良い影響を与え,nca\_fast\_hit の増加という弊害を小さくできている.

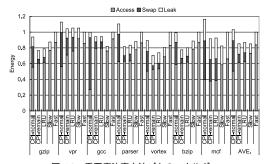

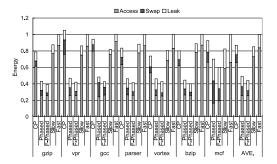

次にエネルギーについて見る.図10にエネルギー の結果を示す. すべてのウェイが高速な場合の結果で 正規化されており、グラフが低いほど消費エネルギー が少ないことを示している. 横軸はベンチマークプロ グラムごとにデータの入れ替え方法を変化させた場合 の結果を表し,縦軸はエネルギーの総量とその内訳を 表す. 縦軸の Access はキャッシュメモリにアクセス したときに消費したエネルギーを, Swap はデータの 入れ替え時に消費したエネルギーを, Leak はリーク 電流により消費したエネルギーをそれぞれ表す.Slow はすべてのデータ領域へアクセスを行っているため、 すべての場合と比較してアクセス時に消費するエネ ルギーが大きい.また CPI-remain, LRU の場合より も処理性能が低下しているため、リーク電流による エネルギーも CPI-remain, LRU の場合より大きい. CPI-normal から CPI-remain , LRU へとデータ入れ 替え方法が変わると, キャッシュメモリへのアクセス 時に消費するエネルギーが増加する.これはクリティ カルパス情報に従った領域選択を行うことに起因する nca\_fast\_hit 増加のペナルティである.しかし,デー タ入れ替え時に消費するエネルギーは減少している.

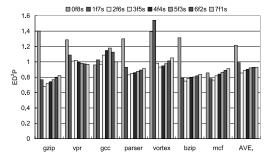

図 11 重要度決定方法ごとの  $ED^2P$  Fig. 11  $ED^2P$  results.

これは、データ入れ替えを抑制する CPI-remain , LRU の効果である.また CPI-remain , LRU では , データ 入れ替え時にかかる処理性能へのペナルティも抑えることに成功しているため , リーク電流による消費エネルギーも抑えることができている .

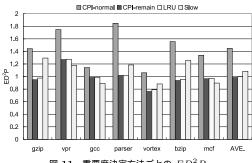

次に  $ED^2P$  の結果を見る.図 11 に結果を示す. すべてのウェイが高速な場合の結果で正規化されてお り,グラフが低いほど省電力であることを示している. Slow では消費エネルギーは抑えられていたが、それ にともなう処理性能の低下の影響で  $ED^2P$  は悪化し ている.CPI-normal ではデータの移動にかかるエネ ルギーとペナルティの影響で  $ED^2P$  が悪化している. データの移動を抑制した場合は,大きく省電力化がで きているものとそうでないものがある.これは,検討 しているアーキテクチャの構造上どうしても起きてし まうデータの移動がクリティカルパスへ影響を与える 頻度とアクセス時のエネルギー削減効果に依存してい る.CPI-remain と LRU で結果に大きな差は見られ ない.しかし,時間的局所性を適用する LRU の方が CPI-remain よりも単純なハードウェアでデータの重 要度を決定できる.よってL1 キャッシュメモリは,時 間的局所性を利用してデータの重要度を決定すること にする.

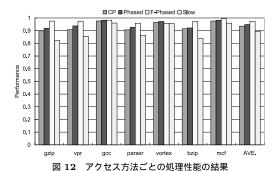

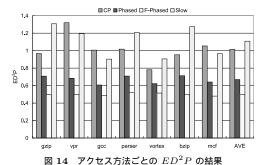

最後に、各領域へのアクセス方法を変えた場合の処理性能、エネルギー、 $ED^2P$  について見る・結果をそれぞれ図 12、図 13、図 14 に示す・図において、CP はクリティカルパス情報を用いてアクセスする領域を決めた場合を、Phased は 5.2 節で説明した段階的アクセスをした場合を、F-Phased は 5.3 節で説明した高速型段階的アクセスをした場合をそれぞれ示している・前述したように、Phased と F-Phased は CP に比べ、早い段階でミスを特定できる・また、全セットのタグを同時に読み出してデータが配置されている場所を特定するので、CP 時に必要な領域ごとのアクセスをする必要がない・このため、アクセス方式

Fig. 12 Performance result of each access technique.

図 13 アクセス方法ごとのエネルギーの結果 Fig. 13 Energy result of each access technique.

Fig. 14  $ED^2P$  result of each access technique.

に CP を用いたときよりも高い処理性能を示している。また処理性能低下も Slow より小さい . 特に高速な領域のデータをタグ比較と同時に読み出す F-Phasedでは,処理性能低下を平均で 2.7%にまで抑えることができている.次にエネルギーについて見る.CP では Fast や Slow の場合よりも悪化する場合も見られたが,CP と比べてアクセスする領域が少ない Phased と F-Phased は,アクセス時に消費するエネルギーを小さくすることに成功している.読み出すデータが低速な領域に存在する場合もタグ比較と同時に高速な領域のデータ領域を読み出す F-Phased は,Phased よりもアクセス時の消費エネルギーが大きい. $ED^2P$  の場合も,必要なウェイにしかアクセスしないことで

Fig. 16 The energy result of L2 cache.

図 15 L2 キャッシュメモリへ適用した場合の処理性能 Fig. 15 The performance result of L2 cache.

消費エネルギーを抑えることに成功した Phased と F-Phased は , すべての領域にアクセスする可能性 のある CP とすべてのウェイが低速な Slow よりも大幅な省電力化を実現できている . 特に遅延が最も小さかった F-Phased の場合 , 平均で  $54\%~ED^2P$  を削減できている .

# 6.3 L2 キャッシュメモリ

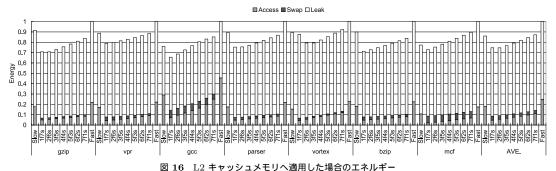

省電力アーキテクチャを L2 キャッシュメモリへ適用した場合の結果を示す .3 章で述べたように ,L2 キャッシュでのデータの重要度は LRU で決定される . アクセスの方法は ,L1 キャッシュメモリへ適用して良い結果が得られた高速型段階的アクセスを用いる .L1 キャッシュメモリは高速な領域と低速な領域の割合が 1:3 で , 時間的局所性を用いてデータを配置し , 高速型段階的アクセスをされるとした . 図中のラベルのうち ,1678 などは L2 キャッシュメモリの高速 , 低速な領域が持つウェイの数を表している .0688 は L1 ,L2 キャッシュメモリのすべての領域が低速な場合を示している . すべての結果は L1 ,L2 キャッシュメモリのすべての領域が高速な場合の結果で正規化されている .

最初に処理性能について見る.図15に処理性能の結果を示す.高速な領域にウェイを1つしか持たない場合は,高速な領域から供給されるデータが少ないこ

図 17 L2 キャッシュメモリへ適用した場合の  $ED^2P$  Fig. 17 The  $ED^2P$  result of L2 cache.

ととデータの入れ替えによるペナルティにより 0f8s よりも処理性能が低下することがある.この処理性能低下は,高速な領域に存在するウェイ数の増加にともない改善されていく.

次に消費エネルギーを見る.図 16 に消費エネルギーの結果を示す.すべての場合でリーク電流による消費エネルギーが大きいことが分かる.高速な領域のウェイ数が増加すると処理性能は改善されるが,高速な領域の増加にともないリーク電流が増加する.このため,リーク電流による消費エネルギーは減少しない.逆にタグ比較時に読み出されるデータ領域が増加するため,アクセス時のエネルギーが増加していく.エネルギーを示すグラフからは,1f7s と 2f6s の場合が消費エネルギーが小さいことが分かる.

最後に  $ED^2P$  の結果を見る.図 17 に  $ED^2P$  の結果を示す.前述したように,高速な領域に置かれるウェイ数が増加するほど処理性能低下は抑制できたが,消費エネルギーは増加した.この消費エネルギー増加分を抑制できた処理性能低下でカバーできれば,高速な領域の増加にともない  $ED^2P$  も改善するはずである.しかし,グラフから分かるように,多くのプログラムで 2f6s の場合が最も  $ED^2P$  を改善できている.その後高速な領域に置かれるウェイ数が増加するにつれ,緩やかに  $ED^2P$  は悪化していく.

処理性能,消費エネルギー, $ED^2P$  のそれぞれの結果から,高速な領域がウェイを 2 つ持つ場合が最適な構成であるといえる.このとき,平均で約 10%の処理性能低下で約 14%の  $ED^2P$  削減を達成できている.ただしプロセッサ全体を考慮すると,10%の処理性能低下によりキャッシュメモリ以外のリーク電流による消費エネルギーの増加が懸念される.しかし,現在のプロセッサではキャッシュメモリの消費するエネルギーが支配的となっている $^{18)}$  ことから,プロセッサ全体でも省電力化が期待できる.

# 7. 関連研究

Abella  $6^{1)}$  と Balasubramonian  $6^{2)}$  は,クリティカルパス情報を用いたデータの配置とアクセスを行うことで,L1 データキャッシュで消費される動的消費電力と静的消費電力を削減することを提案している.

Abella らの提案する L1 キャッシュメモリは 2 つの 独立したキャッシュメモリから構成されている.1つ は高速にアクセスできるが高消費電力なキャッシュで, もう一方はアクセスは低速だが省電力なキャッシュで ある.アクセスは高速・低速なキャッシュへ並列に行 い,タグ領域とデータ領域を読み出す.クリティカル パス上の命令によってアクセスされたデータが低速な キャッシュにあった場合, そのデータの複製が高速な キャッシュへ作られる.クリティカルパス上にない命 令のアクセスするデータが高速なキャッシュにあった 場合は,何も行われない.クリティカルパス上の命令 によるアクセスがミスした場合は, 高速なキャッシュ からデータが供給される.そうでない命令がミスした 場合は、低速なキャッシュからデータが供給される、 データの複製を作るため,高速,低速なキャッシュ間 でコヒーレンシをとる必要があるが,その方法や複製 に必要なレイテンシは検討されていない. キャッシュ ヒットの場合もロード命令のレイテンシが一定ではな くなるため, ロード命令に続く命令のスケジューリン グ方法を検討する必要があるが, その方法については 言及されていない. また, L2 キャッシュメモリの省 電力化については考慮していない.

Balasubramonian らは高速な領域と低速な領域を持つL1キャッシュメモリを提案している.配置予測器と呼ばれる予測器に従って,それらの領域へデータを配置する.データごとにアクセスされた命令がクリティカルであったか否かをカウンタに記録しており,データが追い出される際にカウンタの値に従って配置予測器を更新する.また,ロード命令がアクセスする領域の選択にバンク予測器を用いる.バンク予測器は供給

されたデータが置かれていた領域の情報で更新される. 予測がはずれた場合に備え,タグ読み出しはすべての 領域で行われる.彼らは領域間でのデータの移動は検 討していない.ロード命令に続く命令のスケジューリン グについては言及されていないが,バンク予測器の予 測結果を利用するものと推測される.また,L2キャッ シュメモリの省電力化については考慮していない.

# 8. ま と め

深刻な問題となっているプロセッサの動的・静的消費電力を削減するための省電力キャッシュアーキテクチャを検討した、本稿で検討したキャッシュアーキテクチャは、データの重要度を利用して高速だが高消費電力・低速だが省電力な領域にデータを配置する、これらの領域に対し、すべての領域のタグと高速な領域のデータを読み出し、その後低速な領域のデータを読み出すアクセス方法でアクセスを行った、評価の結果、データの重要度決定には時間的局所性を用いる方が良いこと、すべての領域が高速な L1, L2 キャッシュメモリと比較して、平均で約 10%の処理性能低下で約 14%の  $ED^2P$  削減を達成できることが分かった、

謝辞 本研究の一部は,文部科学省科学研究費補助金(No.16300019, No.176549)の援助によるものです.

#### 参考文献

- 1) Abella, J. and Gonzalez, A.: Power efficient data cache designs, *Proc. International Conference on Computer Design*, pp.8–13 (Oct. 2003).

- 2) Balasubramonian, R., Srinivasan, V., Dwarkadas, S. and Buyuktosunoglu, A.: Hotand-cold: Using criticality in the design of energy-efficient caches, *Proc. Workshop on Power Aware Computer Systems*, pp.180–195 (Dec. 2003).

- Burger, D. and Austin, T.M.: The Simplescalar tool set version 2.0, Technical Report CS-TR-97-1342, University of Wisconsin (June 1997).

- 4) Edmondson, J.H., Rubinfeld, P.I., Bannon, P.J., Benschneider, B.J., Bernstein, D., Castelino, R.W., Cooper, E.M., Dever, D.E., Donchin, D.R., Fischer, T.C., Jain, A.K., Mehta, S., Meyer, J.E., Preston, R.P., Rajagopalan, V., Somanathan, C., Taylor, S.A. and Wolrich, G.M.: Internal organization of the Alpha 21164, a 300-MHz 64-bit quad-issue CMOS RISC microprocessor, Digital Technical Journal, Vol.7, No.1, pp.119-135 (1995).

- Fields, B.A., Rubin, S. and Bodik, R.: Focusing processor policies via critical-path prediction, *Proc. International Symposium on Computer Architecture*, pp.74–85 (July 2001).

- 6) Inoue, K., Ishihara, T. and Murakami, K.: Way-predicting set-associative cache for high performance and low energy consumption, Proc. International Symposium on Low Power Electronics and Design, pp.273–275 (Aug. 1999).

- Inoue, K., Moshnyaga, V.G. and Murakami, K.: Trends in high-performance, low-power cache memory architectures, *IEICE Trans. Electronics*, Vol.E85-C, No.2, pp.304–314 (2002).

- 8) Martonosi, M., Brooks, D. and Bose, P.: Modeling and analyzing CPU power and performance: Metrics, methods and abstractions, Tutorials, SIGMETRICS 2001/Performance 2001 (June 2001).

- 9) Powell, M.D., Agarwal, A., Vijaykumar, T.N., Falsafi, B. and Roy, K.: Reducing set-associative cache energy via way-prediction and selective direct-mapping, *Proc. International Symposium on Microarchitecture*, pp.54–65 (Dec. 2001).

- Semiconductor Industry Association: International technology roadmap for semiconductors, 2005 edition, process integration, devices and structures (Jan. 2006).

- So, K. and Rechtschaffen, R.N.: Cache operations by MRU change, *IEEE Trans. Comput.*, Vol.37, No.6, pp.700–709 (1988).

- 12) Tarjan, D., Thoziyoor, S. and Jouppi, N.P.: CACTI 4.0, Technical Report HPL-2006-86, Hewlett-Parckard Laboratories (June 2006).

- 13) Tune, E., Liang, D., Tullsen, D.M. and Calder, B.: Dynamic prediction of critical path instructions, *Proc. International Symposium on High-Performance Computer Architecture*, pp.185–196 (Jan. 2001).

- 14) Weiss, D., Wuu, J.J. and Chin, V.: The onchip 3Mb subarray based 3 level cache on an Itanium microprocessor, *IEEE International* Solid-State Circuits, Vol.37, No.11, pp.1523– 1529 (2002).

- 15) 小林良太郎,安藤秀樹,島田俊夫:データフロー・グラフの最長パスに着目したクラスタ化スーパースカラ・プロセッサにおける命令発行機構,並列処理シンポジウム,pp.31-38 (June 2001).

- 16) 千代延昭宏, 佐藤寿倫: メモリアクセス命令の 重要度を利用したキャッシュメモリの省電力化, 情報処理学会九州支部火の国情報シンポジウム (Mar. 2004).

- 17) 千代延昭宏, 佐藤寿倫, 有田五次郎: 低消費電 カプロセッサアーキテクチャ向けクリティカルパ ス予測器の提案,並列/分散/協調処理に関するサ マー・ワークショップ,情報処理学会研究報告, 2002-ARC-149-2, pp.7-12 (Aug. 2002).

- Segars, S.: Low-power design techniques for microprocessors, Tutorials, International Solid State Circuits Conference (Feb. 2001).

(平成 18 年 10 月 10 日受付) (平成 19 年 1 月 23 日採録)

# 千代延昭宏(学生会員)

2002 年九州工業大学情報工学部卒業.2004 年同大学大学院情報工学研究科博士前期課程修了.同年九州産業大学情報科学部実習助手.2005 年より日本学術振興会特別研究員.現

在,九州工業大学大学院情報科学研究科博士後期課程 在籍.プロセッサアーキテクチャの研究に従事.IEEE 会員.

#### 藤井誠一郎

2004 年九州工業大学情報工学部 卒業.2006 年同大学大学院情報工学研究科博士前期課程修了.同年日立アドバンスドデジタル入社.

# 佐藤 寿倫(正会員)

1989 年京都大学工学部卒業 . 1991 年同大学大学院工学研究科修士課程 修了 . 同年株式会社東芝入社 . マル チプロセッサアーキテクチャ,消費 電力見積り手法,および組み込み用

マイクロプロセッサの研究開発に従事.九州工業大学情報工学部助教授を経て,現在,九州大学システムLSI研究センター教授.博士(工学).マイクロプロセッサアーキテクチャ,VLSI設計手法に興味を持つ.電子情報通信学会,ACM,IEEE 各会員.