# 広範囲な動作性能領域において エネルギー最小点追跡を可能にするオンチップメモリ

塩見 準<sup>1,a)</sup> 石原 亨<sup>1</sup> 小野寺 秀俊<sup>1</sup>

概要:オンチップメモリはプロセッサの中で最もエネルギーを消費する素子の1つである.したがって,低消費エネルギー化のため電源電圧および基板電圧の調整がオンチップメモリにも適用されている.本稿では,65-nm FDSOIプロセスで製造されたオンチップメモリの測定結果を述べる.既存の6T SRAMマクロと異なり,スタンダードセルベースメモリを使用することで,定格電圧から0.3 Vのような幅広い動作性能領域で動作を可能にする.次に,オンチップメモリの電源電圧および基板電圧を同時に調整し,要求動作速度に対し消費エネルギーを最小化するエネルギー最小点でオンチップメモリを動作させる.DVFS制御と比較して,最大34%消費エネルギーを削減可能であることを示す.

# An On-Chip Memory Enabling Minimum Energy Point Tracking over a Wide Operating Performance Range

Jun Shiomi $^{1,a)}$  Tohru Ishihara $^1$  Hidetoshi Onodera $^1$

Abstract: On-chip memory is one of the most energy consuming components in processors. Aggressive supply voltage scaling and adaptive body biasing are thus applied even to the on-chip memories. In this paper, an on-chip memory is designed to investigate a minimum energy point in a 65-nm FDSOI process technology. Unlike conventional on-chip memories, it employs standard-cell based memories (SCMs) as an alternative to conventional 6T SRAM macros, enabling it to operate at 0.3 V supply voltage. Then, simultaneous tuning of supply and threshold voltage is applied to the SCM, which enables it to operate with minimum energy consumption under a specific clock period. Measurement results show that the energy consumption of the SCM is reduced by 32% in comparison with the conventional DVFS technique.

## 1. 序論

集積回路の微細化により回路の高性能化と普及が実現され、集積回路を用いた新しい応用事例が登場している. IoT (Internet of Things) は何十億もの情報通信機器が相互結合され、情報の自動交換が実現される新しい構想として登場した. これらのネットワークでは、旧来のテキストベースデータよりはるかに複雑なマルチメディアデータの交換が行われている. IoT を支えるマイクロプロセッサは限られたバッテリ容量で動作する必要があり、これらのマイクロプロセッサには高い演算能力を維持しながら、クロックサイクル毎に消費するエネルギーを最小限にすることが求められる.

低消費エネルギーを実現する最も有効な手法の1つとして、DVFS (Dynamic Voltage and Frequency Scaling) が2000年に提案された。要求動作速度に応じて電源電圧およびクロック周波数を動的に調整することで、回路の消費エネルギーを効果的に削減することができる。しかしながら、DVFS により回路の電源電圧が低くなるとサブスレッショルドリーク電流を要因とする静的消費エネルギーが増大する。この問題を解決するため、2000年代には、回路の電源電圧 ( $V_{\rm DD}$ ) およびしきい値電圧 ( $V_{\rm th}$ ) を同時に調整する技術が活発に研究された [1-3]. IoT のような高い演算能力と低い消費エネルギーが求められる応用では、動的に変動する要求動作速度に応じて  $V_{\rm DD}$  と  $V_{\rm th}$  を動的に調整し、

常に最小の消費エネルギーで回路を動作させるエネルギー最小点追跡が注目されている。回路のしきい値電圧は、トランジスタの基板電圧  $(V_{\rm BB})$  を調整することにより変更することができる。動的にトランジスタの基板電圧を変更する技術は ABB (Adaptive Body Biasing) と呼ばれている。完全空乏型 SOI (Fully Depleted Silicon On Insulator: FDSOI) 技術の登場により、従来のバルク型トランジスタと比較して  $V_{\rm BB}$  の制御範囲が拡大した。FDSOI の商用展開が近年実現し、 $V_{\rm DD}$  と  $V_{\rm th}$  の同時調整技術が再び注目されている。

オンチップメモリは集積回路の性能を律速する代表的な 素子の1つである.電源電圧および基板電圧の同時調整技 術を前述の応用例に適用すると、オンチップメモリが $V_{th}$ 近傍かそれより低い電源電圧で動作することが必要になる. しかしながら、これらの極端に低く設定された電圧領域で はオンチップメモリとして最もよく使用される 6T SRAM マクロのスタティックノイズマージンが劇的に悪化し,6T SRAM マクロが正常に機能しない. SRAM の代替マクロ として、スタンダードセルベースメモリ (Standard-Cell based Memory: SCM) がここ 10年の間, 重点的に研究さ れている [4-7]. SCM ではスタンダードセルのみが使用さ れているため、SCM の極低電圧での安定動作を保証しな がら、設計コストを完全自動化されたセルベースデザイン まで削減することができる. 本稿では, 65-nm FDSOI プ ロセスで製造されたオンチップメモリを幅広い電源電圧お よび基板電圧に対して動作させる. SRAM の代替マクロ として SCM を用いることで, 0.3 V のような極低電圧で

京都大学大学院情報学研究科

a) shiomi-jun@vlsi.kuee.kyoto-u.ac.jp

安定して動作し、広範囲な動作性能領域において回路が動作可能であることを実測に基づき示す.次に、SCM が幅広い動作性能領域において要求動作速度に応じて最小のエネルギー消費で動作することが可能であることを実チップ測定に基づき示す.

本稿の構成を以下に示す.第2章では関連研究と本稿の成果に関して述べる.第3章で,提案する SCM 構造の述べ,評価回路の構成を述べる.第4章で SCM の消費エネルギーおよび動作速度の測定結果を示し,エネルギー最小点追跡の優位性を示す.第5章で結論を述べる.

## 2. 関連研究と本稿の成果

動的に変化するプロセッサの仕事量に対し、 $V_{BB}$  および  $V_{

m DD}$  を調整する技術が 2000 年代から活発に研究されてい る [1-3]. 電源電圧を下げることにより, 回路の動的消費エ ネルギーが電源電圧の2乗に比例して効率的に削減できる 一方,電源電圧の低下により回路の遅延が増大し,回路の 静的消費エネルギーが増大する. 一方, トランジスタの基 板電圧を調整することにより, トランジスタのしきい値電 圧  $(V_{th})$  を変更することができ、 $V_{th}$  を大きくすることで遅 延は悪化するものの静的消費エネルギーを効率的に削減す ることができる. この事実は, 回路の総消費エネルギーは  $V_{

m DD}$  および  $V_{

m th}$  の凸関数であることを意味している. した がって、特定の固定されたクロック周期のもと、総消費エ ネルギーを最小化する  $V_{\mathrm{DD}}$  および  $V_{\mathrm{th}}$  が存在し、本稿では この組を MEP (Minimum Energy Point) と呼ぶ. 文献 [8] では、CMOS 回路の単純な性能モデルに基づき、MEP を 閉形式関数で記述することに成功している. その結果によ ると、回路が MEP で動作するとき、総消費電力に対する 回路の静的電力の比はおよそ 30% になることが示されて いる. 文献 [9] では, 文献 [8] の議論を拡張し, 総消費エネ ルギーに対する回路の静的消費エネルギーの比を次の閉形 式関数で記述した.

$$\frac{E_{\rm d}}{E_{\rm s}} = \frac{\alpha V_{\rm DD} - (V_{\rm DD} - V_{\rm th})}{2 N_{\rm s} \alpha} - \frac{1}{2} \quad (V_{\rm DD} \gg V_{\rm th}) \,. \eqno(1)$$

ここで、 $V_{\rm DD}$  と  $V_{\rm th}$  は MEP に対応する電圧条件である.  $N_{\rm s}$  は理想係数 n と熱電圧  $\phi_T$  の積で、 $\alpha$  はアルファ乗則 モデルのパラメータである [10]. この値は一定ではなくお よそ15%から30%まで変動することを示し、回路の活性 化率および温度に依存することを述べている. 以上の事実 は, エネルギー効率の良い回路動作を実現する場合, 回路 の動的消費エネルギーと静的消費エネルギーの均衡が重要 であることを述べている. 例えば, オンチップメモリのよ うな回路では、値の保持を行うビットセルが回路面積の大 部分を占めるため、オンチップメモリの総消費エネルギー に対して静的消費エネルギーが占める割合が非常に大き い. したがって,回路の $V_{\rm th}$ および $V_{\rm DD}$ をともに増大させ ることにより、回路の動作速度を悪化させることなく静的 消費エネルギー、すなわち総消費エネルギーを効率的に削 減できる. この事実は、チップに異なる活性化率を持つマ クロが搭載されているとき、 $V_{\rm th}$  および  $V_{\rm DD}$  は、マクロ毎 に独立して調整することで、エネルギー効率を改善するこ

とができることを示唆している。一般に、オンチップメモリはビットセルがその面積のほとんどを占めているため、活性化率はロジック部と比較して小さい。したがって、プロセッサのロジック部およびオンチップメモリで独立して $V_{\rm th}$  および  $V_{\rm DD}$  を制御することが、エネルギー効率改善に有効であることが示唆される。

オンチップメモリは Within-Die (WID) ばらつきに最も 脆弱なマクロの一つである.極低電圧領域において、WID ばらつきが回路性能に与える影響は大きいため、一般的な 6T SRAM マクロは読み出し、書き込み、 値保持の各操作 において正しく動作しないようになる. したがって, 広範 囲な動作性能領域において 6T SRAM マクロを動作させる ことは困難である.数多くの論文が、ビットセルの冗長化、 トランジスタサイジング、多電源制御、センスアンプの改 良,周辺補助回路の追加等,SRAM の安定性を改善する技 術を提案している [11-13]. しかしながら, これらのフルカ スタム設計に必要な設計コストは非常に大きい.この問題 を解決する1つの方法として、スタンダードセルベースメ モリ (Standard-Cell based Memory: SCM) が 2000 年代か ら活発に研究されている [4,5,14]. ラッチ回路がビットセ ルに使用され,その他の周辺回路はすべてスタンダードセ ルで設計される. したがって, 通常のロジック回路と同程 度まで電源電圧を下げることができ、劇的なエネルギー効 率の改善を実現することが可能である. また, 設計コスト も完全自動セルベース設計の段階まで低減することができ る. しかしながら、通常のフルカスタムされた SRAM マク 口と比較して面積オーバーヘッドが大きいことが SCM の 欠点である. 本稿では, 65-nm FDSOI プロセスで設計さ れた SCM に関して議論する. 広範囲な電源電圧および基 板電圧に対して SCM が MEP で動作可能であることを実 測に基づき初めて示す. 我々の知る限り, 本稿はオンチッ プメモリのエネルギー最小点動作が可能であることを述べ た最初の論文である. 本稿の成果を以下にまとめる.

- SCM をオンチップメモリとして使用することにより, 広範囲な動作性能領域において安定した動作が可能に なった. 特に,電源電圧 0.3 V, 基板電圧 -1.13 V で の極低電圧動作が可能である.

- 電源電圧および基板電圧の調整を SCM に適用した結果, エネルギー最小点で SCM が動作可能であることを実測に基づき初めて示す. 電源電圧のみ動的に制御する DVFS 制御と比較して, 動作速度を悪化させることなく消費エネルギーを最大 34%改善可能であることを実測に基づき示す.

- SCM の SRAM に対する欠点は面積オーバーヘッドである。本稿では、最小高さスタンダードセル (Minimum Height Standard Cell: MHSC) を用いることで、このオーバーヘッドの削減を行う。MHSC は、ロジックデザインルールで CMOS 回路を設計する時に許される最小のセル高さを持っている。この MHSC が提案 SCM に実装され、ビットセルあたり  $8.46~\mu m^2$  (すなわち、ビットセルあたり  $846F^2$ ) の面積効率を実現した。この値は既存研究の最も面積効率の良い SCM よ

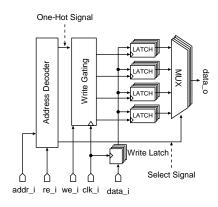

図 1 提案 SCM 構造.

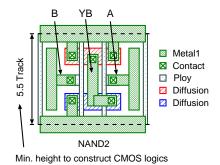

図 2 最小高さスタンダードのレイアウト例.

りわずかに良く, また, SRAM と比較して +191%の 面積オーバーヘッドである.

## 3. 幅広い動作性能領域において動作する完全 ディジタルオンチップメモリ

本章では、提案するスタンダードセルベースメモリの構造に関して述べる.次に、試作チップの回路構造全体に関して述べる.

## **3.1** 最小高さスタンダードセルを用いた完全ディジタル オンチップメモリ

本稿で議論するオンチップメモリは、図1に示すシングルクロックサイクルで動作する SCM である。D-ラッチが記憶素子に使用され、マルチプレクサツリーが読み出し回路に使用される。マルチプレクサツリーは2入力マルチプレクサ(MUX2)の2分木構造となっており、文献[4,15]などの SCM で幅広く使用されている。SCM はディジタル回路のみで構成されているため、その動作可能電圧は通常のロジック回路と同じ値まで下げることができる。

前章で述べた通り、SCMの面積は一般的に SRAM と比較して数倍大きい。したがって、SCMの欠点はその面積オーバーヘッドである。本稿では、面積効率に特化したスタンダードセルを用いることで、面積オーバーヘッドを削減する SCM 構造を提案する。一般的に、スタンダードセルライブラリは FADD、EXOR、DFF といった複雑な論理を搭載している。配線容易性を保つため、一般的なスタンダードセルは配線トラックの 6, 9, または 12 倍の高さを持っている。しかしながら、SCMではアドレスデコーダや読み出しマルチプレクサのような単純な回路のみ使用

表 1 5.5-配線トラック最小高さスタンダードセルライブラリ.

| 論理      | 駆動力                      |

|---------|--------------------------|

| INV     | 1X, 2X, 4X, 8X, 16X, 32X |

| NAND2   | 1X, 2X                   |

| NOR2    | 1X, 2X                   |

| MUX2    | 1X                       |

| D-LATCH | 1X                       |

するため,このような複雑な論理ゲートは必要ではない. したがって、本稿では表1に示すような単純な論理のみ搭 載している最小高さスタンダードセル (Minimum Height Standard-Cell: MHSC) を用いて SCM を設計する. これ らの単純な論理では通常のスタンダードセルより簡単に配 線を行うことができるため、スタンダードセルの高さを低 く設計することができる. MHSC の概念図を図2に示す. MHSC は CMOS ロジックを構成する最小の高さを持って おり、その高さはマスクデザインルールに強く依存する. 例えば 65-nm FDSOI プロセステクノロジの場合,この高 さは NAND2 ゲートにより決定され, 5.5-配線トラックと なる. ここで, 5.5-配線トラックは 11F の高さに対応す る. MHSC に対して、依然として、商用配置配線ツール を使用することが可能である. したがって, 設計コストは フルカスタム SRAM と比較して小さい. MHSC を搭載し た SCM が後に示す試作回路に搭載され、その面積効率と してビットセルあたり  $8.46~\mu m^2$  (すなわちビットセルあ たり  $846F^2$ ) を実現した. なお, この値は周辺回路も含め た SCM すべての面積をビットセル数で割った値である. この値は、既存研究で最も面積効率の良い SCM のビット セルあたり  $8.51~\mu\text{m}^2$  よりわずかに良い [7]. フルカスタム SRAM に対する SCM の面積オーバーヘッドを CACTI モ デルにより求める [16]. 提案 SCM の SRAM に対する面 積オーバーヘッドは +191% である.

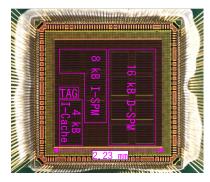

## 3.2 試作チップの構成と測定条件

本稿の測定回路は,65-nm FDSOI プロセステクノロジで製造された 32 ビット 5 段パイプライン RISC プロセッサである.測定回路の写真を図 3 に示す.測定回路のプロセッサにはオンチップメモリとして以下に示す SCM が搭載されている.

- 4 kB 命令キャッシュ (I-Cache)

- 8 kB 命令スクラッチパッドメモリ (I-SPM)

- 16 kB データスクラッチパッドメモリ (D-SPM)

オンチップメモリの電源電圧および基板電圧を自由に制御可能であり、消費エネルギーを測定可能な構成である. 詳細な電源構成を以下に示す.

- プロセッサのロジック部および SCM の電源電圧は独立している. 本稿では、ともに同じ電圧値を設定し、様々な電源電圧および基板電圧に対して SCM の電源に流れる電流から消費エネルギーを測定する.

- SCM マクロでは、nMOS トランジスタおよび pMOS トランジスタの基板電圧をロジック部と独立して設定することができる。本稿では、簡単のため、nMOS, pMOS トランジスタの基板電圧としてそれぞれ  $V_{BB}$ .

図3 試作した RISC プロセッサの写真.

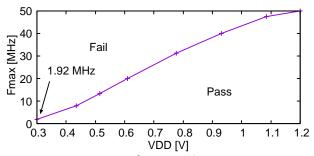

図 4 SCM の Shmoo プロット. 基板電圧は 0 V である.

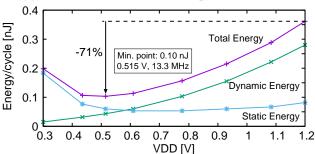

図 5 SCM の消費エネルギー. 基板電圧は 0 V である.

$V_{

m DD}-V_{

m BB}$  を設定する.本稿ではこの構成を単純に基板電圧  $V_{

m BB}$  と表現する.

• ロジック部では、プロセッサの設計を単純にするため、pMOS トランジスタの基板電圧のみ自由に調整することができる. 本稿では、SCM マクロの pMOS トランジスタと同じ基板電圧を設定する.

SCM がクリティカルパス遅延の 95%程度を占めるように 測定対象のプロセッサが設計されている. したがってプロセッサの最大動作周波数 (Maximum operating frequency: Fmax) が SCM の Fmax に対応すると仮定する. プロセッサの外部に主記憶が接続されており, 離散コサイン変換 (Discrete Cosine Transform: DCT) 演算を連続実行するようプログラムされている. 本稿では, DCT を連続実行している時の Fmax および消費エネルギーを様々な電源電圧および基板電圧に対して評価する. なお, SCM はクロックゲーティングを行なっていないため, クロックサイクル毎に SCM が活性化される.

## 4. オンチップメモリの性能測定

#### 4.1 DVFS 制御による消費エネルギー削減

図4にプロセッサが DCT 演算を実行するときの Shmoo

プロットを示す。基板電圧は 0 V に設定されている。SCMをオンチップメモリとして使用することで,動作可能電圧が 0.3 V まで拡大し,そのときの F Fmax は 1.92 MHz である。一般的な S RAM 回路ではこのような極低電圧領域では安定して動作しない。例えば,幅広い電源電圧で動作し,ロジック部が 280 mV で動作可能な文献 [17] のプロセッサに搭載されている 10 T S RAM マクロの最低動作可能電圧は 0.55 V である。本稿の S CM は幅広い動作性能領域で動作が可能である一方, $V_{DD}=1.2$  V の定格電圧ではこの S CM O F Fmax は高々 50 MHz であり,S RAM マクロのように G Hz オーダでの動作は不可能である。エネルギー効率ではなく高い演算能力が求められる計算サーバのような 用途では提案 S CM O 使用は不適切である。

プロセッサが DCT プログラムを実行する時の SCM の 1サイクルあたりの消費エネルギーを図5に示す.ここで, プロセッサの1サイクルあたりの消費エネルギーはクロッ ク周波数が Fmax の際に最小化されるため、プロセッサに は Fmax が与えられている. 測定結果によると, 定格電圧 1.2 V において消費エネルギーはクロックサイクルあたり 0.36 nJ である. 電源電圧を下げることによって, プロセッ サの動的消費エネルギーが減少する一方, 静的消費エネル ギーが低電圧領域で増大する. その結果, プロセッサの総 消費エネルギーは電源電圧 0.515 V のとき最小となり, そ の値は定格電圧動作時より 71%小さい 0.10 nJ/cycle であ る. エネルギー最小点において,電源電圧が低くなると,オ ンチップメモリの Fmax が悪化するため全消費エネルギー に対する静的消費エネルギーの割合が増大する. 第2章で 述べたように、静的消費エネルギーを削減するため、低電 圧領域において SCM の  $V_{\mathrm{DD}}$  および  $V_{\mathrm{th}}$  を大きく設定す ることで動作速度を悪化させることなく消費エネルギーを さらに改善することが可能であることを示唆している.

## 4.2 オンチップメモリのエネルギー最小点の軌跡

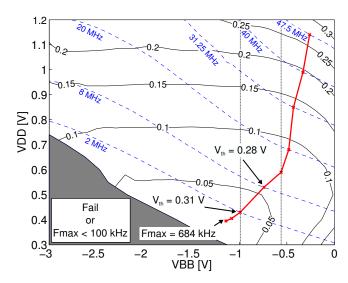

図6にオンチップメモリのFmax 等高線と消費エネル ギー等高線を示す. 横軸はオンチップメモリの基板電圧  $V_{

m BB}$  であり,負方向に大きくすると,オンチップメモリのし きい値電圧が大きくなる. 縦軸はオンチップメモリの電源 電圧である.実線が消費エネルギー等高線,破線が Fmax 等高線である. 消費エネルギーの単位は nJ/cycle である. 太い実線で示された折れ線はオンチップメモリの MEP の 軌跡である.図6の MEP よりさらに低速側に MEP が続 くが、測定機器の測定限界 10 μA に達したため消費エネ ルギーの測定を行なっていない.また,"Fail or Fmax < 100 kHz"と書かれた領域は回路が 100 kHz 未満で動作す るか, または正常動作しない領域である. トランジスタの しきい値電圧をトランジスタレベルシミュレーションで定 電流法により求めた結果, Fmax が8 MHz であるときの MEP ではしきい値電圧は 0.28 V であり、Fmax が 2 MHz であるときの MEP ではしきい値電圧は 0.31 V である. 提 案 SCM は 0.3 V, 基板電圧 -1.13 V のような極低電圧で正 常に動作し,通常の 6T SRAM マクロはこのような極低電 圧で動作しない. 低速動作するにつれて、MEP が図6の

図 6 消費エネルギー等高線、Fmax 等高線と MEP. 実線: エネル ギー等高線、破線: Fmax 等高線、太い実線: MEP の軌跡、 エネルギーの単位は nJ/cycle.

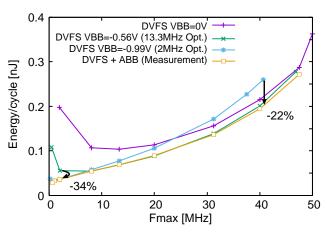

図 7 DVFS 制御と MEP 動作の消費エネルギーの変化.

左側へ移動していることから,前節で述べた通りクロックサイクルあたりの消費エネルギーを最小化するためには,低電圧領域でしきい値電圧を高く設定する必要があることがわかる.

#### 4.3 エネルギー最小点動作による消費エネルギー削減

DVFS 制御のみを行った際の消費エネルギーと、MEPで動作を行った時のエネルギー消費を比較した結果を図7に示す、横軸はオンチップメモリのFmaxに対応し、縦軸はオンチップメモリの消費エネルギーである。"DVFS VBB=\*\*V"と書かれた線は、対応する基板電圧を固定値として与え、DVFS 制御した結果に対応する。例えば、"DVFS VBB=-0.56V (13.3MHz Opt.)"は図6において $V_{\rm BB}=-0.56$  Vの点線部分で $V_{\rm DD}$  を変更し、横軸にFmaxを、縦軸に消費エネルギーを示したグラフに対応する。"DVFS + ABB (Measurement)"は回路を MEPで動作させるときのFmax および消費エネルギーを示したものである。基板電圧として $V_{\rm BB}=0$  Vを設定すると、Fmaxが高い領域において MEPで動作を行った結果と近い消費エネルギーになる一方で、低電圧に近づくにつれ消費エネ

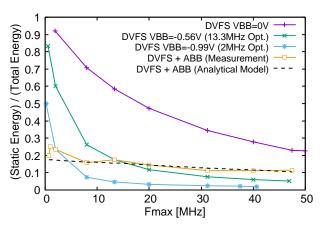

図 8 全消費エネルギーに占める静的消費エネルギーの割合.

ルギーは悪化する. $V_{

m BB}$  を-0.56~

m V に設定すると,8~

m MHz以上の領域において MEP で動作したときとほぼ同じ消費 エネルギーを実現し、消費エネルギーのオーバーヘッドは 高々 +4%程度である. 強反転領域において MEP は垂直 に近い軌跡を描くため,V<sub>BB</sub> を適切な固定値に設定する と消費エネルギーのオーバーヘッドを低減することがで きる. この事実は文献 [9] において解析モデルを用いて示 されており, 例えばオンチップメモリの容量が変化したと きや、演算命令が変化しアクセス頻度が変化しても成立す ることが予想される.一方で、Fmaxが2MHz以下の極 低電圧領域において、消費エネルギーの差が34%発生す る. これは、オンチップメモリの Fmax が悪化し、全消費 エネルギーに対する静的消費エネルギーの割合が増大し,  $V_{\rm BB} = -0.56~{

m V}$  の線から MEP が遠ざかるためである. 逆 に  $V_{\mathrm{BB}}$  を  $-0.99~\mathrm{V}$  に設定し、極低電圧領域で MEP で動作 するよう  $V_{

m BB}$  を調整すると, ${

m Fmax}$  が高い領域において消 費エネルギーの差が発生し,その値は最大 22%である.こ れは、先ほどの議論と同様に、全消費エネルギーに対する 動的消費エネルギーの割合が増大することが原因である. 以上の事実は、動的に仕事量が変化する IoT のようなシス テムにおいて, 電源電圧と基板電圧の同時調整が重要な要 素技術になることを示唆している.

図7と同じデータに対し、SCM の全消費エネルギーに 対する静的消費エネルギーの割合を示した結果を図8に 示す. "DVFS VBB=\*\*V"および "DVFS + ABB (Measurement)"と書かれた線は図7と同じデータに対応する. "DVFS + ABB (Analytical Model)"は文献 [9] において議 論されている強反転領域の MEP において成立する動的消 費エネルギーおよび静的消費エネルギーの比(1)に実測し た MEP 軌跡の点  $(V_{\rm BB},\ V_{\rm DD})$  を代入した結果を示してい る. ただし、 $V_{BB}=0$  V かつ  $V_{DD}=1.2$  V の時のしきい値 電圧をトランジスタレベルシミュレーションで定電流法に より求め、しきい値電圧変動  $\Delta V_{\mathrm{th}}$  が  $V_{\mathrm{BB}}$  および  $V_{\mathrm{DD}}$  に対 して線形に変化すると仮定し、それらの値と  $\alpha$  および  $N_{\rm s}$ をトランジスタ単体の電流特性からフィッティングにより 求めた. MEP上でSCM が動作すると、消費エネルギーの 比は11%から24%の間をゆるやかに変動し、常に動的消費 エネルギーと静的消費エネルギーの均衡が守られている.

また、モデル式から得られた値と実測値がFmax 8 MHz 以 上の MEP に おいて +14%以内の誤差で一致する. この事 実は文献 [9] で用いられた解析的な議論が実チップにおい て正しいことを示している. "DVFS VBB=\*\*V"のいずれ のデータも、電源電圧が低くなると、静的消費エネルギー の割合が増大している. DVFS 制御時の静的消費エネル ギーの割合が "DVFS + ABB (Measurement)" と大きく異 なる動作領域において, "DVFS + ABB (Measurement)" と比較した DVFS 制御の消費エネルギーのオーバーヘッ ドが増大する. 文献 [8,9] で述べられているように、MEP 上では、動的消費エネルギーと静的消費エネルギーの割合 が重要であることが実測により確かめられた. また, 動的 に要求速度が変わり, 広範囲な動作性能領域において低消 費エネルギーを実現する必要がある場合, 動的消費エネル ギーおよび静的消費エネルギーの均衡を保つため、電源電 圧および基板電圧の同時調整技術が必要であることが以上 の結果より確かめられた.

## 5. 結論

電源電圧としきい値電圧の同時調整は、集積回路のエネルギー効率を高める重要な技術である。本稿では、定格電圧 1.2 V から 0.3 V のような極低電圧まで幅広く安定して動作する SCM を提案した。面積効率の良いスタンダードセルを用いることで、既存の SCM よりわずかによい面積効率を実現した。次に、SCM の DVFS 制御を行い、定格電圧動作から 71%の消費エネルギーの削減を実現した。最後に、電源電圧およびしきい値電圧の同時調整を行い、SCM をエネルギー最小点で動作させた。 DVFS 制御と比較して、最大 34%消費エネルギーを削減できることを示し、動的に要求動作速度が変化する IoT のようなシステムには、エネルギー最小点追跡が重要であることを示した。

### 謝辞

本研究は JSPS 科研費 (16H01713 および 16J08694) による 支援によって行われた. 本研究は東京大学大規模集積システム 設計教育研究センターを通し,シノプシス株式会社,日本ケイデンス株式会社,メンター株式会社の協力で行われた.

#### 参考文献

- L. Yan, J. Luo, and N. Jha, "Joint Dynamic Voltage Scaling and Adaptive Body Biasing for Heterogeneous Distributed Real-Time Embedded Systems," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 24, no. 7, pp. 1030–1041, July 2005.

- [2] S. Martin, K. Flautner, T. Mudge, and D. Blaauw, "Combined Dynamic Voltage Scaling and Adaptive Body Biasing for Lower Power Microprocessors under Dynamic Workloads," in *International Conference on Computer Aided Design*, Nov 2002, pp. 721–725.

- [3] A. Basu, S.-C. Lin, V. Wason, A. Mehrotrat, and K. Banerjee, "Simultaneous Optimization of Supply and Threshold Voltages for Low-Power and High-Performance Circuits in the Leakage Dominant Era," in Design Automation Conference, July 2004, pp. 884–887.

- [4] A. Wang and A. Chandrakasan, "A 180-mV Subthresh-

- old FFT Processor using a Minimum Energy Design Methodology," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 1, pp. 310–319, Jan. 2005.

- [5] P. Meinerzhagen, S. M. Y. Sherazi, A. Burg, and J. N. Rodrigues, "Benchmarking of Standard-Cell Based Memories in the Sub-VT Domain in 65-nm CMOS Technology," *IEEE Trans on Emerging and Selected Topics* in Circuits and systems, vol. 1, no. 2, pp. 173–182, June 2011.

- [6] A. Teman, D. Rossi, P. Meinerzhagen, L. Benini, and A. Burg, "Controlled Placement of Standard Cell Memory Arrays for High Density and Low Power in 28nm FD-SOI," in Asia and South Pacific Design Automation Conference, Jan 2015, pp. 81–86.

- [7] O. Andersson, B. Mohammadi, P. Meinerzhagen, and J. Rodrigues, "A 35 fJ/bit-access Sub-VT Memory Using a Dual-Bit Area-Optimized Standard-cell in 65 nm CMOS," in *European Solid State Circuits Conference*, Sept 2014, pp. 243–246.

- [8] K. Nose and T. Sakurai, "Optimization of VDD and VTH for Low-power and High Speed Applications," in Asia and South Pacific Design Automation Conference, Jan 2000, pp. 469–474.

- [9] 竹下俊宏, 塩見準, 石原亨, and 小野寺秀俊, "CMOS LSI におけるエネルギー最小点追跡のための電源電圧としき い値電圧の動的調節指針," in 情報処理学会研究報告, Vol. 2016-SLDM-175, No. 32., Mar 2016, pp. 1–6.

- [10] T. Sakurai and A. Newton, "Alpha-Power Law MOSFET Model and its Applications to CMOS Inverter Delay and Other Formulas," *IEEE Journal of Solid-State Circuits*, vol. 25, no. 2, pp. 584–594, Apr 1990.

- [11] J. Chen, L. T. Clark, and T.-H. Chen, "An Ultra-Low-Power Memory With a Subthreshold Power Supply Voltage," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 10, pp. 2344–2353, Oct. 2006.

- [12] G. Chen, D. Sylvester, D. Blaauw, and T. Mudge, "Yield-Driven Near-Threshold SRAM Design," Very Large Scale Integration Systems, vol. 18, no. 11, pp. 1590–1598, Nov 2010.

- [13] M. Qazi, M. Sinangil, and A. Chandrakasan, "Challenges and Directions for Low-Voltage SRAM," *Design Test of Computers*, *IEEE*, vol. 28, no. 1, pp. 32–43, Jan. 2011.

- [14] P. Meinerzhagen, C. Roth, and A. Burg, "Towards Generic Low-Power Area-Efficient Standard Cell Based Memory Architectures," in *IEEE International Midwest Symposium on Circuits and Systems*, Aug 2010, pp. 129–132.

- [15] J. Shiomi, T. Ishihara, and H. Onodera, "An Energy-Efficient On-Chip Memory Structure for Variability-Aware Near-Threshold Operation," in *International Symposium on Quality Electronic Design*, March 2015, pp. 23–28.

- [16] S. J. E. Wilton and N. Jouppi, "CACTI: An Enhanced Cache Access and Cycle Time Model," *IEEE Journal* of Solid-State Circuits, vol. 31, no. 5, pp. 677–688, May 1996.

- [17] S. Jain, S. Khare, S. Yada, V. Ambili, P. Salihundam, S. Ramani, S. Muthukumar, M. Srinivasan, A. Kumar, S. Gb, R. Ramanarayanan, V. Erraguntla, J. Howard, S. Vangal, S. Dighe, G. Ruhl, P. Aseron, H. Wilson, N. Borkar, V. De, and S. Borkar, "A 280mV-to-1.2V Wide-Operating-Range IA-32 Processor in 32nm CMOS," in *IEEE International Solid-State Circuits Conference*, Feb. 2012, pp. 66–68.