# 極低電圧動作を目指した D-Nwell レス細粒度基板バイアス SRAM ビットセルの検討

## 中馬 良兵 西澤 真一 伊藤 和人 埼玉大学 工学部

概要 集積回路の低消費エネルギー化のためには電源電圧の低下が有効である.しかし集積回路を構成する SRAM は論理回路よりも最低動作電圧が高い問題がある.電源電圧の低下によってトランジスタの駆動電流が低下すると,負荷となる非活性ビットセルのリーク電流によって低電圧動作が困難になる.ビットセルのリーク電流を選択的に制御する手法として,基板バイアス制御があげられる.アクセストランジスタは高い駆動電流を得るために NMOS トランジスタが利用されているが,P 型基板上の NMOS トランジスタに基板バイアスを印加するためには Deep N-Well 層が必要であり,コストが上昇する問題がある.本研究では,Deep N-Well 層を使わずに基板バイアスによるビットセルの閾値電圧の選択的制御を行うために,アクセストランジスタに PMOS を利用する SRAM ビットセルを提案する.

## Fine-Grain Body Biasing Aware SRAM Bitcell Structure for Ultra Low Voltage Operation

Ryohei Chuma, Shinichi Nishizawa, and Kazuhito Ito Faculty of Engineering, Saitama University

### Abstract

Lowering the supply voltage is one of a solution to achieve higher energy efficiency for VLSI circuits. Minimum operation voltage for the SRAM circuit is higher than that of the digital circuit thus it limits the minimum supply voltage for overall VLSI circuit. The minimum operation voltage for the SRAM circuit is limited by the leakage current of the access transistors inside the SRAM bitcells. Body bias technique is one of a solution to controll the leakage current of access transistors. Conventional SRAM bitcell uses NMOS transistor as an access transistor thus Deep N-Well layer is required for individual body bias. We proposes a SRAM bitcell with PMOS access transistor for Deep N-Well less individual body biasing and evaluate its impact on SRAM low voltage operation.

## 1 序論

集積回路の用途が広がるにつれ,集積回路のエネルギー効率の向上が強く求められている.集積回路のエネルギー効率の向上の実現方法の一つとして,電源電圧の低下が挙げられる.集積回路では一般にデジタル回路と,デジタル回路の入出力情報を記憶する大容量の記憶素子として SRAM 回路が混載される.デジタル回路に比べ SRAM 回路が動作可能な最低動作電圧が低いため,集積回路全体の電源電圧は SRAM 回路によって決定されてしまう.これは SRAM ビットセル中のアクセストランジスタのオン電流が電源電圧によって減少するため,負荷となる非活性ビットセルのアクセストランジスタのリーク電流の影響によって SRAM としての動作が出来なくなるためである.

SRAM 回路の低電圧動作を実現するため,一般的に用いられる 6 トランジスタ (6T) 構造ではなく,アクセストランジスタでのリーク電流の影響を軽減する 8T 構造の SRAM が提案されている [1].他にも,ビットセルおよびビット線の電圧を変える事で,書き込みマージン,読み込みマージンを改善する手法が提案されている.アクセストランジスタのオン電流を補償するためにアクセストランジスタの電

圧をバイアスする手法 [2] . SRAM ビットセルの電圧を下げる事による書き込みマージン向上 [3] [4] [5] , ワード線の電圧を下げる事による SNM 向上などが挙げられる [4] [5] [6] . しかし,これらの手法では大量に集積するビットセルにトランジスタの追加が必要であったり,電源資源の追加が必要がある.

トランジスタの電流特性を変化する手法として,基板バイアス制御が挙げられる.活性化するビットセルと非活性ビットセルの基板電圧を選択的に制御する事で,リーク電流とオン電流の制御を同時に行う事が出来る.しかし,通常の SRAM は高いオン電流特性を持つ NMOS をアクセストランジスタとして利用するため,一般的な P 型基板を持つ  $Twin-Well\ CMOS$  では選択的な基板バイアスの印加を行う事が出来ない.

文献 [7] では, Twin-Well CMOS 構造を持つ SRAM 回路において,電圧をプルアップする PMOS を選択的に基板バイアス印加する手法を提案している.しかし, PMOS によるプルアップはデータの書き込み時であり, SRAM 回路の動作特性にもっとも影響を与える読み出し速度の改善に効果を見込むことが出来ない.また SRAM の動作特性を決

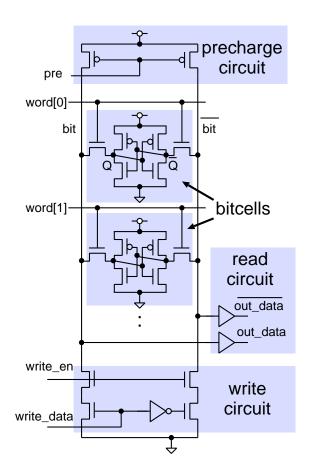

図 1: 一般的な 6T-SRAM 回路.

定するアクセストランジスタの特性を選択的に制御する事が出来ない.

本論文では,アクセストランジスタへの基板バイアス印加を行う事で特性を動的に制御する事で,低電圧動作に適する SRAM を実現する SRAM ビットセルについて提案する.Twin-Well CMOS 構造において選択的な基板バイアス印加を行うために,アクセストランジスタに PMOS を採用する.

論文の構成を以下に示す . 2 章において , 通常の  $\operatorname{SRAM}$  回路の動作の仕組みと , その低電圧化を克服する  $\operatorname{SRAM}$  ビットセルの提案を行う . 3 章において , 提案  $\operatorname{SRAM}$  ビットセルを利用する  $\operatorname{SRAM}$  回路の評価を行う . 4 章にて結論を述べる .

## 2 通常の6T-SRAMと提案SRAMの動作比較

## 2.1 通常の 6T-SRAM の動作と課題

本稿では,まず通常の  $\operatorname{SRAM}$  回路の動作について述べ,その上で提案する  $\operatorname{SRAM}$  ビットセルについて述べる.

図 1 に 、一般的に用いられている 6T-SRAM を示す . SRAM ビットセルが 2 つのビット線 (bit  $\overline{\text{bit}}$ ) を共有する構造となっている . 図の上部にはビットセルを充電するプリ

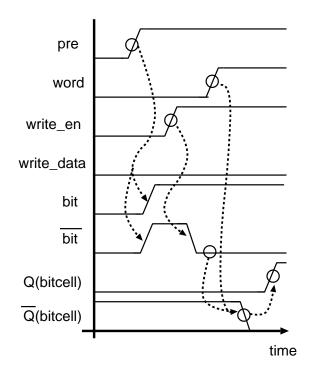

図 2: SRAM 回路の書き込み動作.

チャージ回路,下部にはビットセルに値を書き込むときに ビット線を放電する書き込みドライバ,およびビット線の 電位を判定する読み出し回路がある.読み出し回路は通常 はセンスアンプを利用するが,本稿では論理閾値電圧を変 更したスキュードインバータを想定する.

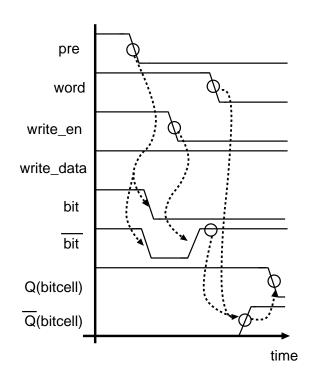

図 2 に,6T-SRAM の書き込み動作,図 3 に読み込み動作を示す.ビットセルの Q を "1" へ, $\overline{Q}$  を "0" へ書き込む.ビット線をプリチャージし,書き込むビット線(ここでは  $\overline{bit}$ )を選択し "0" まで放電する.この状態でセルを活性化すると,セルの  $\overline{Q}$  の電荷がビット線へ放電する. $\overline{Q}$  の放電がある程度進むと,Q の値を保持するインバータの値が反転し,Q が "1" ヘプルアップされる.

次に , 読み込み動作について説明する . "0" が書き込まれているビットセルの Q を読み出す . ビット線をプリチャージし , 読み出すビットセルを活性化する . ビットセルの Q が "0" なので , Q を保持するインバータがビット線 (bit) を放電する . ビット線の電位の低下を読み出し回路で判定し , Q もしくは  $\overline{Q}$  の値を読み出す .

SRAM 回路の動作速度はビットセルの値の読み出し動作に制約される.非活性な多数のビットセルがビット線に並列に接続されており,この寄生容量を小さなビットセルが放電するためである.大量に集積する必要があるビットセルはゲート幅の小さいトランジスタで構成する必要がある一方で,カラム毎に1つ用意すればよいプリチャージ回路,書き込みドライバ,読み出し回路はある程度大きいトランジスタを利用する事ができるため,書き込み動作は比較的

図 3: SRAM 回路の読み出し動作.

高速に実現できる.また非活性であるビットセルは単なる 負荷容量ではなく,各ビットセルが格納している値に依存 してビット線へ漏れ電流が発生する.従って活性化された ビットセルは,ビット線に溜まった電荷の放電だけでなく, 非活性ビットセルから漏れ出るリーク電流にも打ち勝つ必 要がある.

電源電圧の低下は集積回路のエネルギー効率を高める有効な手法であるが,一方でトランジスタのオン電流が減少する欠点がある.トランジスタのオン電流が減少するとビットセルの放電特性が悪化する.活性化するビットセルがビット線を放電する放電電流より,非活性ビットセルから流れ込むリーク電流が上回ると,SRAM 回路として正しく読み出し動作を行う事が出来なくなる.SRAM 回路が正しく読み出し動作を行う最低動作電圧は,トランジスタのオン電流とリーク電流,ビット線に接続するビットセルの並列数に依存する.

## 2.2 閾値電圧の動的制御による SRAM ビットセルの低電圧動作

本論文では、SRAM ビットセルの基板にバイアス電圧を印加する事で、SRAM ビットセル内のトランジスタの閾値電圧を制御する事で、SRAM 回路の低電圧安定動作を試みる、一般に利用される Twin-Well CMOS プロセスにおける 6T-SRAM 回路では、アクセストランジスタとして NMOS を利用するため、ビットセル事に基板バイアスを印加する事

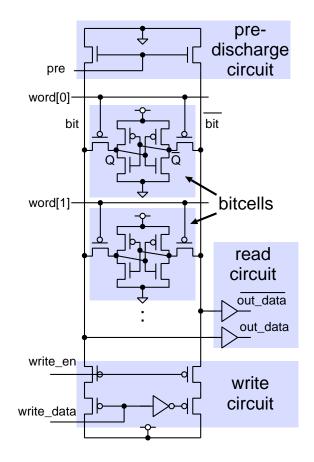

図 4: PMOS をアクセストランジスタとした提案 SRAM 回路 .

は難しい. Triple-Well 構造を利用する事で基板バイアスを 選択的に印加が可能になるが, Deep N-well 層を定義する ために追加マスクが必要となる.

この問題を解決するために,本論文では図 4 に示す,アクセストランジスタに PMOS を利用する SRAM を提案する.PMOS パストランジスタをアクセストランジスタとして利用するには,SRAM ビットセルの読み出し完了時にアクセストランジスタのゲートソース間電圧が PMOS の閾値電圧よりも十分低い必要がある.そのため NMOS を利用した場合とは反対に,ビットセルがビット線を "1" に充電する事で読み出し操作を完了するように回路動作を変更する必要がある.この変更に伴って,提案 SRAM は一般的な6T-SRAM の回路動作における電圧波形とは正反対の波形遷移を利用する事になる.そのため,プリチャージ回路の代わりにプリディスチャージ回路を用意し,読み出し回路における読み出し判定論理を反転させる.

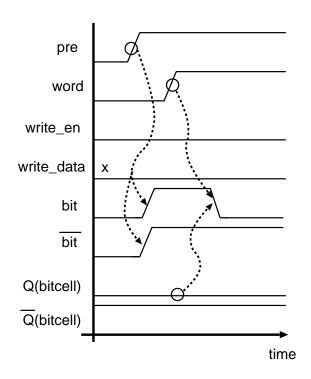

図 5 に , 提案 SRAM の書き込み動作 , 図 6 に読み込み動作を示す . ビットセルの Q を "0" へ ,  $\overline{Q}$  を "1" へ書き込む . ビット線を "0" ヘプリディスチャージし , 書き込むビット線 (ここでは  $\overline{bit}$ ) を選択し "1" まで充電する . この状態でセルを活性化すると , セルの  $\overline{Q}$  がビット線から充電される .

図 5: 提案 SRAM 回路の書き込み動作.

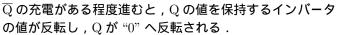

次に,読み込み動作について説明する."1" が書き込まれているビットセルの Q を読み出す.ビット線を "0" ヘプリディスチャージし,次に読み出すビットセルを活性化する.ビットセルの Q が "1" なので,Q を保持するインバータがビット線 (bit) を充電する.ビット線の電位の上昇を読み出し回路で判定し,Q もしくは  $\overline{Q}$  の値を読み出す.

このように , 前述した一般的な 6T-SRAM とは正反対の極性を持つ回路動作となる .

## 3 商用テクノロジを用いた SRAM 回路の設計 実験

本節では , 商用 65-nm CMOS プロセスを想定した SRAM 回路の設計実験を行う .

## 3.1 実験準備

商用 65-nm FDSOI CMOS プロセスを利用して設計実験を行った . SRAM ビットセルの作成にあたり , 回路設計は通常のロジックプロセスを利用した . 本プロセスの特徴として , ソース基板間電圧を 2.0~V まで印加可能である . SRAM 動作時において , 活性化セルの基板バイアス電圧を無バイアス状態に変更し , 一方で不活性化セルの PMOS トランジスタに対して選択的に逆バイアスを印加する事でリーク電流の削減を試みた . 本プロセスにおいて Nwell と Pwell で

図 6: 提案 SRAM 回路の読み出し動作.

は Well 間の最低間隔ルールが異なる.Nwell に比べ Pwell の方がより広い Well 間距離ルールが適用されており,ビットセルあたりの面積コストという観点でも提案  $\operatorname{SRAM}$  の方が有利な条件となっている.

## 3.2 評価する SRAM 回路および評価方法

アクセストランジスタの PMOS 化にあたり,3 種類の SRAM 回路を作成しその特性を評価した.1 つはアクセストランジスタに NMOS を利用した通常の 6T-SRAM である. Twin-Well 構造を想定し,基板バイアスの印加は考慮しない. 残りの 2 つはアクセストランジスタに PMOS を利用した SRAM である. ビットセルの配置方法が異なり,一方は 1 bit 単位で基板バイアスを印加可能とする SRAM であり (以下  $\overline{SRAM}$ ), もう一方は  $\overline{SRAM}$  ビットセルの実装密度を向上する一方で基板バイアスを 2 bit 単位で印加する SRAM である (以下  $\overline{SRAM2}$ ).

いずれの SRAM においても,2 対のビット線にビットセルを並列に 1024 セル接続する構造を採用した.ビットセルの比較を公平に行うために,3 種類のビットセルの回路設計時に,内包するゲート幅の総和を等しくする制約を加えた.各ビットセルが内包するトランジスタのゲート幅を表 1 に,ビットセルの面積を表 2 に示す.面積効率を示す 1 bit あたりの面積は,通常の SRAM と  $\overline{SRAM}$  はほぼ等しいが,1 bit 単位で基板バイアスを印加可能な  $\overline{SRAM}$  は 10%程度悪化している.

表 1: ビットセル中の各トランジスタゲート幅

|               | Conv. SRAM |           | P-type. SRAMs |           |

|---------------|------------|-----------|---------------|-----------|

|               | Type       | Width[nm] | Type          | Width[nm] |

| Access Tr.    | NMOS       | 280       | PMOS          | 280       |

| Pull-up Tr.   | PMOS       | 200       | PMOS          | 280       |

| Pull-down Tr. | NMOS       | 280       | NMOS          | 200       |

表 2: ビットセルの面積

| K =: = > 1 = 27 + 2 = K |            |               |              |  |

|-------------------------|------------|---------------|--------------|--|

|                         | Conv. SRAM | P-type. SRAMs |              |  |

|                         |            | SRAMB         | SRAMB2       |  |

| Cell width $[\mu m]$    | 1.52       | 1.52          | 1.52         |  |

| Cell height $[\mu m]$   | 1.32       | 1.5           | 2.56 (2 bit) |  |

| Area/bit $[\mu m^2]$    | 4.01       | 4.56          | 3.90         |  |

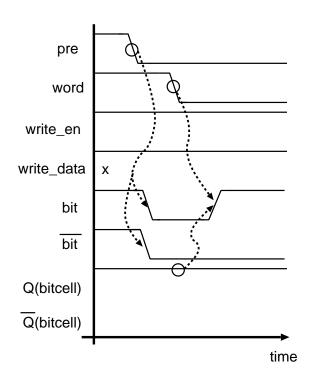

プリチャージ/プリディスチャージ回路,書き込み回路, 図 7: SRAM 回路の電源電圧と読み出し遅延の関係 (Typi-読み出し回路もレイアウト設計を行った.読み出し回路は, cal). -般的なセンスアンプを利用した方式ではなく,論理閾値 を変更したスキュードインバータとしている.ただし以下 の評価において,読み出し時の遅延の評価ではスキュード インバータではなく、ビット線の電位を評価している、提 案する SRAM ビットセルにおいて , 非活性セルに基板バイ アスを印加する事を前提にしているが,基板バイアス電圧 の印加方法については本論文では検討できていない. 今回 の評価においては,回路シミュレーションにおいて外部か ら静的にバイアス電圧を供給している.

3種類の SRAM 回路において SRAM ビットセルの違いに よる性能の違いを評価するために, SRAM ビットセル以外 の周辺回路の入出力容量がおおむね等しくなるように、ト ランジスタのサイズを等しくした、トランジスタの型の違 いによる駆動能力の変化が SRAM ビットセルの遅延特性に 反映されないように , 対象となる SRAM ビットセルの駆動 能力に依存する遅延変動を評価した.

前述したように, SRAM ビットセルからの読み出し速度 は、活性化したビットセルがビット線を駆動する能力と、 ビット線の負荷容量、そしてビット線の充放電に伴って非活 性ビットセルから漏れるリーク電流に依存する.リーク電 流は非活性ビットセルに格納されている値に依存するため、 非活性ビットセルの値を適切に設定する必要がある.通常 の SRAM の読み出し動作ではビット線に "1" をプリチャー ジしビットセルによって "0" へ放電するため, "1" が書き 込まれているビットセルからビット線を充電する様にリー ク電流が流れ込む.逆に,提案 SRAM は "0" をプリディス チャージしビットセルによって "1" へ充電するため, "0" が 書き込まれているビットセルからビット線の電荷を放電す る様にリーク電流が流れる.

ビットセルに起因する遅延を評価するために、読み出し 遅延と書き込み遅延を以下の様に定義した.読み出し遅延 は、プリチャージ後にワード線の電位が電源電圧の半分を 超えた点から,ビット線の電位が90%変動するまでの時間

と定義した.書き込み遅延は,プリチャージ後にワード線 の電位が電源電圧の半分を超えた点から,書き込むビット セル内部の値が目的の電位の90%になるまでの時間と定義 した.

トランジスタのオン電流,オフ電流共にトランジスタ特 性のばらつきの影響を受ける.今回の評価では,ばらつき を与える対象を SRAM ビットセルに限定した上で,2つの 条件の評価を行った.一つはばらつきを想定しない Typical 条件である、もう一つは、最も遅延特性が悪くなる条件と して,活性化ビットセルをSlowとし,非活性ビットセル のリーク電流が最大化する Fast コーナーを想定した条件で ある.

#### 3.3 評価結果

電源電圧 0.5 V, Typical 条件における, 各 SRAM 回路の 読み出し遅延および書き込み遅延を表3に示す.いずれの SRAM 回路においても , 読み出し遅延の方が書き込み遅延 よりも大きい.前述の通りビットセル内部のゲート幅の小さ いトランジスタがビットセルを駆動する必要があるためであ る.表からわかるように,アクセストランジスタをPMOS にした SRAM および SRAM2 は通常の SRAM に比べて読み出 し遅延が35%ほど遅い結果となった.

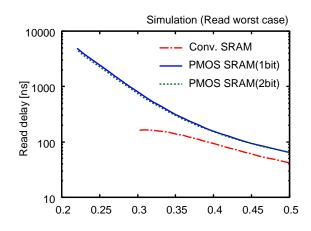

Typical 条件における最低動作電圧を評価した結果を図 7に示す、縦軸は対数である、通常のSRAM回路は全ての 領域で 20-30%ほど高速であるが , 0.25 V より低い領域で は読み出し動作ができない . 一方で提案 SRAM 回路はより 低電圧動作が可能であり,  $\overline{\mathtt{SRAM}}$  は  $0.19~\mathrm{V}$  まで,  $\overline{\mathtt{SRAM2}}$  は 0.18 V まで読み出し動作が可能であった . 各 SRAM 回路の 読み出し時および書き込み時の最低動作電圧を表4に示す.

SRAM 回路の読み出し動作が最も悪化するトランジスタ 条件における各 SRAM 回路の読み出し遅延および書き込み

表 3: 各 SRAM 回路の遅延 (0.5V).

|            | Read delay [ns] |       | Write delay [ns] |       |

|------------|-----------------|-------|------------------|-------|

| Circuit    | Typ.            | Worst | Typ.             | Worst |

| Conv. SRAM | 35.9            | 42.1  | 9.00             | 10.1  |

| SRAMB      | 49.6            | 64.5  | 18.6             | 18.3  |

| SRAMB2     | 50.5            | 64.8  | 15.0             | 14.5  |

表 4: 各 SRAM 回路の最低動作電圧.

|            | Min. read-op.[V] |       | Min. write-op.[V] |       |

|------------|------------------|-------|-------------------|-------|

| Circuit    | Typ.             | Worst | Typ.              | Worst |

| Conv. SRAM | 0.25             | 0.30  | 0.23              | 0.26  |

| SRAMB      | 0.19             | 0.22  | 0.15              | 0.15  |

| SRAMB2     | 0.18             | 0.22  | 0.15              | 0.15  |

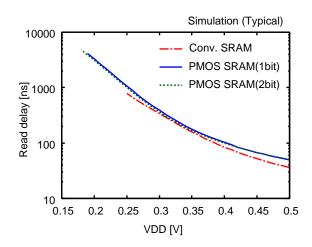

遅延を表 3 に示す .0.5 V 動作において通常の SRAM 回路では遅延が 13%増大し,提案する SRAM 回路では遅延が 30%増大した.電源電圧と各 SRAM 回路の読み出し速度の関係を図 8 に示す.通常の SRAM 回路に比べ,PMOS を アクセストランジスタとした提案 SRAM 回路は読み出し遅延が 50%から 100%大きく,Typical 条件に比べその差は大きい.

各 SRAM 回路の読み出し時および書き込み時の最低動作電圧を表 4 に示す.提案 SRAM 回路はトランジスタのワーストケースであっても最低動作電圧が低い事がわかった.通常 SRAM 回路の最低動作電圧が 0.3~V である事に対し, $\overline{SRAM}$  および  $\overline{SRAM2}$  は 0.22~V での動作が可能であった.

## 4 結論

本論文では,集積回路の低電圧動作のための,低電圧動 作 SRAM を構成するビットセルの構造について議論した. 非活性化セルのリーク電流を削減するために基板バイアス による閾値電圧の制御に注目し,細粒度基板バイアスによ るビットセル単位での閾値電圧制御を利用可能とするビッ トセルを提案した. Twin-well 構造で各アクセストランジス タの閾値電圧を個別に制御するために,アクセストランジ スタに PMOS トランジスタを採用し,そのために回路構造 全体を一般的な 6T-SRAM とは異なる構造を採用した.提 案する SRAM ビットセルは PMOS トランジスタを採用し たことから一般的な SRAM よりも動作速度が遅いが, 基板 バイアスによる閾値電圧の制御によって最低動作電圧を下 げる.65-nm FDSOI プロセスにおける設計実験において, 1 bit 単位で基板バイアスの制御が可能な SRAM , 2 bit 単位 での基板バイアス制御とする代わりに面積効率の高い SRAM2 の 2 種類の SRAM ビットセルを提案し, 一般的な SRAM と比較を行った.実験の結果, Typical 条件において通常の SRAM の最低動作電圧が 0.23 V であった事に対し , 提案す る SRAM の最低動作電圧として, SRAM が 0.19 V, SRAM2 が 0.18 V を達成する事が出来た.

今後の課題として,基板バイアスの印加方法,基板バイ

図 8: SRAM 回路の電源電圧と読み出し遅延の関係 (ワーストケース).

アス電圧の生成および分配制御方法についての検討が挙げられる.

## 謝辞

設計実験は,東京大学大規模集積システム設計教育研究 センターを通し、シノプシス株式会社,日本ケイデンス株 式会社,メンター株式会社の協力で行われた.

## 参考文献

- [1] R. Kumar and G. Hinton, "A Family of 45nm IA Processors," in *International Solid-State Circuits Conference (ISSCC)*, 2009, pp. 58–59.

- [2] K. Ishibashi, K. I. Takasugi, T. Yamanaka, T. Hashimoto, and K. Sasaki, "A 1-V TFT-Load SRAM Using a Two-Step Word-Voltage Method," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 11, pp. 1519–1524, 1992.

- [3] Y. H. Chen, W. M. Chan, W. C. Wu, H. J. Liao, K. H. Pan, J. J. Liaw, T. H. Chung, Q. Li, C. Y. Lin, M. C. Chiang, S. Y. Wu, and J. Chang, "A 16 nm 128 Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-VMIN applications," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 1, pp. 170–177, 2015.

- [4] E. Karl, Y. Wang, Y. G. Ng, Z. Guo, F. Hamzaoglu, M. Meterelliyoz, J. Keane, U. Bhattacharya, K. Zhang, K. Mistry, and M. Bohr, "A 4.6 GHz 162 Mb SRAM design in 22 nm tri-gate CMOS technology with integrated read and write assist circuitry," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 1, pp. 150–158, 2013.

- [5] O. Hirabayashi, A. Kawasumi, A. Suzuki, Y. Takeyama, K. Kushida, T. Sasaki, A. Katayama, G. Fukano, Y. Fujimura, T. Nakazato, Y. Shizuki, N. Kushiyama, and T. Yabe, "A process-variationtolerant dual-power-supply SRAM with 0.179um2 Cell in 40nm CMOS using level-programmable wordline driver," pp. 458-460, 2009

- [6] T. Song, W. Rim, J. Jung, G. Yang, J. Park, S. Park, K. H. Baek, S. Baek, S. K. Oh, J. Jung, S. Kim, G. Kim, J. Kim, Y. Lee, K. S. Kim, S. P. Sim, J. S. Yoon, and K. M. Choi, "13.2 A 14nm Fin-FET 128Mb 6T SRAM with VMIN-enhancement techniques for low-power applications," Digest of Technical Papers IEEE International Solid-State Circuits Conference, vol. 57, pp. 232–233, 2014.

- [7] M. Yamaoka and T. Kawahara, "Operating-margin-improved SRAM with column-at-a-time body-bias control technique," in *European Solid-State Circuit Research Conference (ESSCIRC)*, 2007, pp. 396–399.