# 1 アクセラレータ技術の影と光 ーペタ〜エクサの次世代 HPC の 中心的な躍進技術へ

松岡 聡 (東京工業大学)

## はじめに—HPC (高性能科学技術計算)のコモディティ化とアクセラレーション

Cell<sup>1)</sup>, GPU<sup>2)</sup>, ClearSpeed<sup>3)</sup>, MDGRAPE<sup>4)</sup> などの アクセラレータ技術が昨今注目を浴びている. コンピュ ータシステムにおけるアクセラレーション自体は特に目 新しいことではなく、マルチメディア処理やグラフィク ス、I/O やネットワーク、暗号処理などを通常の CPU の外部の特殊ハードウェアや専用プロセッサで行うこと は普通であった。しかしながら、昨今のアクセラレータ への注目は、それが汎用のプロセッサとして高度な科学 技術計算や、それらに類した一般のアプリケーションに おける高負荷な処理―ビデオ圧縮・リアルタイム画像処 理・ゲームにおける物理計算―などへ広く安価に適用で きるところにある。それぞれのアクセラレータの内容は 参考文献や本特集の他稿に詳しいが、ここでは過去より 汎用アクセラレータの隆盛を繰り返してきた高性能計算 (HPC)・スパコンに着目し、そこからアクセラレータ の歴史・位置づけ・今後に関して述べてみよう.

いわゆるコモディティ技術による高性能 PC プロセ ッサや PC クラスタはスパコンに代表される HPC (高 性能科学技術計算)の世界を革命的かつ根本的に一新し た. 現在では広く用いられている x86 系のプロセッサは, 1980 年代初頭の 8086/8087 の登場時からすでに倍精度の 浮動小数点演算をハードウェアでサポートしていた。こ れは、当時のトランジスタ規模、および前進の8ビット 系の CPU が整数除算もサポートしていなかったことを 考えれば画期的なことであった。初期は Cray に代表さ れる当時のスパコンであるベクトル計算機と比較してそ の性能は微々たるものであったが、マルチメディアや小 規模の科学技術計算のニーズに押されその性能は急速に 向上し、1995年に登場した Pentium Proでは、高度な パイプライン化により毎クロックごとの演算が可能とな り、150MFlops を達成した。また、ネットワークやソフ トウェアの進化により高性能 PC を汎用高速 LAN で結 合した PC クラスタとしての並列計算機の構築も可能に

なり、その高いコストパフォーマンスによって 1994 年の最初の「Beowulf 型」の PC クラスタ (Wigraf) の登場から十数年、ハード・ソフトウェア技術の進歩によってそのサイズ・台数共に急激に増加し、裾野が広がるとともに、数万 CPU のマシンが構築されるようになった。我が国では大規模 PC クラスタである東工大 TSUBAME<sup>5)</sup>が 2006 年 6 月に地球シミュレータを押さえ我が国トップのスパコンとなり、その地位を 2 年間維持した。また、2008 年 6 月の Top500 においてはついに IBM Cellと AMD Opteron の混合型のクラスタ計算機である米国 LANL/IBM のスパコン Roadrunner が、クラスタ計算機としてははじめて世界一となって、同時にはじめて性能値でペタ(10 の 15 乗)フロップスの「壁」を破った。

PC クラスタにより HPC はメインストリーム化・大 衆化し従来はスパコンでしか実行可能でなかったアプリ ケーションが、ある程度の規模までならば PC ワークス テーションなどで実行可能となり、従来のスパコンと 比較して抜群なコストパフォーマンスの向上をもたら し、大規模なスパコンも同様に構築されるようになって、 「デスクトップからスパコンまで」のソフトウェアや利用 環境の共通化が果たされた。つまり、スパコンが PC テ クノロジの世界的なエコシステムの一部として相互の技 術転用を実現することが、HPC の世界を急速にメイン ストリーム化し、その発展における中心的な原動力とな っている。これがユーザ層を広げるだけでなく、従来 にはなかったより多くのアプリケーション分野―ビジネ ス分野からゲーム・エンタテインメントまで幅広く―へ の広がりをもたらした。たとえば、今や多くの映画製 作で不可欠な実写と見まごう 3DCG が可能となったの は、数百台~数千台並列のレンダリング用 PC クラスタ の構築が容易になったからである。 TSUBAME におい ても、昨日パソコンで動いていたアプリユーザが、今日 1.000CPU 規模でアプリを動かしている例も枚挙にいと まがない.

しかしながら、2008 年現在においても、IBM, Cray, NEC, 富士通など各社から、専用設計のスパコンが売ら

れているのも事実であり、日米において後継機種の研究 開発が続いている。コモディティのコストパフォーマン スからすれば、それら「恐竜」はとっくに絶滅しても良い はずだが、専用スパコンが存在し得るのは、それらが以 下のような PC-HPC 技術の欠点のニッチを埋めている からである。

(1) **高性能・高効率なベクトル処理**: x86 プロセッサの 性能向上は著しく、SSE や AltiVec, AVX など SIMD ベクトル命令も備わっているが、単一スレッドの処理能 力では、多くの場合これらの専用設計のプロセッサには かなわない。これはベクトル並列性が専用プロセッサの 8~16に比べてたかだか2~4程度しかないこと、メ モリアクセスのバンド幅やランダムアクセス性が弱いこ と、などに起因する。過去には CPU クロックの持続的 な上昇で単一スレッドの性能が高まり, 専用設計に急速 に追いついたが、消費電力や発熱の問題で2005年あた りを境に急速に止まり、今ではそれが困難になった。無 論, 通常は OpenMP や MPI などで中~粗粒度の並列性 を高めることによって専用プロセッサの性能を大幅に上 回ることが多々あるが、それにも限界がある。たとえば 計算中の主要アルゴリズムなどで、中~粗粒度レベルの 逐次計算の必要性や、あるいはグローバルメモリアクセ スのレーテンシに起因するボトルネックが発生すると, アムダールの法則によって性能が上げられず, 数倍の性 能差が本質的に生じてしまう.

(2) 電力・設置・メンテナンス効率の問題:PCクラスタによっては効率が出にくいアプリケーションの性能を並列性でカバーしても、それによる電力・スペース・メンテナンス、最終的にはコストの大幅な増加が問題となってくる。多くの大規模スパコンの電力消費量は数百 KW から数 MW に達し、次世代ではさらに最大で数十 MW に達すると目されている。小規模なマシンでも、電力は言うにおよばず、冷却・騒音・重量などの設置性や、サイズと反比例して低下するシステムの故障率が大きな問題となる。つまり、あるアプリケーションの実行に際して、同じ性能が得られるのならば、なるべく計算機としてはコンポーネンツの数や物理的なサイズの面で小さく、かつ効率が良いことが好ましい。それらの点で、専用設計のスパコンが有利になる場合においてはニッチとして存在し得る。

上記のような汎用コモディティプロセッサの欠点を 大幅に是正し、専用設計のスパコン並み、あるいはそ れを上回る性能を発揮するのが汎用技術をベースとし た現代のアクセラレータである。今後のペタスケール から 2019 年ごろのエクサ (10 の 18 乗) へのトップエンドスパコンの性能向上から、ボトムエンドの PC レベルでの通常の CPU では効率の悪いビデオ編集などのアプリケーションの加速まで、多くの期待がなされており、研究開発が盛んに行われている。ちなみに、前述のTSUBAME、Roadrunner とも、Top500 においてはじめてアクセラレータを搭載した 2 台であることは、今後のHPC のトレンドを占う上で重要である。しかし、先にも述べたように、HPC においても汎用処理用のアクセラレータは過去より存在し、必ずしも成功したとは言い難い。それらと比較して、現代のアクセラレータはどのように違い、なぜ成功を期待されているのか、次に論じることにしよう。

### HPC におけるアクセラレータの影と光

HPC向けのアクセラレータ技術は古くから存在し、古くはメインフレームやミニコンの「科学技術演算用オプション」としても売られていた。近代スパコンでも Thinking Machine 社の CM-5 や富士通 AP1000 などに 採用されていた Weitek 社製のベクトルアクセラレータ など、いくつもの試みがあった。しかしながら、それらは広く受け入れられることなく、場合によってはメーカ 自身を含み消滅してしまった。これにより、HPC 業界全体で、CPU 自身の高速化がメインストリームになり、アクセラレータはかなり穿った目で見られてきたことも 事実である。

しかしながら、現在は HPC においてアクセラレータが注目技術として脚光を浴びており、同じような理由で通常の PC や携帯などにおけるコンピューティングでも、グラフィクスなど特定用途以外の一般アプリへの適用が着目されている。これはなぜなのであろうか;つまり、過去の暗黒時代とどのように違うのであろうか。これらの技術的な点のみならず、HPC やアクセラレータを取り巻く社会環境までつまびらかにすることにより、今後のアクセラレータの成功を強く確信することが可能となる。

まずは、過去と異なりアクセラレータが PC ベースのコモディティのエコシステムの一部として開発・設計がなされていることにある。MDGRAPE、ClearSpeedなども、そのホストとなるプラットフォームは PC であり、PCI-Express などの高速 I/O に接続し、主に PC 上でプログラムを開発しその HPC アプリケーションを加速するようになっている。Cell や GPU はさらにそもそもの生い立ちが PC や組込み系のコモディティ環境のグラフィクスやマルチメディアの加速が目的であり、当然 PC やゲーム機器を中心としたハードウェアや開発環境が安価に存在する。このように PC エコシステムの一部とな

ることにより、その低価格により容易に一般利用が可能となり、結果としてアクセラレータの HPC アプリケーション開発や利用技術の発展が加速し、普及につながるという、自らのエコシステム維持が今回は可能でありそうなことがアクセラレータが再び脚光を浴びている大きな理由である

次に、過去には通常の CPU がすぐにアクセラレータ に性能的に追いついてしまい、その存在理由を希薄に していたが、現在では前章の(1)で述べた通り、現代の CPU はクロック上昇による性能向上が 2005 年ごろに終 焉し、その後マルチコア化により性能向上を維持してい るが out-of-order 実行などのために多くのトランジスタ を演算以外の部分に費やしており、また過去との命令体 系の互換性の維持のために、そのトランジスタ数の増加 に比例した性能向上を得られなくなっている. また, 多 くの HPC アプリで重要なメモリバンド幅の不足もさま ざまな理由で深刻となっているが、レガシーを多く含む 一般的なアプリの万遍ない速度向上にはキャッシュの増 量以外の決定打がなく、さらに演算回路が利用できるチ ップ面積を圧迫している. 現状で, 250mm~300mm 程度のチップ面積において線幅 45nm で作られるメイン ストリームの x86 系の CPU の場合, SIMD 演算をフル に駆使しても、倍精度では 50GFlops 程度以下、単精度 では 100GFlops 程度以下である.

これらに対し、現代のアクセラレータはアプリケーションの適用範囲を絞り、かつレガシーに縛られないことによって、ベクトル・SIMD・マルチスレッド演算処理よりはるかに高い演算密度を得ている。Cell/B.E. は単精度で 256GFlops、倍精度演算が改良された PowerXCell 8i では 102.8GFlops のピーク性能である。ClearSpeed も初期よりボードあたり倍精度 80~96GFlops に達している。MDGRAPE は単精度 200GFlops の性能によって、理研の初の分子動力学用ペタフロップスシステム「MDGRAPE-3」の中心的な演算装置となった。GPU のピーク演算性能はさらに高く、2008 年末の最新の NVIDIA の Tesla T10 GPU、AMD の FireStream GPU とも単精度では 1 TFlop 以上を可能としており、倍精度の性能も急速に向上しつつある。

また、メモリバンド幅も Cell、GPU は CPU と比較して高い。Cell/B.E. は 2006 年に XDR メモリを用い25.6GB/s を実現し、当時の PC と比較して約 4 倍のメモリバンド幅を可能とした。PC がこのレベルまで追いついたのは 2 年以上後の 2008 年末の Intel Nehalemにおいてであり、しかもトップエンドの高性能モデルに限られる。GPU はさらにメモリバンド幅が高く、Graphics 用の GDDR メモリの point-to-point 接続を利用して、少ないチャネル数で高いバンド幅を実現してお

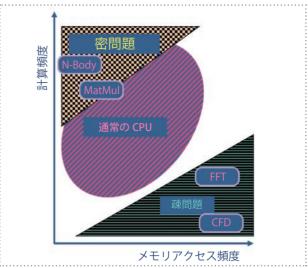

図 -1 CPU とアクセラレータにおける計算頻度とメモリアクセス 頻度の関係

り、その性能は 100GB/s を超え、NEC SX-9 などの最新の専用ベクトル計算機に匹敵する.

以上をまとめると、図-1のようになる。ここでは X 軸は要求される単位時間あたりの計算回数、Y軸は要 求される単位時間あたりのメモリアクセスの回数を示 す。この中でそれぞれのアプリケーションはこのグラ フのどこかにプロットされる。HPC アプリケーション は当然高性能であることが求められるので、グラフ上 で右方向・上方向に位置するが、その中でも N-Body や BLAS に代表される密結合系の問題の計算カーネル と,流体力学(CFD)やFFTに代表される,高いメモリ バンド幅を要求するものに大別され, 前者は左上に, 後 者は右下に位置する。この中で、特に右下は旧来型のべ クトル計算機が得意とするものであった。一方、通常の CPU が得意とする通常の汎用アプリケーションは、左 下から右上の(加速が必要ない)エリアに位置する. 今回 取り上げるアクセラレータは、多くの並列演算ユニット を密にチップに内包し、すべて左上の密結合系の問題の 計算カーネルを得意とする。さらに、Cell, GPU は、右 下の高メモリバンド幅系の HPC アプリケーションも同 時に得意とする.一方 MDGRAPE, ClearSpeed はこの 領域は不得意だが、その代わり性能に対する消費電力が 相対的に低い、などの有利さがある。全体的に HPC で 重要な領域がカバーされ,先の(1),(2)の専用スパコ ンの存在を意味あるものにたらしめていた領域までも汎 用技術でカバーするのが、現代のアクセラレータの過去 との大きな違いなのである.

このように、汎用技術に基づき、PC やゲームなどの エコシステムを活用して大幅なコストダウンを果たし、 広い普及を可能にしただけでなく、その性能面において CPU が不得意であった多くの HPC のアプリケーショ

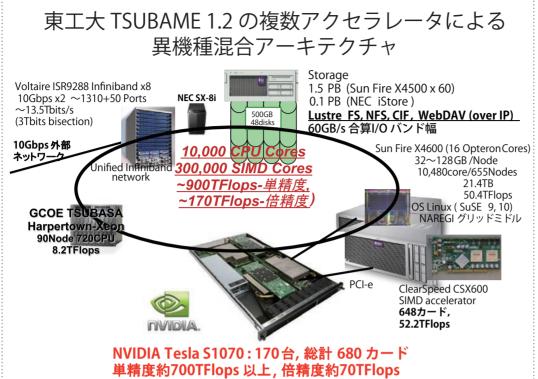

図-2 TSUBAME1.2 におけるアクセラレータの追加

ン領域をカバーし、HPCの将来に対して大いなる可能性を示している。しかし、真の普及のためには、越えなければいけない大きなハードルがある。それがアクセラレータに適したアルゴリズムと、その開発を支えるソフトウェア技術や環境の進歩である。

### アクセラレータ技術の問題点と今後の展望:アルゴリズムとソフトウェア

2008 年 10 月に、東工大において TSUBAME をホストマシンとして、「高速フーリエ変換演算加速装置」と銘打って図-2,3 のように 170 台の NVIDIA Tesla S1070 が配備された。従来のスパコンとしての TSUBAME の 10,480 コアの AMD Opteron CPU、従来からの合計 648 枚の ClearSpeed アクセラレータに加え、合算した性能は倍精度演算は約 170TFlops、単精度性能は約 900TFlops 近くに達し、その Linpack 性能は 77.48TFlops に達した。これは、Opteron のみの性能である、倍精度のピーク性能約 50TFlops、Linpack 38.18TFlops を大きく上回る。しかも、それらの設置面積は大変少ないもので(図-3)、かつ消費電力も TSUBAME 全体の  $1/8 \sim 1/10$  程度である。

しかしながら、アクセラレータで性能を達成するのは 容易ではなく、x86 の通常の CPU (Opteron + 一部 Intel Xeon)、ClearSpeed、Tesla を複合した異機種環境におい て Linpack を効率よく動作させるには、負荷分散におい

て我々の過去の異機種分散環境における高性能 Linpack の研究 <sup>6)</sup> をさらに発展させた緻密なアルゴリズム設計を 必要とした。高メモリバンド幅の3次元FFTカーネル においても、Tesla GPU は TSUBAME の1ノード・ 16CPU (Opteron 2.4Ghz) における最適化ライブラリ の性能 (20GFlops) の 7 倍の 140GFlops の性能を示す <sup>7)</sup>. しかしながら、この性能もベクトル計算機用の FFT の アルゴリズムである Multi-Row FFT をベースとしなが ら、並列化や転置の際のメモリレイアウトや順番の工夫 など、細心の注意を払って得られた結果である。このよ うに、アクセラレータはその性質上性能がピーキーで あり、最高性能を得るためのアルゴリズムの開発負荷が 大きい。その負荷をなるべく減らすには、並列記述を容 易にするプログラム言語,性能プロファイリングおよび モデリング技術、並列化をサポートするコンパイラ技術、 ランタイム時の自動チューニングを伴う自動最適化技術, 並列デバッグ技術、さらにはアクセラレータにチューニ ングされた種々のライブラリ群など、種々の研究と、実 用的なシステムを構築するための開発が必要である.

近年では、これらの課題を解決するために、すでにいくつかの研究開発が行われている。GPU においては、プログラム言語は初期は Brook や PeakStream などストリーム型の言語が中心であったが、NVIDIA 社のマルチスレッド型の言語の CUDA の成功に伴い、アルゴリズムやアプリケーションの開発が大幅に進みつつある。さらに、CUDA をベースに、AMD Firestream や Intel

図 -3 TSUBAME への NVIDIA Tesla S1070 の追加. それぞれの S1070 には Tesla 10p プロセッサカードが 4 枚内蔵されている. TSUBAME の計算ノード間にS1070 を挿入し、PCI-Express の拡張ケーブルで計算ノードに接続する. 挿入後もほとんど目立たず、アクセラレータの高い計算密度を示している(写真は筆者).

Larrabee など、他のアクセラレータでもポータビリティが確保されるために、OpenGL の標準化を行っている Khoros グループが中心となって標準言語 OpenCL の規格制定と処理系開発が進んでいる.

我々も, 東工大・学術国際情報センターを中心とし て、他の大学や企業と HPC における研究開発プロジ ェクトを進めている. JST の戦略的創造研究推進事業 (CREST) における「ULP-HPC: 次世代テクノロジのモ デル化・最適化による超低消費電力ハイパフォーマンス コンピューティング」では、今後10年間で電力性能比を 1000 倍向上させることを目標に、複数の大学の研究グ ループが合同で研究を行っているが、アクセラレータに よる電力性能比の向上が目標達成に大いに寄与する。こ こでは割愛するが、その中でさまざまなソフトウェア研 究が行われており、また流体アプリケーションにおける 加速と省電力化は、本特集の青木氏らの稿に詳しい。ま た, Microsoft Research との共同研究では, 東工大の秋 山泰教授と合同で、全対全のたんぱく質問のドッキング を GPU で大幅に加速する研究を行っているが、長時間 の大規模計算を実現するために、GPU 計算の高信頼化 アルゴリズムの開発を進めている.

しかしながら、汎用アクセラレータの HPC, さらには一般アプリケーションにおけるメインストリーム化のための研究開発は緒についたばかりである。本特集が参考になって、HPC のメインストリーム化、それによりさらに一般のアプリケーションに今までなかった質的な

違いがもたらされれば大変に幸いである.

#### 参考文献

- 1) Cell Broadband Engine Technology and Systems, IBM Systems Journal, 51-5 (May 2007).

- Owens, J. D., Houston, M., Luebke, D., Green, S., Stone, J. E. and Phillips, J. C.: GPU Computing, Proc. IEEE, 96-5, pp.879-899 (May 2008).

- 3) ClearSpeed Technology Inc.: ClearSpeed Whitepaper: CSX Processor Architecture, http://www.clearspeed.com/docs/resources/ClearSpeed\_Architecture\_Whitepaper\_Feb07v2.pdf (Feb. 2007).

- 4) Taiji, M.: MDGRAPE-3 chip: A 165 Gflops Application Specific LSI for Molecular Dynamics Simulations, Proc. Hot Chips 16, IEEE Computer Society Press (CD-ROM) (2004).

- 5) Matsuoka, S.: Petascale Computing Algorithms and Applications ---Chapter 14 The Road to TSUBAME and Beyond, Chapman & Hall CRC Computational Science Series, pp.289-310 (2008).

- 6) Endo, T. and Matsuoka, S.: Massive Supercomputing Coping with Heterogeneity of Modern Accelerators, IEEE International Parallel & Distributed Processing Symposium (IPDPS 2008), the IEEE Press (Apr. 2008).

- 7) Nukada, A., Ogata, Y., Endo, T. and Matsuoka, S.: Bandwidth Intensive 3-D FFT kernel for GPUs using CUDA, Proc. ACM/IEEE Supercomputing 2008 (SC2008), Austin, Texas, the IEEE Press (Nov. 2008)

(平成 21 年 1 月 16 日受付)

#### 松岡 聡(正会員)

matsu@is.titech.ac.jp

1986 年東京大学理学部情報科学科卒業。東大・東工大教員を経て 2001 年東京工業大学学術国際情報センター教授。博士(理学,東京大学大学院)。高性能システム,並列処理,グリッド,クラスタ計算機,HPC の省電力化や加速,大規模データ処理,等の研究に従事。NAREGI プロジェクト・情報爆発特定科研のサブリーダー,2006 年我が国最高性能のスパコン TSUBAME を構築。1999 年本会坂井記念賞、2006 年学術振興会賞受賞。2009 年 ACM/IEEE Supercomputing '09 の論文委員長。