# 高性能プロセッサモデルにおけるアーキテクチャと OS の協調

4D - 03

河原 章二 中條 拓伯 並木美太郎 東京農工大学工学部情報コミュニケーション工学科

### 1 はじめに

近年の VLSI 技術は、1つのチップに数千万というオーダのトランジスタの実装を可能にし、それに合わせてプロセッサの性能も向上してきた。特に現在主流のスーパスカラプロセッサアーキテクチャは、命令ウィンドを増やし、またチップ上のキャッシュを拡大することで性能を上げてきた。しかし現在、その性能向上には陰りが見え始めている。その要因として単一の命令流(スレッド)に、現行のスーパスカラプロセッサが抽出できる命令レベル並列性(ILP)がさほど存在しないというのが挙げられる。

このような中、Simultaneous Multithreading (SMT) [2] アーキテクチャが注目されている. SMT は 1 つのチップに複数のスレッドを保持し、それらを同時に実行することで性能向上を得る.

SMT の提案は現在までにいくつかあるが、一方で SMT プロセッサを考慮したオペレーティングシステム (OS) は未だ提案されていない、本論文では、現状のプロセッサモデルのまとめを行なうとともに、SMT プロセッサ上において、どのような OS のモデルが望ましいか、またどのような課題があるかを議論する、それとともに、OS の実装を目標とした SMT プロセッサのモデルについても議論する。

### 2 現状のプロセッサモデル

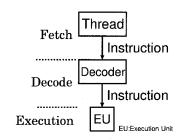

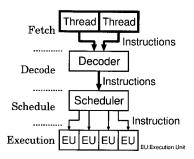

現在のプロセッサは、パイプラインプロセッサをベースにしてそこからいくつかのプロセッサモデルに派生している.まず、ベースとなるパイプラインプロセッサの簡単なモデルを図1に示す.

図 1: パイプラインプロセッサのモデル

ここでスレッドとは1つの命令流を指す. 図中の左の単語, Fetch, Decode, Execution はパイプラインステージを示している. また, 矢印は命令の流れを示

<sup>†</sup>Cooperation between Operating System and Architecture Based on High Performance Processor Model

Shoji Kawahara (shoji@nj.cs.tuat.ac.jp) Hironori Nakajo (nakajo@cc.tuat.ac.jp)

Mitaro Namiki (namiki@cc.tuat.ac.jp)

Department of Computer, Information and Communication Sciences, Tokyo University of Agriculture and Technology している。そして EU は Execution Unit の略であり、 ALU などの実行ユニットを意味する。

パイプラインプロセッサにおいて,命令は1つのスレッドから1命令フェッチされ,その命令はデコードユニットを介して実行ユニットに送られる.これがベースとなるパイプラインプロセッサの基本的なモデルである.

# 2.1 スーパスカラプロセッサ

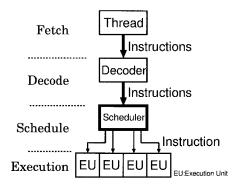

スーパスカラプロセッサとは、1つのスレッドから 複数の命令をフェッチし、もし同時実行できる命令(依 存関係が無い)があれば、1サイクル中にそれらを実 行するプロセッサのことである。図2に簡単なモデル を示す。

図 2: スーパスカラプロセッサのモデル

同時実行(並列実行)できる命令はハードウェアが 抽出しそれらを実行する.並列実行可能な命令を抽出, スケジューリングするのが図中のスケジューラの役目 である.このために,新たにスケジューリングのため のパイプラインサイクルが追加される.現在,一般的 に最も普及しているプロセッサモデルである.

### 2.2 VLIW プロセッサ

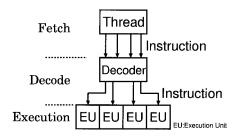

VLIW (Very Long Instruction Word) プロセッサとは、コンパイラ (ユーザ) が並列実行可能な命令をあらかじめ指定しておき、プロセッサは既にコンパイラによってスケジューリングされた命令を並列に実行する. 図 3 に VLIW プロセッサのモデルを示す.

スーパスカラプロセッサは動的、つまりハードウェアが並列実行可能な命令を抽出して実行するのに対し、VLIW は静的にスケジューリングされた命令を実行する。よって、スーパスカラプロセッサのようなスケジューリングのためのハードウェアは必要ない。このため、スーパスカラプロセッサと比べてハードウェアが複雑にならずにすむ。現在、VLIW は DSP などの、静的にスケジューリングしやすい定型処理をターゲットにしたプロセッサに採用されている。

図 3: VLIW プロセッサのモデル

### 2.3 オンチップマルチプロセッサ

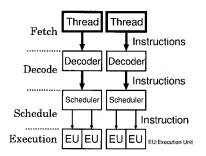

オンチップマルチプロセッサ (CMP) は,1つのチップに複数のプロセッシングエレメント (PE) を実装したプロセッサモデルである.図4にCMPのモデルを示す.

図 4. オンチップマルチプロセッサのモデル

CMP が今まで挙げてきたプロセッサモデルと異なるところは、複数のスレッドを1つのプロセッサで扱える点にある。このようなプロセッサアーキテクチャを、オンチップマルチスレッドアーキテクチャという。 図 4 では各 PE はスーパスカラプロセッサになっているが、これは普通のパイプラインプロセッサでも、または VLIW プロセッサでも構わない。また、図では VLIW プロセッサでも構わない。また、図では 2つだが、更に 4 つであっても構わない。重要なことは複数の PE が 1 つのチップに実装されている点にある。複数のスレッドから命をフェッドを1 であるにある。複数のスレッドがら物数スレッド実行を可能にしている。これは従来のマルチプロセッサを1 つのチップで実現したものといえる。これにより、従来のシングルスレッドをターゲットにしたプロセッサモデルに比べ、より高い性能向上が得られる。

# 2.4 SMT プロセッサ

SMT プロセッサは複数のスレッドからフェッチして きた命令を1つのパイプラインに流し, 同時に実行するプロセッサモデルである. 図5に SMT プロセッサのモデルを示す.

CMP, SMT プロセッサはともにオンチップマルチスレッドアーキテクチャであるが, 両者の違いは CMPはハードウェアが PE 単位で区切られているのに対し, SMT は 1 つのハードウェアリソースを複数のスレッ

図 5: SMT プロセッサのモデル

ドで共有している点にある.このため、SMT プロセッサは CMP と比べてハードウェアリソースを無駄なく活用できる.

# 2.5 プロセッサの命令実行状態

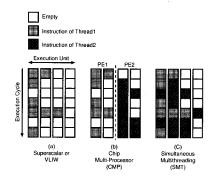

上述した各プロセッサモデルの命令実行状態のまとめを図 6 に示す.

図 6: 各プロセッサモデルの命令実行状態

図の四角1つ1つが実行ユニットを意味し、横が実行ユニットの総数、縦が実行サイクルの流れを意味する。例えば(a)の1番上の段が意味するものは、このプロセッサは1サイクル中に最大4つの命令を同時に実行でき、1サイクル目でスレッド1の2つの命令がプロセッサの実行ユニット(Execution Unit)によって実行される、ということである。全サイクルを通した実行命令数が、即ちそのプロセッサの性能の指標といえる。

図 6 の (a) はスーパスカラプロセッサと VLIW プロセッサの命令実行状態である. 両プロセッサは,全サイクルを通して1つのスレッドからフェッチしてきた命令を実行する. よって,1サイクル中に1命令しか実行できない時もあれば,キャッシュミスなどのプロセッサのストールにより,全く命令を実行できないサイクルも存在する.

(b) は CMP の実行状態を示しており, 各 PE が それぞれ別のスレッドを実行することにより, (a) よりも実行ユニットの稼働率が改善されるのが分かる.

そして(c)はSMTの実行状態を表しており、CMP

と違い、1つのプロセッサ (CMP における PE) を複数 のスレッドが共有しているのが分かる。複数のスレッ ドからフェッチしてきた命令群を一緒にスケジューリ ングすることにより、CMP と比べてより効率的にハー ドウェアリソースを使用できる。

# 3 SMT プロセッサ

ここでは SMT プロセッサの概要について述べる. 前節では SMT プロセッサの簡単なモデルについて述べたが,ここでは SMT プロセッサの具体的な形態を示す.

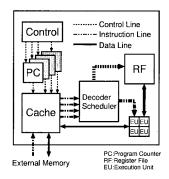

図7にSMTプロセッサ内部の概略を示す.

図 7: SMT プロセッサの概要図

SMT プロセッサは、チップ内に複数のプログラムカウンタ(PC)を保持し、それらを制御することで複数スレッドの実行を可能にしている。その他のハードウェアリソース、例えば実行ユニットは全てのスレッドが共有する。このようにスレッド制御ユニットなどのわずかなコストで、SMT プロセッサは複数スレッド実行の性能向上のみならず、ハードウェアリソースを有効に利用することが可能になる。しかし、SMTプロセッサは従来のスーパスカラプロセッサの機能を拡張したものであり、スーパスカラプロセッサが本来持っている、ハードウェアの複雑さの問題[1]をより増大させる恐れがある。

現在, Intel が HyperThreading という SMT アーキテクチャを用いたプロセッサを商用化しつつある [3]. このプロセッサは, 論理的に 2 つ PE が結合した SMP (Symmetric Multi-Processor) として動作する. これは提案初期の SMT[2] のアーキテクチャに近く, 比較的簡単なハードウェアロジックの付加により, 性能向上が得られる.

研究レベルでは、1つのプログラムを複数のスレッドに並列化させ、それらを SMT プロセッサで実行するという手法が模索されている。この複数スレッドの実行はプロセッサに新たなパラダイムを与える。単純な並列化の場合、サブルーチンコールやループのイタレーションを全てスレッドに変換し、並列実行させるという手法が挙げられる [4]. また、分岐命令が現れた時に Taken、Not Taken の両方のパスを実行することも可能である [5]. さらに、単なるプログラムの並列化だけでなく、通常のプログラム実行と同時に、分岐予測の改善、プリフェッチ、キャッシュ制御などの

副次的な操作を行なうことも提案されている [6,7].

### 4 オンチップマルチ SMT

前述の通り現状の SMT プロセッサは、商用レベルでは SMP に見立てたものに、研究レベルではシングルプログラムの高速化を目指したものと位置付けられている。商用レベルにおける SMP と見立てた SMTの使用は、従来のオペレーティングシステム (OS) との親和性がよいという利点がある。例えば Microsoft 社の WindowsNT や、フリーで配布されている Linux などは SMP に対応しており、ほとんどプログラムを改変することなく SMT プロセッサに移行できる。

しかし SMP と見なすならば、ハードウェアが複雑化する SMT としなくとも、CMP を用いて実現することが可能である.一方で、現在研究レベルである単体のプログラムの並列実行の場合、CMP はハードウェアリソースが各 PE に分断され、複数スレッドに並列化できないプログラムの時には期待したほどの性能が引き出せない場合がある.我々はこれらのことから、OS との親和性を考慮したシステム全体のスループットの向上、ハードウェアの複雑化の回避、単一プログラムの実行速度の向上、これらを目指したアーキテクチャ、オンチップマルチ SMT というアーキテクチャについても今後研究を進める.

オンチップマルチ SMT は、SMT プロセッサを PE とし、その PE を複数個、1 つのチップ上で実現することにより、SMT プロセッサの SMP として動作する。複数のプロセスは OS によってそれぞれの PE に割り振られ、それらは OS によってスケジューリング、管理される。また各 PE に割り振られたプロセスは、コンパイラ(ユーザ)によって複数スレッドに分割され、その PE 内で並列実行される。またプロセス間の通信、つまり PE 間の通信は 1 つのチップ上にあるという利点をいかし、チップ上の共有メモリないし共有レジスタによって高速に行なわれる。

### 5 SMT を考慮した OS の資源管理モデル

ここではSMT を考慮した時の OS のモデルについ て議論する.

従来、OS ではプロセッサの仮想化モデルとして、Mach 以降、プロセスとはマルチプログラミングの環境下で保護を行う実行単位、スレッドとは資源を共有しあう実行単位、という2種類のモデルが採用されてきた。OS から見れば、CMP も SMT も基本的にはOS の論理スレッドとして仮想化できる。

従来の資源管理モデルの延長でとらえると,

- 1. 複数の実スレッドを実行する 1 つの SMT プロセッサを、1 つのプロセスとして仮想化、プロセス全体をスイッチする方式

- 2. 実スレッドを論理スレッドとして仮想化する方式

の2つが考えられる.

前者は、アドレス空間を共有しあう従来のスレッドとプロセスの関係を、そのまま対応つける考え方である。1つのプロセス内で生成されるスレッドは実スレッドに対応し、実スレッドの生成はコンパイラが並列化を行う。この SMT をマルチプロセッサにしたアーキテクチャでは、さらに、この複数のプロセッサを用いて、実スレッドの個数を増やすことができる。これにより、資源共有の観点からは、高性能が期待できる。

しかし、プロセス内の論理スレッドを実スレッド以上に割り付けようとすると、何らかの工夫が必要となる、ループのような均質構造を有する反復処理ならば、コンパイラでの最適化が期待できるが、サーバ処理のような非均質構造のマルチスレッド処理では、プログラマが明示的に fork などのスレッド生成命令を発行する可能性があり、個数を限定することはできない、このような理由から、後者のような論理スレッドを導入する必要が生じる.

従来の OS のスレッド管理は、コンテキストの save/restore は必須であるため、細粒度並列性を生か すための従来のスレッドよりも、さらに軽量なコンテキストの導入が不可欠である。オンチップマルチ SMT では、個々の PE 間でのスレッド割付が性能を左右する.

上記のことから、SMTおよびオンチップマルチSMT における OS の目標は、数 10 命令から 1000 命令程度 の細粒度スレッドに向けた

- 本質的課題として、SMT 向けのプログラミング モデル

- 2. 技術的課題として軽量な論理スレッドの制御方式 特に、関数呼出し程度の数命令で論理スレッドを スイッチする方式

- 3. SMT をオンチップで複数結合させるたときの資源の統合的な管理

を課題としてとらえる必要がある.

# 6 OS を考慮した SMT プロセッサ

ここでは、OS の実装を目標とした SMT プロセッサのモデルを議論する.

基本的に多数のスレッドを実行する SMT プロセッ サは、従来のプロセッサと比較して、より外部メモリ のバンド幅が問題になってくる. これに関連して、従 来のキャッシュをそのまま SMT に当てはめるのも問 題になっている [8]. また前述の通り、OS を用いてコ ンテキスト切り替えを行なう場合、コンテキストの save/restore が必須であり、メモリバンド幅は更に重 大な問題になってくる. そして, コンテキスト切り替 えはレジスタの退避のため、システム全体で実行サイ クルを大きく消費する作業の1つである.このため、 例えばこのコンテキスト切り替えのためのコンテキス ト切り替え専用のキャッシュ (C-cache) をプロセッサ 内部に実現するなどして、コンテキスト切り替えによ るメモリバンド幅への影響を取り除く必要がある. こ の C-cache のため、プロセッサは OS がこのキャッシュ を直接アクセスできるように新たな命令を用意するの が望ましい.また、この C-cache のトレードオフとし て、従来の1次キャッシュ、2次キャッシュの削減が考 えられる.

そして SMT プロセッサ上において、本来 OS が管理するプロセスを管理する機構だけでなく、コンパイラやユーザが生成するスレッドを OS が管理できるようにするためのアーキテクチャによるサポートが必要である。前述の通り、OS はシステム全体の資源を管理する役割があり、当然プロセッサの資源も管理する、しかしコンパイラやユーザが OS のシステムコールを介することなく、SMT プロセッサのスレッド生成命令を実行できるアーキテクチャの場合、資源の管理者たる OS にそのスレッド生成を何らかの形で通知する

必要がある. これを回避する方法としては、スレッド生成を行なう時は必ず OS を介するというモデルにすればよいが、本来 SMT プロセッサに期待される軽量なスレッド生成・消滅の実現が困難になる. このため、軽量なスレッド生成・消滅、そして OS の資源管理を両立させる場合はプロセッサ側の何らかのサポートが必要になってくる.

この点で、オンチップマルチ SMT を考えた場合、SMT である PE 内部はコンパイラまたはユーザのスレッド生成空間、そしてチップ全体は OS のプロセス管理空間という切り分けができる。しかし、PE の内部に生成できるスレッド数以上をコンパイラやユーザが生成しようとした場合、コンパイラやユーザは OSまたはアーキテクチャのサポートが必要となり、これはアーキテクチャ、OS、コンパイラ(ユーザ)、全てにまたがる課題の1つである。

このようにSMTプロセッサにおいてOSを考慮した場合、メモリバンド幅などのハードウェアとしての課題、OSの管理機構をサポートを検討する必要がある.

#### 7 まとめ

本論文では、現在実現されているいくつかのプロセッサモデルの説明を行なった。また最近注目されている SMT アーキテクチャの内部モデルを示し、SMTプロセッサと OS を協調させるための課題を述べた。今後は、ここで述べた課題を検討し、SMT アーキテクチャと OS を密接に協調させた、より強固なシステムの構築を目指す。さらにはオンチップマルチ SMTの検討も今後行なう。

### 参考文献

- S. Palacharla, N.P. Jouppi, and J.E. Smith: Complexity-effective superscalar processors, 27th Int'l Symp. on Computer Architecture, 1997

- [2] D. M. Tullsen, S. J. Eggers, and H. M. Levy: Simultaneous multithreading: Maximizing on-chip parallelism, in Proceedings of the 22nd Annual International Symposium on Computer Architecture, pp.392-403, 1995

- [3] http://www.intel.com/

- [4] 河原 章二, M. Yankelevsky, 中條 拓伯, C. Polychronopoulos: オンチップマルチスレッドプロセッ サα-Coral のアーキテクチャ並列処理シンポジウム (JSPP'2001), pp.39-46, 2001

- [5] S. Wallace, B. Calder, and D. M. Tullsen: Threaded Multiple Path Execution, Proc. of Int'l Symp. on Computer Architecture(ISCA98), pp.238-249, 1998

- [6] R. S. Chappell, J. Stark, S. P. Kim, S. K. Reinhardt, and Y. N. Patt: Simultaneous Subordinate Microthreading (SSMT), Proc. of Int'l Symp. on Computer Architecture(ISCA99), pp.186-195, 1999

- [7] 佐藤 寿倫, 有田 五次郎: KIT COSMOS プロセッサ:背 景と着想 IEICE Technical Report CPSY99-115, pp.69-76, 2000

- [8] S. Hily, and A. Seznec: Standard Memory Hierarchy Does Not Fit Simultaneous Multithreading, In Workshop on MultiThreaded Execution, Architecture and Compilation, Colorad State Univ. Technical Report CS-98-102, 1998