# 1J-02

# SPL 開発におけるペアワイズ法を用いたテスト手法について

城谷 まりな†1 岸 知二†1

†1 早稲田大学 創造理工学研究科 経営システム工学専攻

## 1. はじめに

ソフトウェア開発において、生産性の向上・品 質の安定等様々な要求が存在し、これに対応する 方策として再利用技術がある。再利用技術を活用 した開発手法として、ソフトウェアプロダクトラ イン (SPL) 開発がある。SPL 開発では、製品群 を開発する際に製品間の共通性と可変性を明ら かにした上で再利用資産(コア資産)を構築し再 利用する。SPL 開発には、コア資産を開発する活 動であるドメインエンジニアリング、コア資産を 用いて個々のプロダクトを開発する活動である アプリケーションエンジニアリングが存在する。 ここで、ドメインエンジニアリングでは SPL 全 体の要求を踏まえて再利用されるコア資産が正 しく構築されているかを検証する必要があるた め、コア資産のテストは重要な工程であり、本研 究ではこのテストに着目する。

## 2. 背景知識

#### 2.1. フィーチャモデル(FM)

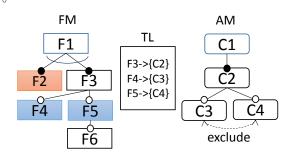

ドメインエンジニアリングの要求モデルとして、製品間の共通性・可変性を表現するために用いられる[1]。末端利用者から可視な特徴であるフィーチャ(F)を階層的に表している。個々のフィーチャ毎に関連が存在し、またフィーチャ間でクロスツリー制約(CT 制約)が存在する。図1の左側はFMの例である。

## 2.2. アーキテクチャモデル(AM)

本研究では、ドメインエンジニアリングで導出される設計モデルとして扱う。可変性を持つ FMと対応させ、構成要素の可変性をコンポーネント(C)として表現し、その組合せでバリアント(選択肢)を表現する。図 1 の右側は AM の例である。

## 2.3. トレーサビリティリンク(TL)

フィーチャを実現するために必要なバリアントを示すリンクである。図1中央はTLの例であ

る。

図 1 FM,AM,TL の例

#### 2.4. ペアワイズ法

ペアワイズ法とは、全てのパラメータ値のペアをカバーするようなテストケースを生成することで、テストケース削減を可能にする手法である。Osterら[2]は、FMにペアワイズ法を適用し、全てのフィーチャのペアを含むように、テストするプロダクトを選択することで、テストの質を保ちながらテストすべきプロダクトを削減する手法を提案した。

例えば、図1の場合、ペアワイズ法を適用すると、 $P1\sim P6$ の6製品が選出される。これは、 $P1\sim P6$ をテストすることで、全てのフィーチャのペアの動作確認ができることを意味する。

表1 図1から考えうるプロダクト(一:否定)

|    | F1 | F2/F3 | F4  | F5  | F6  |

|----|----|-------|-----|-----|-----|

| P1 | F1 | F2    | ¬F4 | ¬F5 | ¬F6 |

| P2 | F1 | F3    | ¬F4 | ¬F5 | ¬F6 |

| P3 | F1 | F3    | ¬F4 | F5  | F6  |

| P4 | F1 | F3    | F4  | ¬F5 | ¬F6 |

| P5 | F1 | F3    | F4  | F5  | F6  |

| P6 | F1 | F3    | F4  | F5  | ¬F6 |

#### 3. 問題と分析

# 3.1. デッドフィーチャ・選べない組合せ

モデル間の不整合によって様々な現象が発生 する可能性があるが、本研究では以下に着目する。

デッドフィーチャ(dead feauture, DF): 実現できないフィーチャのことである。例えば、

図 1 において、F3 は必須 C である C2 を必要とする為、必須 F となるが、F2 と F3 は同時に選択できないため、F2 は DF である。

選べない組合せ(dead feature pairs, DFP):

実現できないフィーチャのペアである。例えば、図1において、F4とF5はそれぞれC3とC4を必要とするが、C3とC4は同時に選択できないため、F4とF5のペアはDFPとなってしまう。

# 3.2. DF/DFP がテストに与える問題(①)

DF/DFP を含むプロダクトは実行不可能であり、このプロダクトのテストが行えない。実行不可能なプロダクトの中に、実現可能なフィーチャのペアがあったとしても、動作確認を行えず、テストの質が低下する。よって、DF/DFP を含まないような、質の高いテストを行うためには、DF/DFP をペアワイズ法適用の前に認識することが理想である。例えば、表 1 において、DF/DFP を含む P1,P5,P6 に含まれ、他に含まれない、実現可能なペア(P6 の F5・ $\neg$ F6)のテストを行う事が出来ない。しかし、DF/DFP を事前に認識する事が出来れば、全てのペアを網羅する為には P2,P3,P4,P7 を選択すれば良い事がわかる。

表 2 DF/DFP を考慮した場合

| • • |    |       | - · · - · · · · · · · · · · · · · · · · |     |     |  |

|-----|----|-------|-----------------------------------------|-----|-----|--|

|     | F1 | F2/F3 | F4                                      | F5  | F6  |  |

| P2  | F1 | F3    | ¬F4                                     | ¬F5 | ¬F6 |  |

| P3  | F1 | F3    | ¬F4                                     | F5  | F6  |  |

| P4  | F1 | F3    | F4                                      | ¬F5 | ¬F6 |  |

| P7  | F1 | F3    | ¬F4                                     | F5  | ¬F6 |  |

# 3.3. DF/DFP 検出に関する問題(②)

テストの質の向上のために、全ての DF/DFP を 事前に認識する事は困難である事が多い。以下は その典型的な例である。

- 各モデルは膨大かつ複雑であり、特にAMの 全情報を得る事は困難である。そのため、 DF/DFPの検出に必要な情報が得られない 事がある。

- FM、AM は数千もの構成要素を持つことも あり、全ての DF/DFP を検出する事は高コストである。具体的には、FM/AM/TL を辿った 複数のパスの組合せを調べる必要があるため、計算量が非常に大きくなる。

#### 4. 提案手法

# 4.1. 手法の考え・流れ

本研究では、ペアワイズ法を拡張し、DF/DFP を事前に認識し一部検出する事でテストの質を 向上させる、グレーボックステスト手法を提案する。

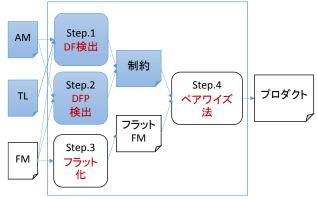

図 2 提案手法の全体像

- DF/DFP 検出(Step.1,2):DF/DFP の検出を行 う。検出される DF/DFP は、既存の DF 検出 パターン[3]を応用して検出した。

- フラット化(Step.3):FM にペアワイズ法を適用する際は、フラット化を行うのが一般的である[2]。フラット化とは、アルゴリズムに従い、階層構造を持つ FM を 3 階層に変換することで、組合せテストの入力に準じた書式にすることを言う。

- ペアワイズ法の適用(Step.4):フラット化された FM、DF/DFP の制約を入力とし、ペアワイズ法を行う事で、不整合を含まないプロダクトの選択が可能となる。

#### 5. まとめ

本研究では、SPL 開発のコア資産におけるテスト手法として、モデル内、モデル間で発生するDF/DFP を考慮することで、ペアワイズ法を拡張し、グレーボックステストを実現した。これにより、実行可能なプロダクトをより多く選択する事が可能になった。しかし、提案手法を適用する事で逆にテストの質が低下してしまうケースが存在する為、今後対応していきたい。

#### 参考文献

- [1] Kang, K.C., et al.: Feature-Oriented Domain Analysis (FODA) Feasibility Study, CMU/SEI-90-TR-21, ESD-90-TR-222, 1990.

- [2] Oster, S., et al.: Automated Incremental Pairwise Testing of Software Product Lines. the 14<sup>th</sup> International Software Product Line Conference (SPLC 2010), pp. 196-210, 2010.

- [3] Trinidad, P.,et al: Explanations for agile feature models. Proceedings of the 1st International Workshop on Agile Product Line Engineering (APLE'06). 2006.