## C-019

# DVI出力をもつ位相ホログラフィ専用計算機の開発

Special Purpose Computer for Phase Modulation Type Electro-Holography with DVI output

增田 信之 $^*$  遠藤 優 $^\dagger$  角江 崇 $^\dagger$  下馬場 朋禄 $^\dagger$  伊藤 智義 $^\dagger$  市橋 保之 $^\ddagger$

Nobuyuki Masuda Yutaka Endo Takashi Kakue Tomoyoshi Shimobaba Tomoyoshi Ito Yasuyuki Ichihashi

## 1. まえがき

近年,立体映像を表示するデバイスが次々と発売されているが,その多くは専用の眼鏡が必要であったり,目に負担がかかるなどの問題がある.これらの問題を解決し,より自然な3次元映像を実現する手法として電子ホログラフィがある.しかし,3次元映像再生時に用いるCGH(Computer Generated Hologram)の作成には膨大な量の演算が必要であるため,ホログラフィ技術を用いて滑らかな3次元映像を再生するためには,演算処理の高速化が不可欠である.

我々の研究グループでは CGH を高速に作成するための専用計算機システム HORN(HOlographic ReconstructioN)を開発してきた([1,2]).しかし,従来の HORN-7では作成した CGH を一度 PC に送信し,それから高精細液晶ディスプレイ (LCD: Liquid Crystal Display)に表示する必要があり,この通信時間が大きなコストになっていた.本研究では,作成した CGHを HORN-7に搭載されている DVI(Digital Visual Interface)端子から直接LCDに出力することで処理時間を短縮した.また,ホログラフィには振幅型と位相型の2種類があり,位相型は振幅型に比べて光の利用効率が良いとされ,良質な再生像を得ることができるため,近年主流になりつつある.本研究では,DVI 出力を持つ位相電子ホログラフィ専用計算機を開発し,従来より滑らかで良質な3次元映像を得ることに成功した.

## 2. データ転送方向

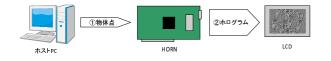

昨年度までの HORN-7 を用いた CGH 作成システムのデータの流れを説明する. はじめにホスト PC は 3D オブジェクトを構成する物体点データを HORN に送る. HORN は受け取った物体点データを元に計算を行ってホログラムを作成し, PC へと転送した後, LCD に表示するという流れになっていた. しかし, 物体点数が数万点程度の場合,物体点データが数百 KB であるのに対し,ホログラムの情報量は物体点数によらず約 2MB と大きい. そのため,このホログラムの転送時間が大きなコストとなっていた.

図 1: CGH 作成システムのデータの流れ

そこで本研究では、FPGA評価ボードに搭載されてい

る DVI 出力端子から直接 LCD にホログラムを転送する ことでこの問題を解決した.新しい HORN-7 を用いた CGH 作成システムの概略図を図 1 に示す.

## 3. 設計回路概要

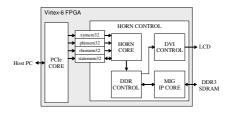

今回開発した HORN-7 の FPGA 内部回路構成図を図 3 に示す .

図 2: FPGA 内部ブロック図

PCIe CORE は,ホスト PC と HORN の間の通信を制御する. HORN CONTROL はホログラムの位相分布を求める計算を行う HORN CORE, DDR3(外部RAM) とのデータのやり取りを制御する DDR CONTROL および MIG IP CORE, LCD へのデータ転送を制御する DVI CONTROL から構成され,これらをステートマシンで一括して制御している. PCIe COREと HORN CONTROL の間でのデータのやり取りはxymem32,phimem32,rhomem32,statemem32の4つのデュアルポート RAM を介して行う.

## 3.1 位相分布計算回路

ホログラム面上の座標  $(x_a,y_a)$  における位相分布  $\phi(x_a,y_a)$  は , 式 (1) に示すように複素振幅分布  $U(x_a,y_a)$  の偏角を計算することで求める.さらに  $U(x_a,y_a)$  は式 (2) , および式 (3) で表される.ここで , N は物体点数 , p はドットピッチ ,  $\lambda$  は光源の波長 ,  $(x_j,y_j,z_j)$  は物体点の座標である.さらに HORN CORE では , フレネル近似 , 漸化式といった高速化アルゴリズム ([3]) を適用し , 1 度に 640 画素分の位相分布をパイプライン処理で計算することができる.

$$\psi(x_a, y_a) = \arg \left[ U\left(x_a, y_a\right) \right] \tag{1}$$

$$U(x_a, y_a) = \sum_{j=1}^{N} \exp i \left(2\pi \theta_{a,j}\right)$$

(2)

$$\theta_{a,j} = \frac{p}{\lambda} \sqrt{(x_j - x_a)^2 + (y_j - y_a)^2 + z_j^2}$$

(3)

<sup>\*</sup>長岡技術科学大学電気系

<sup>†</sup>千葉大学大学院工学研究科

<sup>‡</sup>独立行政法人 情報通信研究機構

#### 3.2 外部 RAM 制御回路

DVI 端子からホログラムのデータを LCD に転送するためには,ホログラム 1 枚分  $(1,920\times1,080$  画素) のデータ約 2MB を一時的に保存する必要がある.しかし,FPGA 内部の Block RAM 領域 (約 1.87MB) では容量不足であるため,FPGA 評価ボード上に搭載されている外部 RAM(DDR3 512MB) を使用する必要がある.そのためには,Xilinx 社が提供する MIG(Memory Interface Generator) と呼ばれるソフトウェアが生成する IP コア (MIG IP CORE) を用いる.DDR CONTROL は,この MIG IP CORE を介することで外部 RAM への書き込み,および読み出しを行う.

### 3.3 DVI 出力制御回路

ホログラムを LCD に表示する際には , 外部 RAM から位相分布の計算結果を 1 列 (1,920 画素) ずつ読み出し , これを 1,080 回繰り返すことで 1 枚のホログラムのデータを転送する . 動画化のためにはホログラムを連続してコマ送りにする必要があるが , 外部 RAM への書き込み , 読み出しを同時に行うことはできないため , HORN CONTROL のステートマシンは位相分布計算回路 , 外部 RAM 制御回路 , DVI 出力制御回路の同期を取り , 書き込みと読み出しを切り替えている .

#### 4. Performance

本研究で開発した HORN-7 の回路規模などの概要を表 1 に示す .

表 1: HORN-7 仕様

| 回路面積       | LUT 使用率      | 73 %      |

|------------|--------------|-----------|

|            | Register 使用率 | 45 %      |

| 最大動作周波数    |              | 183.0 MHz |

| 動作周波数      |              | 180.0 MHz |

| 内部 RAM 使用率 |              | 88 %      |

| パイプライン段数   |              | 640 段     |

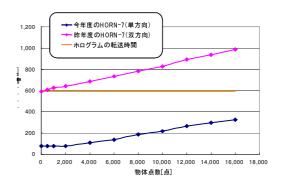

また,昨年度と今年度の HORN-7 で,ホログラム 1 枚を表示するのに要する処理時間の比較を図 4 に示す.昨年度の HORN-7 では,ホログラムをホスト PC に転送するのに約 0.6 秒かかっており,物体点数に関係なくこれ以上の高速化は見込めなかった.

本研究で開発した新しい HORN-7 ではこの問題を解決し,例えば物体点数約 6,000 点の 3D オブジェクトのホログラムを,1 枚当たり約 0.14 秒で表示することができる.これはフレームレートに換算すると,1 秒間当たりに約 7 枚のホログラムを表示可能であることを示している.

開発した HORN-7 を使用し,実際に光学系を用いて ホログラムの再生を行った際の再生像を図4に示す.ホストPC から何パターンかの恐竜の物体点データを連続して送ることにより,恐竜が歩いている様子を確認することができた.

図 3: 処理時間

図 4: 再生像

## 5. まとめと今後の課題

本研究では,HORN-7から直接 DVI 出力端子を用いてホログラムを転送することにより,昨年度の HORN-7で約 0.6 秒かかっていた転送時間を削減することができた.これにより,物体点数約 6,000 点の 3D オブジェクトを秒間約 7 フレームで再生することに成功した.

さらなる高速化を実現するためには,一度に計算できる画素の数(パイプライン段数)を増やすことが有効である.しかし,本研究で使用した FPGA(Virtex-6)では,Block RAM 等の回路リソースの制限から,現在の640段からパイプライン段数を大幅に増やすことは難しい.

そこで,回路リソースの豊富な最新型の FPGA への実装や,複数枚の FPGA ボードを並列化することで,さらなる高速化が期待できる.

#### 謝辞

本研究の一部は,科学研究費補助金基盤研究 (C)(課題番号 24500056),および科学研究費補助金基盤研究 (A)(課題番号 25240015)による.

## 参考文献

- Tomoyoshi Ito, et al. Opt. Express, Vol.13, pp 1923-1932 (2005)

- [2] Yasuyuki Ichihashi, et al. Opt. Express, Vol.17, pp. 13895-13903 (2009)

- [3] Tomoyoshi Shimobaba, *et al.* Comput. Phys. Commun., Vol.138, No.1, pp. 44-52 (2001)