C-025

# 高電磁環境下で論理回路に発生する過渡故障の実験的評価

Experimental Evaluation of Transient Faults on Logic Circuit in Highly Electromagnetic Environments

永島 一磨 † 今井 健太 † 新井 雅之 † 福本 聡 † 和田 圭二 ‡

Kazuma Nagashima Kenta Imai Masayuki Arai Satoshi Fukumoto Keiji Wada

#### 1. まえがき

近年,電力変換回路では,主回路のパルス大電流部分が引き起こす近傍電磁界ノイズ (near-field noise) の影響が問題になっている. 近傍電磁界ノイズとは,電力変換回路のトランジスタがオン,オフするときに流れるパルス電流に重畳する過渡的な交流成分による電磁ノイズなどを指す. このノイズは,電力変換回路の制御回路や周辺回路,特に論理回路に大規模な同時多重過渡故障を発生させる可能性があり、その対策が必須となっている.

本研究では、こうした過渡故障に耐性を持つ順序回路を検討するための基礎的な準備として、近傍電磁界ノイズが論理回路の動作にもたらす故障について観測した、実際のインバータによってノイズが発生する高電磁環境を設定し、汎用ロジックICとFPGAで実装した簡単な順序回路がその近傍でどのような影響を受けるかを評価した、

### 2. 実験用主回路

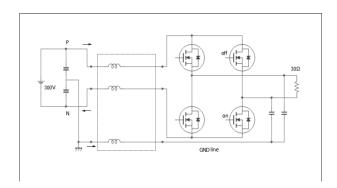

本研究では、直流電源と MOSFET を使用した評価用インバータ回路 (以下, 主回路) によって高電磁環境を設定した、主回路の回路図を図 1 に示す、実験では, 主回路の線路部分 (図 1 の点線枠部分) に評価用回路を近接させ、ノイズの挿入状況や回路動作を確認した。主回路のスイッチング周波数は 1kHz, 電圧は 300V, 電流は 20Aに設定した。

図 1: 評価用インバータ回路の回路図.

### 3. 評価用順序回路

高電磁環境にさらされる評価用順序回路は,ロジックICとFPGAを用いて作成した.回路は,12bitカウンタと2個の256bitレジスタ間で単純なデータ送受信をおこなうものの2種類である.12bitカウンタ回路は汎用ロジックICを用いた回路とFPGAボードを用いた回路の二つを実装した.また,256bitレジスタ間のデータ送受信回路はFPGAで実装した.

### 3.1 12bit カウンタ回路

汎用ロジック IC は、カウンタ IC(74HC4040) を使用した。出力値を LED で表示させ、外部からの電源にはニッケル水素電池を用いて 4.8V を給電する。クロックを任意のタイミングで入力するため、シュミットトリガインバータ IC(74HC14) を用いてチャタリングを防止した手動式クロック発生器を作成した。

FPGA 実装では、ハードウェア記述言語に Verilog HDLを、FPGA ボードにヒューマンデータ社の XCM-001-400を使用した。このボードの必要な電源は DC 3.3V、オンボードクロックは 48MHz である。電源電圧は、ニッケル水素電池で 3.6V を供給している。また、クロック信号をオンボードクロックと手動式クロックで任意に切り替えられるように設定した。手動式クロック発生器には、上記と同じものを使用した。オンボードクロックは 48MHzである。これを分周して約 0.7 秒周期で最下位ビットが変化するように設定した。

#### 3.2 256bit レジスタ間のデータ送受信回路

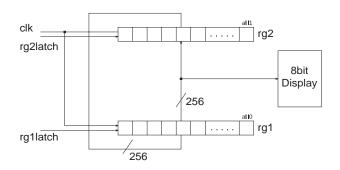

256bit のレジス夕間でデータを送受する回路の概念図を図 2 で表す.これは FPGA によって実装した.rg1, rg2 は,それぞれのラッチ信号が High のときだけクロックの立ち上がりに同期してレジスタの値を更新する.値を更新した後は自身のラッチ信号を Low に更新し,相手のラッチ信号を High に更新する.rg2 に含まれる 1 の総数は 2 進数変換されて LED 表示される.初期値としてrg1 はオール 0, rg2 はオール 1, rg1latch は 1, rg2latch は 0 となっている.クロックは FPGA のオンボードクロックを使用している.また本研究では上記で述べた順序回路の他に,FPGA 実装した 12bit カウンタと同様に分周回路を組み込んだものを用意した.さらに,ノイズによって誤りがレジスタに取り込まれたとき,その値を保持して LED 表示するように仕様変更したものも実装した.

<sup>&</sup>lt;sup>†</sup>首都大学東京 大学院 システムデザイン研究科, Graduate School of System Design, Tokyo Metropolitan University

<sup>&</sup>lt;sup>‡</sup>首都大学東京 都市教養学部 <sup>2</sup>理工学系, School of Science and Engineering, Faculty of Urban Liberal Arts, Tokyo Metropolitan University

図 2: 256bit レジスタをもつ順序回路の概念図.

### 4. 実験結果

#### 4.1 12bit カウンタ回路

12bit カウンタ回路の実験結果を表 1 で示す. まず, 汎用ロジック IC を用いた 12bit カウンタで実験を行った. カウンタ回路が主回路の大電流部分から離れている場合は, 手動クロックにしたがってカウントアップし, 過渡故障は認められなかった. 主回路に近づけるに従って, 手動クロックとは無関係にカウントアップする様子が観測され始めた. カウンタの最上位ビットが約 2 秒の周期で点滅したことから, 主回路の電流の立ち上がりと立ち下がりに発生するオーバシュートとアンダーシュートによるノイズ周波数 2kHz に同期してカウントアップしていることが判明した. FPGA 実装した 12bit カウンタで実験を行ったが, 汎用ロジック IC の場合と同様の結果となった.

表 1: 12bit カウンタでの実験結果.

| 実装        | 観測             |

|-----------|----------------|

| 汎用ロジック IC | ノイズによってカウントアップ |

| FPGA      | ノイズによってカウントアップ |

次にクロック入力端子の状態に焦点を当てて実験した. FPGA 実装した 12bit カウンタに外部入力として繋いでいた手動式クロック発生器を外し, クロックの入力信号線をグランドに落として主回路に近づけた. この場合もクロックを接続していない状態であるにもかかわらず主回路の周期的ノイズによってカウントアップした. 次にクロックの入力信号線をグランドに落とさず, オープンにして主回路に近づけた. 入力線をグランドに落としたときとは異なり, 主回路に近づけてもカウンタアップは起こらなかった. また, 手動式クロック発生器ではなく, 分周回路を組み込んだオンボードクロックを使用して実験を行った. この場合は, 回路を主回路に近づけてもノイズの影響を受けることなく正常に動作した.

表 2: クロックの仕様を変更したときの実験結果.

| クロック仕様       | 観測             |

|--------------|----------------|

| 通常配線         | ノイズによってカウントアップ |

| クロック端子を GNG  | ノイズによってカウントアップ |

| クロック端子を OPEN | カウントアップせず      |

| オンボードクロック    | 正常にカウントアップ     |

#### 4.2 256bit レジスタの順序回路

256bit レジスタの順序回路の実験結果について述べる. この回路を主回路に近づけた場合, LED 表示は最初のクロックの立ち上がりで値が初期値から 256(9bit 目だけ点灯) に更新されたが, その後変化は無く正常に動作した. これは分周回路を挟んだものや仕様を変更したものも同様の結果となり, ノイズの影響を受けていないことがわかった.

#### 4.3 考察

以上の実験結果から、いずれもクロック信号を外部入力した場合に限ってノイズの影響を受けていることがわかる。このことから、主回路が引き起こすノイズがクロックの信号線に混入しているものと推測される。また、市販のFPGAにはノイズ対策が十分に施されており、オンボードクロックを使用する場合にはノイズの影響を受けにくいものと考えられる。

これらから,本研究の実験環境においては,従来の高信頼化順序回路でしばしば仮定された"過渡パルスは回路中のデータパスや制御信号に同時多重に発生してその信号値に影響するが,クロック信号はその影響を受けない"という故障モデル[1]が成り立たないこと判る.また逆に,過渡パルスがクロック信号の入力線に発生し,データパスや制御信号は正常であるような故障モデルを考える必要があることが示唆された.

## 5. むすび

本研究では、高電磁環境下で発生する論理回路の過渡 故障に耐性を持つ順序回路を考えるための導入として、高 電磁環境を実現するインバータ回路と評価用順序回路を 用いて過渡故障の実装評価を行った、今後の課題として、 評価用論理回路の電源グランドを主回路の電源グランド と共通化した場合の観測を行うことなどが挙げられる。

#### 参考文献

[1] サイサナソンカム アロムハック, 今井 健太, 小山善史, 新井 雅之, 福本 聡, "高電磁環境下における過渡故障に耐性を持つ順序回路方式の検討," 信学技報, vol.111, no. 252, DC2011-21, 2011, pp.7-11.