# 大規模高速 ASIC 用クロック分配回路レイアウト 設計ツールの開発

寺 井 正 幸 † 金 本 俊 幾 † 小 谷 健 †

柴 山 泰 範 † 岡 崎 芳 †

堀 場 康 孝 † 岩 出 秀 平 †

本論文は,大規模高速 ASIC 用クロック分配回路のレイアウト設計手法を提案する.対象とする ASIC は,セルを配置配線して回路を実現する.本手法の特長は,大規模クロック分配回路のスキューを抑えることを狙ったトランク方式レイアウト,すなわち,LSI チップ全面にメッシュ状に敷設したトランク配線を介して多数の並列駆動クロックバッファでフリップフロップを駆動する方式を採用して いることと,配置配線後にクロックスキュー改善のために FF 配置の疎密に基づきクロックバッファの駆動力調整を行うことである.本手法を実現したプログラムを, $1.5\,\mathrm{M}$  ゲート規模, $200\,\mathrm{MHz}$  の周波数のクロックを含む LSI 設計に適用し,その有効性を示す.

# A Clock Distribution Circuit Layout Design Tool for Large-scale and High-speed ASICs

Masayuki Terai,† Toshiki Kanamoto,†† Ken Kotani,†† Yasunori Shibayama,†† Kaoru Okazaki,†, Yasutaka Horiba††† and Shuhei Iwade†

This paper proposes a clock distribution circuit layout tool, termed CCgen, for ASIC's. We employs the trunk layout style, which can control the resultant clock skew within a specified small value for large-scale clock distribution circuits. The proposed method consists of floor-planning, trunk circuit generation, placement and routing, and clock skew improvement that adjusts drivability of clock buffers based on the densities of flip flops on regions of the LSI chip. The application results are shown in order to demonstrate that the method is effective.

#### 1. まえがき

LSI の製造技術の微細化の進歩にともない, LSI 回路の大規模化,高速化が進むとともに,信号伝播遅延に対する配線遅延の影響が増大している.特に,チップ全体にわたるクロック信号は,長い配線が必要であり,レイアウト設計におけるクロックスキューの考慮が必須となっている.クロックスキューとは,クロックのソースからフリップフロップやラッチ等の記憶素

子(以下,FFと略記する)のクロック端子までのパス群のディレイの最大差と定義する.クロック周期をP,クロックスキューをs,FF間の最大パス遅延を $d_{max}$ ,FFのセットアップタイムを $t_s$ とすると,よく知られた以下の関係が成り立つ.

$$P \ge s + d_{max} + t_s \tag{1}$$

クロック周期を小さくするためには,スキューsと最大パス遅延  $d_{max}$  を小さい値(たとえば s は P の 5%程度)に抑えることが必要である.LSI の微細化により配線遅延の信号伝播遅延に対する割合が高まり,LSI が大規模化するにつれて,クロック回路の設計におけるスキューの制御は困難になってきている.

クロック分配回路のレイアウト方式としては,RC 遅延バランス配線手法に基づくクロック木 $^{1)\sim4}$ ,大型 クロックドライバでチップ内の FF を一括駆動するクロックトランク $^{5),6}$ が報告されている.クロック木のうち,H-tree  $^{1)}$ は LSI 上の非対称な FF の配置に対しては適用困難であり,文献  $^{2}$ 0 はクロック信号の伝播

Faculty of Engineering, Kansai University

現在,大阪電気通信大学工学部

Presently with Osaka Electro-Communication University

<sup>†</sup> 三菱電機株式会社システム LSI 事業化推進センター System LSI Development Center, Mitsubishi Electric Corporation

<sup>††</sup> 三菱電機株式会社システム LSI 事業統括部 System LSI Division, Mitsubishi Electric Corporation

<sup>†††</sup> 関西大学工学部電気工学科

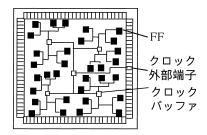

図1 クロック木分配回路 Fig. 1 Clock tree circuit.

遅延ではなく配線長の均衡を狙った方法である.その 後発表されたクロック木 $^{3),4)}$ は,図1のように複数段 のクロックドライバによりバイナリ木状の回路を構成 し, その末端のノードにつながる FF を駆動する. そ の生成処理は LSI チップ上の FF のクラスタリング, クラスタ群のトップダウン分割により木状回路のトポ ロジ作成とバッファ挿入位置の決定,配線の寄生容量 と抵抗による RC 遅延を考慮した等遅延配線からなる. 等遅延配線を行うには配線障害物がほとんどないこと が必要なので、通常はクロック信号の等遅延配線は他 の信号ネット配線より先に行われる、等遅延配線手法 を用いてもクロック木のレイアウト設計でスキューが 生じる原因は,等遅延配線処理で配線障害物(すなわ ち, セル内配線や電源グランド配線等)が多い場合に 迂回配線を余儀なくされることと、この段階ではまだ 配線されていない通常の信号ネットとクロック配線の 間の隣接配線容量を正確には考慮できないことがあげ られる.

市販の業界標準ツールを用いた我々の評価では,実際の ASIC クロック木を生成した場合メガセルや電源配線等の配線障害物によってスキュー値は大きくなる.また非常に多数の FF を駆動する場合,クロック木の段数やクロックパス長が大きくなり,スキューはさらに大きくなることを確認している.一方,クロックトランク方式は,駆動力の大きなクロックドライバでチップ全面にメッシュ状に敷設されたトランク配線,および,FF とトランク間の短い配線を介して FF を駆動する方式である.この方式では,FF 配置の疎密によりスキューが増大するという問題が生じる.

本論文では,クロックトランク方式でかつ FF 配置の疎密に対するスキュー改善機能を備えたクロック分配回路レイアウトツール CCgen (clock distribution circuit generator)とクロックスキュー解析ツール CSDP (clock skew error diagnosis program  $)^{\circ}$ から構成される設計手法を提案する.対象とする LSI は,論理ゲート,FF 等の機能を持つセルと呼ばれる回路

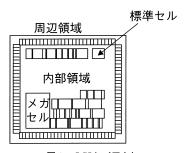

図2 LSIレイアウト Fig. 2 LSI layout.

構成要素を LSI チップ上に配置し, セル端子間の接続情報(ネットの集合)に従いセル間を配線するレイアウト方式である.計算機用回路等において要求される200 MHz 級のクロック信号を 60,000 個程度の FF に供給するような大規模かつ高い周波数のクロック分配回路に対して, CCgen はトランク方式の分配回路を自動生成し, CSDP が生成結果のクロックスキューを評価し,各 FF 入力端子でのクロック信号遅延値を表示する.

本レイアウト設計手法は大規模クロック分配回路のスキューを抑えることを狙ったトランク方式を採用しており、その特長は、配置配線後に FF 配置の疎密に基づくクロックバッファの駆動力調整を行うことである・全ネットの配線後に駆動力調整を行うので、通常の信号ネットとクロック配線間の隣接配線容量も考慮した正確な配線寄生 RC を用いてスキュー値を評価し改善が行える・本システムを、1.5 M ゲート規模、200 MHz の周波数のクロックを含むシステム LSI 設計に適用し、その有効性を示す・

#### 2. LSI のレイアウトモデル

本論文で取り扱う LSI はセルベース設計方式で,そのレイアウト構造を図 2 に示す.LSI は中心部分の内部領域と,内部領域を取り囲む周辺領域から構成される.周辺領域には I/O バッファセルが,内部領域には 1 対の p および n 型トランジスタを横 1 列に並べトランジスタ間を接続して実現した論理ゲートや FF 等の機能を持つ標準セルと RAM/ROM のようなメガセルが配置される.セルの端子間の配線要求をネットと呼ぶ.ネットの配線には 5 層の金属配線を用いる.各配線層にはあらかじめ垂直(V と表示)もしくは水平方向(H と表示)の優先使用方向が決められている.本論文では,"VHVHV"(第 1 層が V,第 2 層が H,  $\cdots$ ,第 5 層が V)の配線層使用方式を採用する.内部領域には垂直および水平方向の配線トラックが定義さ

トランクバッファ回路 (垂直トランク配線の下に置く)

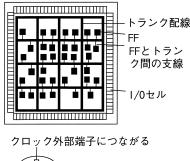

図 3 トランク方式クロック分配回路 Fig. 3 Clock circuit of trunk layout style.

れ,配線は配線トラックの上に置かれる.標準セルとメガセル内配線は第1層と第2層の配線を用いて構成される.このためセル間の配線は第 $3\sim5$ 層で標準セル上を自由に通過できる.一方,ROM等のメガセル上は回路特性の維持のため第3層のセル間配線の通過が禁止され,第 $4\sim5$ 層のみセル間配線が通過できる.

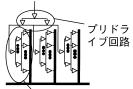

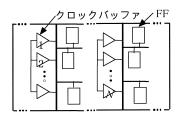

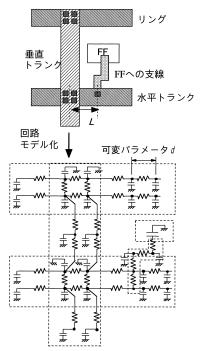

トランク方式のクロック分配回路を図3に示す.リング状のトランク配線および水平垂直のトランク配線を敷設し,各FFは近傍の水平トランク配線に接続する.リング内部の垂直トランク配線は第3層に,それ以外のトランク配線は配線層使用方式どおりに第4層と5層に置く.各垂直トランク配線はプリドライブ回路とトランクバッファ回路により駆動される.プリドライブ回路は人手配置固定し,トランクバッファ回路は垂直トランク配線の下に置く.

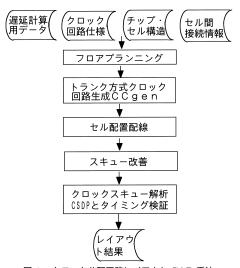

### 3. クロック分配回路レイアウトフロー

本章では,CCgen と CSDP を用いたクロック分配 回路のレイアウト設計フローについて述べる.そのフローを図 4 に示す.以下では,各ステップについて説明する.

(1)フロアプラニングおよびクロックトランク生成まず,達成可能なトランジスタ集積密度はある範囲内におさまるという経験則に基づいて回路規模(トランジスタ数)からチップサイズを見積もる.次に,標準セルを列状に並べるべきセルベンチとメガセルのチップ上での配置を決める.標準セルは同一の高さで異なった横幅を持つので,セルベンチは長方形の領

図 4 クロック分配回路レイアウト CAD 手法 Fig. 4 Layout flow of clock circuits.

域で,これらをチャネルレスで敷き詰める.この後, CCgenによりトランク配線とクロックドライバを生 成する.その方法は,4章で説明する.

### (2)セル配置配線

式 (1) のパス遅延制約に基づいて標準セルをタイミング駆動配置する.次に,セル間配線処理で,FF とトランク間のクロックネットをできるだけ短い配線で接続するとともに,クロック以外の全ネットの配線を行う.自動配置配線ツールとしては,我々が開発した ${\rm HGALOP}^{8)\sim11}$ を用いる.

#### (3) クロックスキュー改善

小領域単位で見た FF の配置分布の疎密 (FF による負荷の大小)に基づいてトランクバッファ回路の最終段のクロックバッファの駆動能力を調整する.

#### (4) クロックスキュー解析 CSDP

生成したクロック分配回路に対して, CSDP を実行してスキュー値を求め, 所望の値以下であることを確認する. CSDP は,5章で述べるように,配線の寄生容量と抵抗を抽出してトランジスタレベルのネットリストを作成し,回路シミュレーションを実行してスキュー値を評価する.

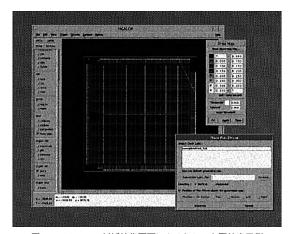

# 4. クロック分配回路生成ツール CCgen

CCgen は , トランク方式のクロック分配回路のレイアウトを自動生成し , さらに負荷の偏り ( FF 配置のばらつき ) に基づいてトランクバッファ回路の駆動能力を自動調整する機能ならびに , 生成結果のレイアウトを表示・編集する機能を備える ( 図 5 参照 ).

図 5 CCgen の対話編集画面によるトランク配線表示例 Fig. 5 Clock trunk layout results by CCgen.

トランク方式のクロック分配回路は,複数のトランクバッファ回路と,それらのトランクバッファ回路に等遅延でクロック信号を伝播するプリドライブ回路で構成する.大きな駆動能力を得るために,駆動能力の小さなバッファセルを垂直トランク配線下に多数,均等に配置し,それらを同時に駆動する.トランク・プリドライブのカスケード段数は外部よりクロック仕様として与える.通常,トランクバッファ回路は2~3段,プリドライブ回路は1~2段で構成すると指定する.また,トランク配線の配線幅,配線層と間隔の最大許容値も外部からユーザが与える.

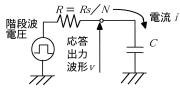

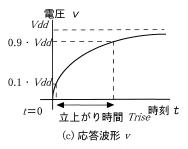

CCgen は,まず初めに,トランクバッファ回路の最終段のバッファセル総数 N を算出する.FF 入力端子容量の総和とトランクの配線寄生容量見積り値の和を C,バッファセルのソース抵抗を Rs,電源電圧を Vdd とすると,N の算出手法は以下のようになる.図  $\mathbf{6}$  (a) の最終段バッファセルから FF へのクロック分配回路におけるバッファセルの出力電圧波形 v は,図  $\mathbf{6}$  (b) の RC 直列回路へ階段波形を印加した場合の応答波形で近似できる.図  $\mathbf{6}$  (b) の応答出力波形 v と電流 i は式 (2) と (3) で表現される.

$$v = Vdd \left(1 - \exp(-t/RC)\right) \tag{2}$$

$$i = (Vdd/R)\exp(-t/RC) \tag{3}$$

式 (2) の応答波形 v は図 6 (c) で表される.本段階では図 6 (c) の波形の立ち上がり時間 Trise が十分小さい値(周期の 1/30 程度)になるように,すなわち,式 (4) を満たすように,バッファ総数 N を決める.

$$Trise = RC \cdot \log 9 < [周期の約 1/30]$$

(4)

後述するスキュー改善処理はクロックバッファを駆動力 0 のダミーセルに置換してスキューを改善するので, 改善後のクロック波形の立ち上がり時間はスキュー

(a) トランクバッファ回路からFFへの クロック回路

(b) 回路(a)のRC直列回路モデル

図 6 トランクバッファ回路のバッファセル数算出手法 Fig. 6 Calculation of buffer cell count.

改善前に比べて大きくなる.後のスキュー改善に備えて,本段階では N を十分大きい値に設定しておく.

次に,垂直トランク配線本数 T を,[ チップ幅]/[ 垂直トランク配線間隔の最大許容値] に等しいかまたはこれを超える最小の整数と決定し,1 本の垂直トランク配線あたりのバッファセル数を算出する.その後,順次前段のバッファセル数を算出する.その際にも図 6 (b) の RC 直列回路モデルを用いるが,この場合の C は次段バッファセルの入力端子容量の総和と次段との配線の寄生容量見積り値の和とし,立ち上がり時間 Trise の最大許容値としては通常の値(周期の 1/10 程度)を用いる.最後に,算出値に従ってバッファセルを配置し,それらの間の配線,ならびに,最終段バッファセルの出力端子に接続する垂直トランク配線を生成する.

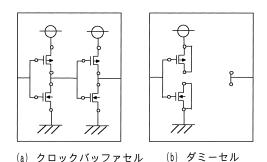

FF 配置は一般に疎密を生じる.疎の領域では密の領域と比較して負荷容量が小さいため FF へのクロック信号の遅延時間が短くなり,これが大きなスキューを生じる1つの大きな原因となる.疎な領域の近傍のクロックバッファセル(最終段セル)を駆動能力0のダミーセルへ置き換えることにより,疎領域の FF へのクロック信号遅延時間を密領域の遅延時間に揃え,

図7 ダミーセルの回路 Fig.7 Dummy cell circuit.

スキューを小さくできる.ダミーセルは,図7に示すように信号受け側のトランジスタのソースドレイン間をショートしたうえで出力側のトランジスタを取り除いたセルである.バッファセル削除ではなくダミーセル置換の採用により,バッファセルとダミーセルの入力端子容量は同一となり,最適化前後においてクロック分配回路の入力から最終段セル入力端子までの遅延時間は変化しない.

各垂直トランク配線の下に置くトランクバッファ回路はすべて同一にすることから,数千個以上のFFへのクロック分配回路の場合で,クロック入力から最終段バッファセルまでのクロック信号到達時間差は,クロック分配回路全体のスキューの5%以内であることが多いと経験的に分かっている.したがって,クロック入力から最終段バッファまでの遅延は変えずに,最終段バッファからFF入力端子までの遅延を揃えるように改善して目標スキューを達成する手法は有効である.この原理を用いて,CCgenは,後述のCSDPを用いて,最終段バッファセルから各FFへの遅延時間を求め,遅延最小のFF近傍の最終段バッファセルをダミーセルへ置き換えるスキュー改善処理を行う.

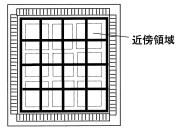

ダミーセルへの置換は、処理を高速化するために以下のような複数バッファセルを並行して置換する技法を用いている。まず、近傍領域とダミーセル置換操作を定義する。通常、上記の遅延時間最小のFFは最終段バッファセルが駆動する垂直トランク配線の近くに位置するので、垂直トランクを中心線として近傍領域を以下のように定める。

[近傍領域の定義] 水平および垂直トランク配線の交点を中心とし,高さが水平トランク間隔と等しく,横幅が垂直トランク間隔に等しい矩形を近傍領域と定義する.ただし,チップ上下左右端の近傍領域は,それぞれ高さと横幅を図8のように拡張する.

[ダミーセル置換操作] 最終段バッファセルから

図8 近傍領域の定義

Fig. 8 Area for dummy cell replacement.

各 FF へのクロック信号遅延時間を CSDP で求め,遅延時間が小さい順に m 個 ( m はパラメータ ) の FF を選択する.選択された FF が含まれる各近傍領域に対してそれぞれ内部の中心に近い最終段パッファセル m 個 ( m はパラメータ ) をダミーセルに置換する.本操作で同一近傍領域内の複数の FF が選択されても,その領域内のダミーセルへの置換は m 個のみとする.

スキュー改善処理は次の 2 ステップからなる . ステップ  $1: m \leftarrow 0.03 \cdot [FF 総数]$  ,  $n \leftarrow 2$  としてダミーセル置換操作を繰り返し実行する .

ステップ  $2: m \leftarrow 1$ ,  $n \leftarrow 1$  としてダミーセル置換操作を繰り返し実行する.

ステップ 1, 2 はともに,目標スキュー値を達成するか,またはスキュー改善幅が指定値以下に収束するまでダミーセル置換操作を繰り返す.この際の CSDP は,高速化のため回路シミュレーションの代わりに AWE 手法 $^{12}$ )を用いて FF の入力端子ノードでの波形を計算する.

最後にトランク配線幅の決め方について簡単に述べる.CCgenへのインプットであるトランク配線幅の値の変動は(1)配線容量によるクロック信号伝播遅延値の増大や(2)エレクトロマイグレーション発生の原因となるが,一方,上記の(1)と(2)は CCgenを実行してクロック分配回路のレイアウトを得た後,初めて CSDP で正確にチェック可能となる.まず,トランク配線を流れる電流値を大雑把に見積もり,エレクトロマイグレーションの制約に基づき配線の幅を見積もる.以下では,垂直トランク配線を例にその手法を示す.クロック周波数を F とし,垂直トランク本数を T とする.最終段トランクバッファの単位時間あたりの消費電力は,貫通電流を無視した場合,充放電電流による要素のみとなり, $1/2(C\cdot Vdd^2\cdot F)$  で表される.

垂直トランク配線 1 本あたりを流れる電流値は近似的に, $1/2(C\cdot Vdd\cdot F/T)$  となる.この値の電流を流してもエレクトロマイグレーションが発生しない配線

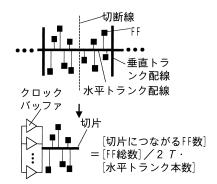

図9 水平トランク切片とクロックバッファ Fig. 9 A trunk wire connected to buffers.

幅を算出し,これを垂直トランク配線幅とする.

この垂直トランク配線幅の計算時点では,まだ配線幅が決まっていないので負荷容量 C は仮の見積り値を用いる.したがって,計算によって得られた配線幅の値を用いて C を更新し,再度トランク配線幅を計算しなおすことが必要である.しかし,数千個以上のFFへのクロック分配回路ではトランクの寄生配線容量値より FFの入力端子容量の総和の方が大きいという我々の経験則を適用すると,この再計算により配線幅の値はほとんど変わらないことが分かり,再計算は不必要となる.

水平トランクの配線幅も、バッファセルが負荷容量の充放電により消費する単位時間あたりの電力と電流値を計算することにより以下のように決定する。図9のように2本の垂直トランク配線に挟まれた水平トランク配線の半分の切片にクロックバッファ群が直接つながる回路に対して垂直トランク配線の場合と同じ手法で算出した電流値を、水平トランク配線を流れる電流であると近似する。この電流値を流してもエレクトロマイグレーションが発生しない配線幅を水平トランクの配線幅とする。

#### 5. クロックスキュー解析ツール CSDP

クロックスキュー解析ツール CSDP は , 現状の技術では最も精度が高い 3D の配線 RC 抽出 $^{13),14}$ と , RC 多段梯子型の配線モデル $^{15)}$  , および BSIM $_3$ トランジスタモデル $^{16)}$ を用いて動的に応答波形を得る SPICE 互換の回路シミュレーションを行う . このうち , クロック分配回路の回路モデル (ネットリスト ) は以下の  $_3$  つの工程で作成する .

- (1) 配線線分の RC 多段梯子型回路の作成

- (2) via hole に対する抵抗素子挿入

- (3) FF の入力トランジスタゲート容量素子の接続

図 10 トランク方式クロック回路の寄生 RC の回路モデル Fig. 10 Parasitic RC networks.

(1)~(3)の工程を説明した図が図 10 である.一般 に,配線を駆動するバッファから次段のバッファ(最終 段は FF の入力トランジスタ )までを , 配線寄生抵抗 3 段以上にモデル化すれば遅延誤差は3%以下であると文 献 15) で実証されている . CSDP はトランク/ブラン チ配線を長さ d ごとに (本評価実験では  $d=100\,\mu\mathrm{m}$ と設定), 分岐と折れ曲り点ごとに, RC1 段の回路に モデル化する.したがって,クロックバッファと FF 間のパスの大部分は RC3 段以上の回路にモデル化さ れ,3%以下の誤差になると考えられる.ただし,例 外的な一部の FF については RC1 段回路にモデル化 される配線長 d 未満の配線を介してクロックバッファ と接続している.その一例は,図10のFFに対し図 中の距離 L と d の間に L < d が成り立つ場合であ る.このような場合も長さLの短い配線の配線遅延 誤差はクロックバッファの無負荷遅延にくらべかなり 小さく無視できるため、3%以下の誤差が保証できる ことを文献 7) で実証した.

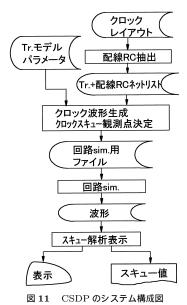

図 11 に CSDP のシステム構成図を示す. 配線 RC 抽出には高精度ではあるが処理時間のかかる米国 EDA ベンダー製の 3D 方式 RC 抽出ツールおよび我々が開発した高速なツール  $HBAgen^{17)}$ を用いている. HBAgenは処理速度が速いことから, CCgenのスキュー改善処理中で CSDP を呼び出すときのみ用いる.

Fig. 11 Processing flow diagram of CSDP.

HBAgen は,スキュー改善処理全体で1回だけ実 行し,ダミーセル置換ごとには HBAgen は再実行し ない、HBAgen を用いる配線 RC 抽出は、処理の高 速化のために以下のようにする. HBAgen はセル間 配線の寄生 RC を抽出する.セル内配線の寄生 RC は 事前に全種類のセルに対し配線 RC 抽出を実行して得 られた値をライブラリとして登録しておき、これを用 いる.このとき,セル上空をある確率で各配線層のセ ル間配線が通過することを想定した近似モデルを用い る . HBAgen によるセル間配線の RC 抽出では , 標 準セルのセル内配線は第1層で敷き詰め詰められてい ると想定して簡単化し,メガセルのセル内配線は実際 の配線パターンどおりとして,セル内配線との間の寄 生容量を計算する.クロックバッファはその形状から の分類で標準セルであるので,ダミーセル置き換え前 後でセル内配線パターンは第1層敷き詰めで変化しな い.このため、HBAgenの再実行は行っても抽出結果 の配線 RC は変わらず,再実行が不必要となる.

CSDP は抽出した配線 RC を MOS トランジスタの接続情報とともに業界標準形式 DSPF で回路シミュレータに渡す・本システムに対し,設計者はクロック波形入力ノードと末端の FF 名,および解析結果の出力形式(3次元表示/リスト出力)を指定するだけでよい・CSDP はクロック波形を生成し,全 FF の入力端子をクロック観測点として,回路シミュレーションの入力ファイルを生成する.

回路シミュレーションが終了すると, CSDP はシ ミュレータの出力波形および入力クロック波形を基に

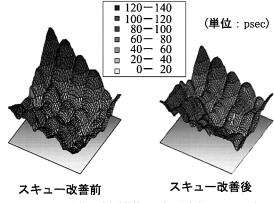

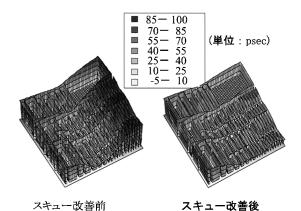

図 12 クロック信号到達時間差の 3 次元分布表示 (LSI 回路 A) Fig. 12 Clock skew analysis results.

各観測点におけるクロック信号遅延値を計算し,指定された形式で出力する.クロックのリング状配線で囲まれた領域を  $64\times64$  の矩形の 2 次元配列に分割してできた各矩形を粗い格子と呼ぶ.各粗い格子に対し,その重心に近い位置に存在する 1 つの FF のクロック入力端子への信号到達時間をその格子の信号遅延とする.CSDP が出力する各粗い格子のクロック信号遅延とそれらの最小遅延値との時間差の 3 次元表示の例を図 12 に示す.これによりクロック分配回路の各ノードの遅延値の分布が明確となり,クロック分配回路の人手修正を容易化する.

# 6. 評価結果

本章は本設計ツールを 100 ~ 200 MHz 級のクロック 分配回路を含む ASIC に適用した結果を示す.

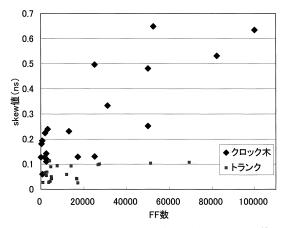

図 13 と表 1 は CCgen と CSDP を用いて設計 した ASIC のクロック周波数とスキュー値を示す. 0.18 CMOS テクノロジの場合, トランクの配線幅は, 下にバッファ回路を置く垂直配線が第3層で, $18.0 \mu m$ , それ以外は第4,第5層で $2.0 \mu m$ である.FFへの支 線の幅は,第1—4層は0.28μmで,第5層は0.5μm とした.また,垂直,水平トランク間隔はそれぞれ  $2,000 \, \mu \mathrm{m}$  以内,  $84 \, \mu \mathrm{m}$  (セルベンチ 10 段相当)以内 と指定した.図13と表1から分かるように,トラン ク方式クロック分配回路は 20,000 ~ 70,000 個の FF を 100 ps 程度のスキューで駆動することができている. CCgen によるトランク方式とクロック木を比較する ために,市販の業界標準ツールAを用いてクロック木 回路を生成した. 本ツール A は文献 3) と同じ範疇に はいる手法を用いてクロック木を生成していると推定 できる.しかし,正確な生成手法が不明であるので, 個々の LSI のクロック回路生成結果に対する詳細かつ

正確な議論は困難であるが,我々が現在までに適用した結果を図 13 に示す.図 13 から分かるように,FF数が 20,000 個以下の場合は,クロック木方式回路でスキュー値  $200\,\mathrm{ps}$  程度を達成できているが,20,000 個を超えると,CCgen によるトランク方式のほうがスキュー値を小さく抑えるのに有効であることが分かる.例として,回路 D に対する本ツール A の実行結果の詳細を表 1 に示す.

次に , FF 配置の疎密に基づく CCgen のバッファ 回路駆動力調整機能の有効性を検証する . 実験に用いた LSI 回路 A , B1 , B2 の FF 数はそれぞれ 69,290 個 , 2,581 個 , 2,822 個で , 垂直トランク配線を 5 本 ,

図 13  $0.25/0.18 \, \mu\mathrm{m} \,$ ルール LSI におけるクロックスキュー値と FF 数の関係

Fig. 13 Relationship between skew and FF count.

2 本 , 2 本敷設している . LSI 回路 A の場合 , 各トラ ンクバッファ回路のバッファセルのカスケード段数は 3 で,各レベルでバッファを8個,30個,520個並列 駆動して回路を構成している. LSI 回路 B1 (B2)の 場合,カスケード段数は2で,各レベルでバッファを 4個,83個(8個,145個)並列駆動して回路を構成 している.この後,AWE 手法により最終段バッファ から各 FF への遅延時間を計算し,遅延最小の FF 近 傍のバッファセルを順次ダミーセルに置換した.この 結果, LSI 回路 A の場合, 755 個のバッファセル置換 後に表 2 のようにスキュー値は , 136 ps/130 ps から 100 ps/97 ps へ減少し (rise/fall), 目標スキュー値を 達成した. LSI 回路 A のスキュー改善処理に要した CPU 時間は 1.9 時間, その後の CSDP の 3D 方式配 線 RC 抽出と回路シミュレーションの CPU 時間はそ れぞれ 33.0 時間 , 4.2 時間 (450 MHz の Ultra SPRC 使用)であった.なお,プリドライブ回路のカスケー ド 段数は 2 で , 各レベルでバッファを 4 個 , 12 個並列 駆動して回路を構成している.回路 B1 と B2 は,同 LSI 上の階層ブロックである.このブロック単位に 相異なる相のクロック信号が供給されている.

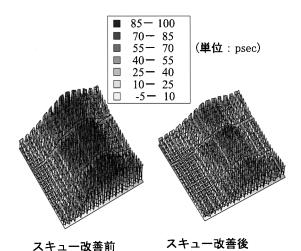

回路 A , B1 と B2 に対するスキュー改善効果を表 2 に示す . そのスキュー改善前後での CSDP によるチップ上に設けた粗い格子単位のクロック信号到達時間と最小遅延時間との差の表示を図 12 , 14 , 15 に示す . 20 3 次元表示では , -般に , 垂直トランク配線部分のノードの遅延は小さいので「谷」として表示され ,

表 1 CCgen を適用した LSI のクロック周波数とスキュー値 Table 1 Resulting values of clock frequency and skew by CCgen.

| LSI名 | 回路規模  | テクノ                | FF数    | 周波数    | クロック | スキュー値        | 最大/最小クロック遅延                         | 最終段バッ | バッファの tpd値   |

|------|-------|--------------------|--------|--------|------|--------------|-------------------------------------|-------|--------------|

|      |       | ロジ                 |        |        | 分配方式 | (rise, fall) | 値(rise, fall)                       | ファ数   | (rise, fall) |

| A    | 1.4MG | $0.25 \mu$ m       | 69,290 | 133MHz | トランク | 100ps, 97ps  | 1.227ns/1.127ns,<br>1.245ns/1.148ns | 2,806 | 208ps, 164ps |

| B1   | 1.2MG | 0.18μm             | 9 501  |        | トランク | 68ps, 70ps   | 0.876ns/0.808ns,<br>0.895ns/0.825ns | 153   | 120ps, 126ps |

| B2   | 1.Zru | υ.10 <i>μ</i> m    | 2,822  | 200MHz | トランク | 54ps, 57ps   | 0.808ns/0.754ns,<br>0.814ns/0.756ns | 221   | 120ps, 126ps |

| C1   | 1.5MG | 0.18μm             | 4,839  | 166MHz | トランク | 81ps, 87ps   | 0.581ns/0.500ns,<br>0.581ns/0.494ns | 308   | 120ps, 126ps |

| C2   | 1.5Mu | υ. 10 <i>μ</i> III | 16,577 | 166MHz | トランク | 48ps, 49ps   | 0.780ns/0.732ns,<br>0.796ns/0.747ns | 608   | 120ps, 126ps |

| D    | 1.5MG | $0.18 \mu$ m       | 82,313 | 120MHz | 木    | 373ps, 505ps | 3.906ns/3.533ns,<br>5.057ns/4.552ns | 2,225 | 438ps, 306ps |

表 2 CCgen スキュー改善機能の適用結果

Table 2 Application results of CCgen skew improvement.

| LSI | 64X64分割領域 | バッファ | スキュー値(       | rise, fall) | 最小遅延値(rise,      | fall)            |

|-----|-----------|------|--------------|-------------|------------------|------------------|

| 回路  | 中のFF数(疎   | の減少数 | 最適化前         | 最適化後        | 最適化前             | 最適化後             |

| A   | 1~51個     | 755  | 136ps, 130ps | 100ps, 97ps | 1.089ns, 1.113ns | 1.127ns, 1.148ns |

| B1  | 0~31個     | 13   | 96ps, 99ps   | 68ps, 70ps  | 0.777ns, 0.793ns | 0.808ns, 0.825ns |

| B2  | 0~33個     | 69   | 92ps, 97ps   | 54ps, 57ps  | 0.712ns, 0.715ns | 0.754ns, 0.756ns |

図 14 クロック信号到達時間差の 3 次元分布表示 (LSI 回路 B1) Fig. 14 Clock skew analysis results.

図 15 クロック信号到達時間差の 3 次元分布表示 (LSI 回路 B2) Fig. 15 Clock skew analysis results.

垂直トランク配線間のノードの遅延は大きいので「尾根」として表示される.トランク間で FF の分布が密の部分が「ピーク」として表示される.この傾向は図 12 において最も顕著である.図 12,14,15 においてスキュー改善によりピークは低く抑えられ,結果として,スキュー値は小さくなっていることが分かる.

#### 7. む す び

本論文では、計算機用回路等の高い周波数のクロック信号を要求される大規模 ASIC 向けに開発したクロック分配回路設計用 CAD システムを提案した、本システムを ASIC 事業に実際に用いており、クロック回路レイアウト設計を自動化している。しかし、まだ適用回路数が少なく、クロック木方式との比較評価が十分ではない、適用回路の実績を積み比較評価することが今後の課題である。

# 参考文献

- Bakoglu, H.B., Walker, J.T. and Meindl, J.D.: A symmetric clock-distribution tree and optimized high-speed interconnections for reduced clock skew in ULSi and WSI circuits, *Proc. IEEE Int. Conference on Computer Design*, pp.118–122 (1986).

- Kahng, A., Cong, J. and Robins, G.: Highperformance clock routing based on recursive geometric matching, *Proc. 28th Design Au*tomation Conference, pp.322–327 (1991).

- 3) Minami, F. and Takano, M.: Clock tree synthesis based on RC delay balancing, *Proc.* 1992 Custom Integrated Circuits Conference, 28.3.1-28.3.4 (1992).

- 4) Tsay, R-S.: An exact zero-skew clock routing algorithm, *IEEE Trans. CAD of ICAS*, Vol.12, No.2, pp.242–249 (1993).

- 5) 荒川隆彦, 奥野義弘, 岡辺雅臣, 大野多喜夫, 蔵満洋一:高性能クロック分配機能付 0.8  $\mu$ mCMOS SOG, 信学技報 VLD 89-103, pp.47-52 (1989).

- 6) 福山弘幸,野村周司,山本一郎: クロックスキュー保証レイアウト手法,信学技報 VLD92-37, pp.13-18 (1992).

- 7) 金本俊幾,柴山泰範,寺井正幸,堀場康孝,外 薗三彦,味岡佳英,岡崎 芳:システム LSI 用ク ロック分配回路設計手法とそのクロックスキュー 解析手法,情報処理学会論文誌,Vol.41, No.4, pp.871-880 (2000).

- 8) 寺井正幸, 八原俊彦: タイミング駆動型ミニカット配置アルゴリズム, 電子情報通信学会論文誌, Vol.J75-A, No.6, pp.1054-1063 (1992).

- Takahashi, K., Nakajima, K., Terai, M. and Sato, K.: Min-cut placement with global objective functions for large scale sea-of-gates arrays, *IEEE Trans. CAD of ICAS*, Vol.14, No.4, pp.434–446 (1995).

- 10) 寺井正幸,佐藤興二,松崎日出夫,高橋一浩:3 層配線ゲートアレイ用グローバル配線の新手法,電子情報通信学会論文誌,Vol.J78-A, No.10,pp.1372-1384 (1995).

- 11) 寺井正幸, 城田博史, 柴谷 聡, 佐藤興二:3層 チャネルレス・ゲートアレイのための高速配線手法, 情報処理学会論文誌, Vol.38, No.3, pp.657-668 (1997).

- 12) Pillage, L. and Rohrer, R.: Asymptotic waveform evaluation for timing analysis, *IEEE Trans. Computer-Aided Design*, Vol.9, No.4, pp.352–366 (1990).

- 13) Akcasu, O.E., Lu, J., Dalal, A., Mitra, S., Lev, L., Vasseghi, N., Pance, A., Hingarh, H. and Basit, H.: "NET-AN" a full three-dimensional parasitic interconnect distributed RLC extrac-

tor for large full chip applications, IDEM 95, pp.19.5.1–19.5.4 (1995).

- 14) Lee, M., Chavez-Reyes, E. and Zorinsky, E.: A reliable traversal clock delay evaluation including input slew effect with 3D parasitic interconnect RLC extraction, *Proc. IEEE Custom In*tegrated Circuits Conference, pp.123–126 (May 1997).

- 15) Sakurai, T.: Approximation of wiring delay in MOSFET LSI, *IEEE J. of Solid State Circ.*, SC-18, 4, pp.418–426 (Aug. 1983).

- 16) Klein, P., Hoffmann, K. and Lemaitre, B.: Description of the bias dependent overlap capacitance at LDD MOSFETs for circuit applications, *IDEM 93*, pp.19.3.1–19.3.4 (1993).

- 17) 小谷 健, 寺井正幸, 高橋一浩, 堀場康孝, 岡崎 芳: ディープサブミクロン LSI 設計にお ける仮想配線容量見積りの精度向上の一手法, 情 報処理学会論文誌, Vol.42, No.4 (2001).

(平成 13 年 9 月 14 日受付) (平成 14 年 3 月 14 日採録)

# 小谷 健(正会員)

平成元年大阪大学基礎工学部情報 工学科卒業.平成3年同大学大学院 修士課程修了.同年三菱電機(株) 入社.以来,LSIの自動レイアウト 技術の研究開発に従事.現在,同社

システム LSI 事業統括部勤務.

# 柴山 泰範

昭和 62 年早稲田大学理工学部電 気工学科卒業・同年三菱電機(株) 入社・以来, LSI の回路設計 CAD 技術の研究開発に従事・現在,同社 システム LSI 事業統括部勤務.

# 岡崎 芳(正会員)

昭和 44 年大阪大学工学部電子工学科卒業.昭和 51 年同大学大学院博士課程修了.同年三菱電機(株)入社.以来,LSIの CAD 技術の研究開発に従事.平成 14 年 4 月より

大阪電気通信大学工学部教授.工学博士.電子情報通信学会会員.

# 寺井 正幸(正会員)

昭和 51 年大阪大学工学部電子工学科卒業.昭和 53 年同大学大学院修士課程修了.同年三菱電機(株)入社.以来,LSIの自動レイアウト技術の研究開発に従事.現在,同社

システム LSI 事業化推進センター勤務 . 工学博士 . 電 子情報通信学会会員 .

#### 堀場 康孝

昭和 39 年名古屋大学工学部電子 工学科卒業 . 昭和 41 年同大学大学 院修士課程修了 . 同年三菱電機(株) 入社 . 以来 , リニア IC , CMOS ディ ジタル IC , バイポーラ/MOS ゲー

トアレイ,ディジタル信号処理 LSI の研究開発に従事. 現在,関西大学工学部教授.工学博士.電子情報通信 学会会員.

# 金本 俊幾

平成元年日本大学理工学部物理学 科卒業.平成3年同大学大学院修士 課程修了.同年三菱電機(株)入社. 以来,LSIの物理検証技術の研究開 発に従事.現在,同社システムLSI

#### 岩出 秀平

昭和 51 年大阪大学理学部物理学 科卒業 · 昭和 53 年同大学大学院修 士課程修了 · 同年三菱電機(株)入 社 · 以来,高速ゲートアレイ回路設計,赤外線イメージセンサ,MOSア

ナログ回路およびシステム LSI の研究開発に従事.現在,同社システム LSI 事業化推進センター勤務.理学博士.電子情報通信学会会員.