1V - 9

# 1ビットフラグ RFID 識別方式における 受信タイミングのずれの影響に関する一検討

中村 有貴 † 藤井 雅弘 † 渡辺 裕 † † 宇都宮大学大学院工学研究科情報システム科学専攻

# 1 はじめに

タグ側で電源を持たないパッシブ型の RFID(Radio Frequency IDentification)システムは ,幅広い用途に用いられ ,物流業界を中心に普及してきている . しかし , ISO/IEC (International Organization for Standardization and International Electrotechnical Commission ) 標準規格の衝突回避技術では ,数百程度のタグ数に対しては高速な処理を望めない可能性がある . そのため ,数百程度のタグ数に対しても ,高速にタグの ID の識別を実現するパケットの衝突回避技術が研究されている . その一つとして , 1 ビットフラグを用いた高速 RFID 識別方式 (1 ビットフラグ方式)が提案されている [1] . 本稿では , 1 ビットフラグ方式において 1 ビットフラグの受信タイミングのずれが生じる際の影響について検討を行った上で , ビットフラグの衝突が発生したときに ,意図的にビットフラグを消失させる高速 RFID 識別方式についての検討を行う .

# 2 RFID における衝突回避技術

#### 2.1 frame slotted ALOHA

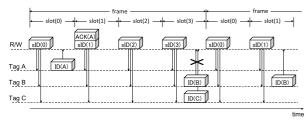

図 1 は frame slotted ALOHA の ID 識別処理における時間軸上での Reader/Writer(R/W) と 3 つのタグのパケットのやり取りの様子を表している. frame slotted ALOHA は 1 フレームを複数のスロットに分割し,各タグがランダムに選択した 1 つのスロットに同期して ID 送信を行う衝突回避技術である. frame slotted ALOHA 方式は,通常の ALOHA 方式よりも効率が良いが,図 1 のフレーム1 のスロット 1,スロット 2 のようにタグからの ID 送信が無いスロットが存在し,そのスロット長分の無駄な処理時間が生じている.

# 2.2 1 ビットフラグ RFID 識別方式

#### 2.2.1 概要

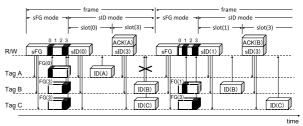

frame slotted ALOHA 方式の無信号区間の無駄を改善するために,1 ビットフラグを用いた高速 RFID 識別方式が提案されている [1]. 図 2 は 1 ビットフラグ方式の ID 識別処理における時間軸上での R/W と 3 つのタグのパケットのやり取りの様子を表している.1 ビットフラグ方式では,各タグの ID を送信するスロットのランダムな選択と,実際に ID を送信するプロセスが,フラグ要請(sFG) モードと ID 要請 (sID) モードに時間軸上で分割され,1 フレームを構成している.R/W はフラグ要請モードにおいて各タグに,ID を送信するスロットを 1 ビットのフラグを送信させることであらかじめ申請させ,ID 要

図 1: frame slotted ALOHA の一例

An Effect of Time Offset in RFID Inventory Method using 1-Bit Flag †Yuki NAKAMURA †Masahiro FUJII †Yu WATANABE †Department of Information Systems Science, Graduate School of Engineering, Utsunomiya University

図 2: 1 ビットフラグを用いた高速 RFID 識別方式

請モードにおいて申請のあったスロットでのみ ID 要請を 行うので,タグからの ID 送信の無いスロットが削減され,frame slotted ALOHA で課題となった無駄な処理時間の削減が可能となる.

#### 2.2.2 受信タイミングのずれによる影響

一般に,パッシブタグは R/W から送信されるパケット に基づいて R/W と同期を取り, 任意のスロットでパケッ トを送信している.しかし,実際の通信環境では,R/W からの信号に対して同期をとって信号を送信したとして も,各タグと R/W 間の伝搬距離差により R/W では受信 タイミングのずれが発生する可能性がある.ここで,1 ビットフラグ方式のフラグ要請モードにおいて,2つの タグが同一スロットのビットフラグを送信した場合を考 える.2つのタグからの信号が全く同時にR/Wに到達す る場合は,衝突となるが,2つのタグ間の伝搬距離差が 搬送波の半波長に一致した場合,それらのタグからの信号は互いに打ち消し合うことになる.したがって,複数のタグからのビットフラグ送信があっても,R/Wではそ れを認識しない場合が発生する、このような場合が発生 すると, R/W は該当するスロットにどのタグからも予約 がないものと判断し、フラグを立てた夕グが存在する場合でも、ID 要請モードで ID 要請を行わない・ビットフ ラグ消失が発生しない場合にはID要請モードでパケット の衝突が発生するが,フラグの消失によって,パケット の衝突のため無駄となるはずであったスロット長分の ID 識別時間が削減される場合がある.

# 3 提案手法

#### 3.1 概要

ここでは、意図的にビットフラグ消失を生じさせる衝突回避技術について提案する.例えば、タグ側で自身の ID の下位 1 ビットが 0 か 1 かに基づいて、通常の ASK100%で変調された信号の位相を反転して R/W に送信する.これにより、2 つのタグが同一フラグビット区間でフラグを立て、R/W と各タグ間の距離差がない場合であっても、1/2 の確率でフラグ消失が発生する.このようにタグの送信位相を適切に操作し、フラグ信号の消失を誘発することで、本来、ビットフラグ消失が発生しない場合であっても、無駄なスロットを削減でき、ID 識別時間を短縮することができると考えられる.

## 3.2 R/W 受信器の構成

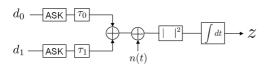

ここで,本研究で想定する R/W の受信器の構成を図 3 に示す.本研究では, R/W での非同期検波を想定する.ここでは, 2 つのタグが存在する場合の例を用いて説明する. 2 つのタグからのそれぞれの送信信号  $d_0$ ,  $d_1$  が ASK

図 3: R/W の受信器の構成

変調され,R/W と各タグ間の距離に基づいた R/W の基準時刻に対する相対遅延時間  $\tau_0$  ,  $\tau_1$  でそれぞれ R/W に受信される.受信信号は受信器で二乗検波され,その出力 z に基づいてフラグの存在判定を行う.

#### 3.3 信号モデル

ビットフラグ消失に基づく提案手法の評価のための信号モデルについて説明する.あるフラグ要請モード期間における第 k タグの送信信号を

$$x_k(t) = \sqrt{P_k} \sum_{k=0}^{L-1} d_{k,k} g(t - uT_b) \cos(2\pi f_c t + \theta_k)$$

(1)

とする.ここで, $\sqrt{P_k}$  は第 k 夕グの送信振幅,L はフラグビット数(スロット数), $d_{ku}$  は夕グの送信ビット,g(t) はビット波形, $T_b$  は1 ビット継続区間, $f_c$  は搬送波周波数, $\theta_k$  は第 k 夕グに割り当てられた送信位相である.この信号モデルでは通常の ASK 信号のモデルに,位相を操作するための  $\theta_k$  を加えている.これより,R/W における第 l ビットのための検波出力は,サンプリング数を  $N_s$  とした台形公式より,

$$z_{l} \approx \frac{T_{b}}{N_{s}} \left\{ \frac{f^{2}(0) + f^{2}(T_{b})}{2} + \sum_{s=1}^{N_{s}-1} f^{2} \left( s \frac{T_{b}}{N_{s}} \right) \right\} + \eta_{l} + n_{l}$$

と書ける。なお、

$$f(t) = \sum_{k=0}^{K-1} \sqrt{P_k} \sum_{u=0}^{L-1} d_{k,u} g(t + (l-u)T_b - \tau_k)$$

$$\times \cos(2\pi f_c(t + lT_b - \tau_k) + \theta_k)$$

(3)

であり, K はタグ数,  $\tau_k$  はタグの R/W からの距離に基づく R/W の基準時刻に対する相対遅延時間,  $\eta_l$ ,  $\eta_l$  は加法性雑音である.式(2)に基づく閾値判定により, 第 l ビット区間でのビットフラグの有無を判定する.

# 4 シミュレーション実験

#### 4.1 評価方法

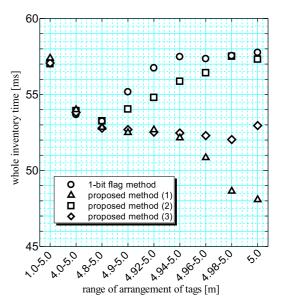

提案方式の評価のため,タグの ID に基づいて操作する送信位相  $\theta_k$  の組み合わせ毎に全タグ ID 識別までの時間を様々なタグの配置環境において検証する.本シミュレーションは雑音,パケットの誤りがない理想的な環境を想定する.送信位相  $\theta_k$  の組み合わせ毎に (1)(2)(3) の提案方式を用意する.提案方式 (1) では, $\theta_k$  にタグの ID の最下位ビットが 0 である場合には 0, 1 である場合には  $\pi$  を与える.提案方式 (2) では,最下位ビットが 0 である場合には  $\pi$  である場合には  $\pi$  、下位  $\pi$  とじットが  $\pi$  である場合には  $\pi$  、「10 である場合には  $\pi$  、「2 を与える.提案方式  $\pi$  のである場合には  $\pi$  、「10 である場合には  $\pi$  、「2 だットブラグ方式と提案方式  $\pi$  のタイムスロット数を  $\pi$  16 とし,本研究で想定する  $\pi$  のタイムスロット数を  $\pi$  16 とし,本研究で想定する  $\pi$  、「5 [m] であるため,タグの配置範囲を  $\pi$  、アクリカル のの通信速度は  $\pi$  、現信速度は標準規格である  $\pi$  、パケットのフレーム構成,通信速度は標準規格である  $\pi$  、 にない、 第6 には  $\pi$  、 第7 にない、 第7 にない、 第7 にない、 第8 には  $\pi$  、 第8 にない、 第9 にない、 第1 にない、 第2 にない、 第1 にない、 第2 にない、 第3 にない、 第4 にない、 第5 にない、 第5 にない、 第6 にない、 第6 にない、 第7 にない、 第6 にない、 第7 にない、 第7

図 4: ID 識別時間の比較

# 4.2 評価結果と考察

(2)

シミュレーション結果を図 4 に示す. グラフの縦軸は 全タグ ID 識別までの時間 , 横軸はタグの配置範囲のパ ターンであり, 図中の点は, 試行回数 1000 回の ID 識別 時間の平均値を意味している.まず,タグの配置範囲が 広く,同一スロットのビットフラグを送信する各タグ間 に生じる伝搬距離差が搬送波の半波長である約 0.16[m] よりも長くなる確率が高い(タグの配置範囲が広い)場 合,提案方式により意図的に位相を操作してもその効果 が得られないため,1ビットフラグ方式と各種提案方式のID 識別時間はほとんど等しい値になっている.次に, 各タグ間に生じる伝搬距離差が搬送波の半波長より短く なる確率が高い(タグの配置範囲が狭い)場合,各方式 で ID 識別時間に差が生まれ,配置範囲が4.94~5.0[m] (0.06[m])より狭い範囲であるとき,提案方式(1)のID 識別時間が最も短くなっている.ここで,ビットフラグ 消失率はタグの配置範囲が狭くなるにつれて,その同一 スロットのビットフラグを送信する各タグに割り当てら れた送信位相  $\theta_k$  に依存する結果となった.この結果から,  $\theta_k$  のパターンが  $0 \ \ \ \ \ \ \$  のみである提案方式 (1) でビット フラグ消失率が高くなり, ID 識別時間が最も短くなったと考えられる.以上より,特にタグの配置範囲が狭い状況では,タグID の最下位ビットが0か1かでタグ送信信 号の送信位相  $\theta_k$  に 0 か  $\pi$  を与える提案方式が高速な ID識別方式として最も有効であると考えられる.

## 5 おわりに

本稿では、1 ビットフラグを用いた高速 RFID 識別方式における受信タイミングのずれの影響について検討し、ビットフラグ衝突が発生したときに意図的にビットフラグ消失を発生させることにより、高速に ID を識別する手法を提案した・また、提案方式について様々なタグの配置環境下における ID 識別時間を計算機シミュレーションにより評価し、1 ビットフラグ方式と比較することでその有効性を示した・今後の課題として、雑音の存在する環境下で提案方式の評価を行うことが挙げられる・

# 参考文献

[1] 亀田 卓,他,"1 ビットフラグを用いた高速 RFID 識別方式",信学論,vol.J89-A,no.12,pp.1057-1067,Dec. 2006