## 4J-3

# FPGA ボード上における 音声データの取り扱い手法に関する検討

正木 範朗 松崎 隆哲‡

近畿大学大学院 產業技術研究科<sup>†</sup> 近畿大学 產業理工学部<sup>‡</sup>

#### 1. はじめに

近年、音声処理技術の高性能化に伴い雑音除去の計算量が増加しているため、ソフトウェアで雑音除去の実時間処理を行うことは困難となっている。実時間の雑音除去を実現する方法としては、高性能なコンピュータを用いて計算時間を短縮する方法とハードウェアで雑音除去回路を構築することで計算の効率化を行う方法の二通りを考えることができる。そこで、本研究ではハードウェアとして FPGA ボードを用いて実時間での雑音除去の実現を目指している。

本研究の目的は、ハードウェアとして FPGA 開発ボードを用いて実時間音声処理回路を構築することである。FPGA 開発ボードで音声データを取り扱うためには、FPGA 上で音声データを扱うためのドライバの構築が必要となる。そのため本研究では、FPGA 開発ボード上に音声データを取り扱うための環境構築を行うことにした。

#### 2. FPGA ボードを用いた音声処理(雑音除去)

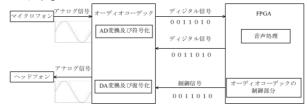

本研究では、マイクロフォンを用いて FPGA ボードに音声データの入力を行い音声処理を行っていく。マイクロフォンから取り込まれた音声データは、アナログデータとして FPGA ボードに取り込まれる。しかし、FPGA ではアナログデータを取り扱うことができないため A/D 変換を行う。また、スピーカーを用いて音声処理後の音声データを出力するが、FPGA から出力される音声データはディジタルデータのため D/A 変換を行う。そこで、本研究では FPGA ボード上のオーディオコーデックを用いて音声データの A/D 変換及び D/A 変換を行う。

FPGA 上に雑音除去回路の構築を行い、オーディオコーデックで A/D 変換されたディジタルデータに対して雑音除去を行う。しかしながら、

Processing techniques of voice handling method on a FPGA board

雑音除去は周波数領域のディジタルデータに対して処理を行うが、オーディオコーデックで扱われるディジタルデータは時間領域のため、時間領域と周波数領域の相互変換を行う回路が必要となる。そのため FPGA を用いた音声処理は、離散フーリエ変換回路と逆離散フーリエ変換回路を FPGA 上に構築し、時間領域と周波数領域の相互変換を行う必要がある。

FPGA とオーディオコーデックの関係図を図 1 に示す。

図 1:FPGA とオーディオコーデックの関係図

### 3. オーディオコーデックを用いた音声データ の取り扱い

本研究では、オーディオコーデックを用いて音声データの取り扱いを行うが、FPGA には音声データを取り扱うためのドライバが搭載されていない。そのため、FPGA とオーディオコーデックの通信に  $I^2C$  を用いて、FPGA にオーディオコーデックの手ライバに相当する制御回路の構築を行った。  $I^2C$  の通信規格に基づいて FPGA からオーディオコーデック内のデータ格納アドレスの指定やデータの書き込みを行うことで、FPGA とオーディオコーデック間の通信を行う事ができ、FPGA 開発ボードでの音声の取り扱いが実現された。

## 4. オーディオコーデックによる遅延状況の調 査

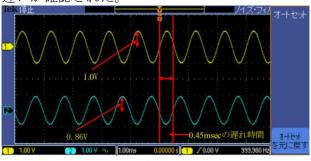

オーディオコーデックを用いて FPGA 開発ボードで音声を取り扱うことはできたが、オーディオコーデックを用いることで音声データにどの程度の遅延が生じるかが不明である。そのため、FPGA ボードの音声入出力ピンに対してオシロスコープを使用することで波形観測を行い遅延時

<sup>†</sup>Noriaki Masaki,Graduate School of advanced technology Kinki University

<sup>‡</sup>Takanori Matsuzaki,Faculty of Humanity-Oriented Science and Engineering Kinki University

間の調査を行った。遅延時間の調査を行うため に、サンプリング周波数 (Fs) を一定に定め、フ アンクションジェネレータから正弦波を入力し、 入力波と出力波の比較を行った。図 2 にサンプ リング周波数を 48kHz と定め、1kHz の正弦波を 入力した場合の入出力波形の比較画像を示す。 入出力の波形を比較したところ、入力波形に対 して出力波形は 0.45msec 遅延していることが判 明し、電圧は 0.86V となっていることが判明し た。同様の測定方法で入力波形を 500Hz とした 場合、遅延時間は 1.424msec、電圧は 0.1V とな り、1KHz の時に比べ遅延時間及び電圧に大幅な 違いが確認された。

図 2:入力波形(上)、出力波形(下)

# 5. オーディオコーデックおける遅延時間とゲ インの周波数特性の調査

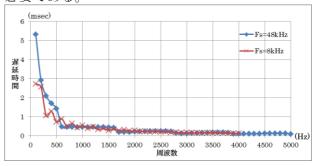

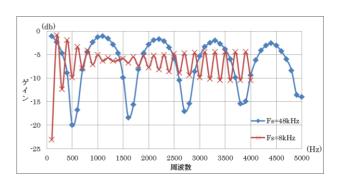

4 章の調査で入力周波数により、遅延時間と電 圧に関して大幅な違いが確認されたため、同様 の測定方法で周波数を 100Hz から 5kHz まで、 100Hz 毎に測定を行い、入力周波数による出力周 波数の電圧変化を明確にするため、電圧をゲイ ンに変換し測定を行った。また、遅延時間やゲ インに関して、サンプリング周波数による変化 を調査するために、8kHz と 48kHz の二つのサン プリング周波数で調査を行った。サンプリング 周波数が 8kHz の場合はサンプリング定理の関係 上、入力周波数の上限を 4kHz として調査を行っ た。図3に遅延時間の周波数特性を、図4にゲ インの周波数特性に示す。

遅延時間の調査では、サンプリング周波数に 関わらず入力周波数が 700Hz 以上の場合の遅延 は 0.5msec 以下で安定しており、700Hz 以下の場 合では遅延が安定しておらず 1~6msec の間の遅 延が生じていることが判明した。また、ゲイン についての調査では、入力周波数によってゲイ ンが大幅に変化することが確認できた。遅延お よびゲインの変化が A/D 変換器と D/A 変換器の どちらに起因するものかが不明である。そのた め、遅延およびゲインの変化の原因の調査およ

びゲインを一定に保つための回路の設計が今後 必要である。

図 3: 遅延時間の周波数特性

図 4: ゲインの周波数特性

### 6. おわりに

本研究では、制御回路の設計、音声データの遅 延調査を行った。オーディオコーデックを用い ることにより FPGA で音声データを取り扱えるこ とは確認できた。また、オーディオコーデック を使用することでの遅延時間の周波数特性とゲ インの周波数特性の調査ができた。

今後の課題としては、オーディオコーデック のゲインを一定にするための回路と音声データ の切り取りための回路を実装が挙げられる。一 定のゲインで音声データを出力することができ、 サンプル毎に音声データの切り取るための回路 を実装することができれば、FPGA 開発ボード上 に音声データを取り扱うための環境構築は整う ことになる。

#### 参考文献

[1] 津城 忠史, 松崎 隆哲: "音声処理システム のハードウェア化に関する検討",火の国情報シ ンポジウム 2009, (2009)

[2] Wolfson microelectronics:

"WM8731/8731L", (2005)

[2] 小林 優: "FPGA ボードで学ぶ組み込みシス テム開発入門",技術評論社,(2011)

[2] 並木 秀明: "改訂新版ディジタル回路と Verilog-HDL", 技術評論社, (2008)