# 低電圧起動回路を用いた省電力チップ間非接触通信回路

佐川 善彦 $^{1,a)}$  廣本 正之 $^1$  佐藤 高史 $^1$  越智 裕之 $^2$

概要:電力制約が大きい恒久保存チップ間の非接触通信の課題として,通信距離の短さ挙げられる.そこで比較的長距離の通信距離が得られる手法として電磁波を用いた手法が注目されているが,他の手法に比べ消費電力が比較的大きくなる問題がある.例としてインバータを用いた増幅回路は簡単な回路で設計が可能であるが,常に動作点バイアスを保持しなければならず,貫通電流が常に流れることで消費電力が大きくなる問題がある.そこで本研究では,通信必要時にのみ動作点バイアスを生成するプリチャージ機構を持つ受信回路とそのプリチャージ信号を生成する起動回路を提案する.シミュレーションにおいて 1 mmの通信距離を確認し,プリチャージ機構を持たない非接触通信回路の平均消費電力を,通信時には約2分の1,待機時には4桁削減できることを示した.

## 1. はじめに

近年,チップ間における非接触通信の需要が高まっている.使用用途はIC タグのデータ読み取り,センサネットワーク,無線通信や本研究グループが提案している恒久保存メディア [5] への応用など多岐にわたる.恒久保存メディアとは超長寿命デジタル記憶媒体のことであり,記憶部として半導体集積回路メモリの一種であるマスク ROMを用い,二酸化ケイ素でメディア全体を覆う構造を持つ.チップ間の非接触通信によりメディア同士での通信が可能となり,管理コストの削減やアーカイブとしての拡張性の向上が期待される.

本稿では電力制約の大きい恒久保存メディアにも応用できるようなチップ間の非接触通信回路を目指す.一般的にチップ間での非接触通信では面積の制約が大きい.これらの制約を満たす既存研究の課題として通信距離の短さが挙げられる.Digital Rosetta Stone [6] はコイルを用いた電磁誘導結合により非接触通信を達成しているが,通信距離は0.2 mm 程度とほぼ密着させなければ通信が行えず,安定性の面で実用的ではない.そこで電磁波を用いた非接触通信手法が提案されており [2],非接触通信の中でも比較的長距離の通信を行えることが期待されている.ただし電磁誘導結合等の他の非接触通信方式に比べ消費電力が比較的大きくなる欠点がある.

1 京都大学大学院情報学研究科

Graduate School of Informatics, Kyoto University

<sup>2</sup> 立命館大学情報理工学部 College of Information Science and Engineering, Ritsumeikan University

a) paper@easter.kyoto-u.ac.jp

そこで本研究では電磁波非接触通信手法によるチップ間 非接触通信を省電力に実現することを想定する.受信回路 における増幅回路としてよく使用されるインバータ増幅回 路は簡単な構造で増幅が可能であるが,以下のような問題 がある.

- 通信待機時においても受信信号を検知するために動作 点バイアスを生成し続ける必要があり,貫通電流が常 に流れるため消費電力が大きくなる.

- 増幅用とバイアス生成用のインバータが異なるため製造ばらつきの影響により動作点バイアスがずれるおそれがある.

本稿では、一時的に増幅用のインバータの入出力を短絡することで動作点バイアスを生成するプリチャージ機構を持つ増幅回路を提案する.この増幅回路により通信待機時の貫通電流は大きく削減されることが期待される.また,入力と出力を短絡して動作点バイアスを生成する際にはプリチャージ信号を ON にする必要がある.ここで微弱な受信信号を検知する起動回路を提案する.この回路もってプリチャージ信号を入力し,増幅回路を作動させる.

本稿ではプリチャージ増幅回路,また起動回路を含む非接触通信回路の設計を示し,その動作をシミュレーションによって示す。またインバータ増幅回路とプリチャージ増幅回路それぞれを用いた場合での消費電力の内訳を示し,通信時の平均消費電力を約2分の1,待機時の平均消費電力を4桁削減できていることを示す。

本稿の構成は以下のとおりである.まず,2章で非接触通信手法や提案回路に関わる既存手法について検討,説明し,3章で提案する非接触通信回路の設計について各回路

ごとに説明をする .4 章でシミュレーションによる回路の動作や消費電力の内訳 , またその評価を行い ,5 章で結論を述べる .

# 2. 既存手法

本章では提案回路における非接触通信手法,また起動回路で用いるレベルシフタの既存手法について述べる.

#### 2.1 非接触通信手法

電力制約の厳しい環境下でのチップ間通信という観点において注目されている手法として電磁結合誘導によるもの [6], 電磁波によるもの [1] 等が挙げられる.以下にそれぞれについて検討を行う.

## 2.1.1 電磁誘導結合によるもの

受信側と送信側にコイルを設けてこれらを接近させると,これらの間に電磁誘導結合が生じるので,これを利用して通信を行うことができる.この手法を用いてチップ間通信を実現させた例として Digital Rosetta Stone がある [6] . 報告によれば直径 0.4 mm のコイルで 0.2 mm の通信距離が確保できたとされている.ただし,この手法は通信距離の変化に非常に弱い.磁界は距離の 2 乗に比例して減衰するため,送受信ポートの距離が少しでも開いてしまうと通信が途絶えてしまうおそれがある.

## 2.1.2 電磁波によるもの

電磁波は適切なアンテナを用いることにより遠距離まで信号を伝えることが可能である.この手法を LSI チップに使用した例として [1] が挙げられる.アンテナのサイズを  $4\,\mathrm{mm}$  程度と,LSI チップ内のメタル配線層を利用して実現が可能であり, $1\,\mathrm{mm}$  程度の通信が可能であるとされている.消費電力が容量結合方式や電磁誘導方式に比べ比較的大きくなってしまうが,安定した通信が見込めるという点で,本研究が想定する環境下ではこの手法が最も適していると考えられる.

送信に使用できる電磁波の周波数はアンテナの長さに依存するため,面積制約の厳しい LSI チップでの実装においては極めて高い周波数となってしまう.一般に LSI チップ上にてリングオシレータ等の発振器で高い周波数を生成することは難しい.そこで,LC 共振回路に急峻なステップ波形を入力することで共振を引き起こし,変圧器を用いてその振動を取り出すことによって高周波数信号の生成を可能とする [2].この機構をショックウェーブジェネレータ(SWG) と呼ぶ.

またアンテナの共振周波数が低いほど長距離通信には有利である.ここで有効なアンテナの種類として,メアンダ状ダイポールアンテナが挙げられる[3].このアンテナはダイポールアンテナを折り返す形状を持ち,ダイポールアンンテナのサイズを小さくしつつ,標準的なダイポールアンテナと同程度のアンテナ特性が期待される.

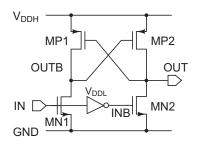

図 1 典型的なレベルシフタの回路図

#### 2.2 レベルシフタ

典型的なレベルシフタの回路図を図1に示す.レベルシフタとは,振幅の小さいディジタル信号を必要とされる振幅まで引き上げて出力する回路を指す.ここで,入力振幅と出力振幅はそれぞれ $V_{DDL}$ と $V_{DDH}$ によって決定されるが, $V_{DDL}$ が小さく $V_{DDH}$ 高い場合,特にサブスレッショルド領域を扱う場合にはうまく動作しない.図1における出力電圧 OUT は MP2 と MN2 が駆動する電流で決まる.電圧 IN が H のとき,MN2 が On となるが,特にサブスレッショルド領域の場合, MN2 に流れる電流が極めて小さくなり,強反転領域での MP2 に流れる電流のほうが大きくなる.このとき電圧 OUT はプルダウンされず,レベルシフタは正しく動作しない.

幅広い入力電圧に対応し、かつ低消費電力で動作するレベルシフタとして、大崎レベルシフタが提案されている [4] . 回路図を図 2 に示す . この回路は大きく分けてレベルコンバータとカレントジェネレータの 2 つの回路で構成されている .

まず図 2 のレベルコンバータについて説明する.出力電圧 OUT は MP6 と MN8 が駆動する電流で決定される.ここで MN8 が駆動する電流は,差動増幅回路とカレントミラーによって MP3 が駆動する電流となる.ここで,MP3 と MP6 はどちらも MP2 に流れる電流に依存するため,どちらも駆動する電流は同じとなり,前述した典型的なレベルシフタのような問題は発生しない.

次にカレントジェネレータについて説明する.この回路は入力電圧 IN と出力電圧 OUT の論理値がそれぞれ異なる場合にのみ MP2 を駆動させることで,不必要なときにレベルコンバータが動作しないように設計されており,レベルシフタが動作する時以外での消費電力を大幅に削減することができる.

出力電圧を立ち下げる場合は  $I_F$  , 立ち上げる場合は  $I_R$  を生成して  $\mathrm{MP2}$  を駆動する .

# 3. 非接触通信回路設計

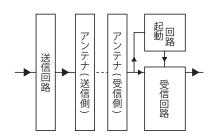

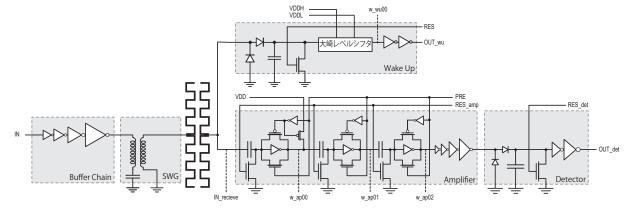

提案する非接触通信回路のブロック図を図3に示す.この非接触通信回路はアンテナ,送信回路,受信回路,起動回路で構成される.ここで,本研究では送信回路の入力信

図 2 大崎レベルシフタの回路図 [4]

図 3 非接触通信回路のブロック図

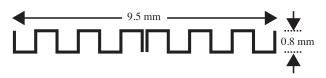

図 4 設計したアンテナの概要図

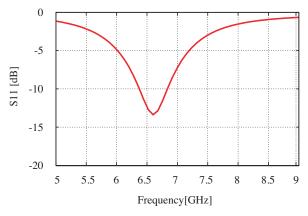

図 5 アンテナ性能

号,受信回路の出力信号はともにデジタル信号であると想定する.以下にそれぞれの回路設計について述べる.

#### 3.1 アンテナ設計

本研究において設計を行ったアンテナを図 4 に示す.本研究では電磁場解析ソフト Femtet を用いてアンテナ形状を検討した.アンテナサイズを  $10\,\mathrm{mm}\times1\,\mathrm{mm}$  に固定し,折り返し回数を 3 回から 13 回まで変化させ,それぞれについてシミュレーションを行ったところ,折り返し回数が 6 回の形状のとき最も低い共振周波数が得られた.この時のアンテナ形状を図 4 に示し,性能を図 5 に示す.

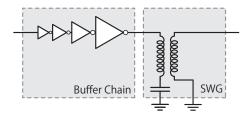

図 6 送信回路の回路図

## 3.2 送信回路設計

図 6 に送信回路の回路図を示す.この送信回路はバッファチェーンと SWG で構成される.

2.1.2 節で述べたように , 高周波信号は SWG にステップ波形を入力することで生成される . ここで入力信号はデジタル信号であるため , 01 もしくは 10 のビット列が入力された場合にそのエッジに応じたパルスが生成されることになる . このとき生成される信号の振幅は , 入力信号のスルーレートに依存し , スルーレートが大きいほど振幅は大きくなる . そこで , SWG の入力にバッファチェーンを挿入し , よりスルーレートの大きい信号が入力されるように設計を行った .

また, SWG で生成される信号の周波数は, 3.1 節で述べたアンテナの共振周波数に合わせるように設計を行った.

# 3.3 受信回路設計

受信回路は増幅回路と検波回路で構成される.

## 3.3.1 增幅回路

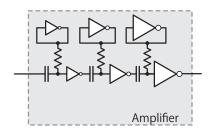

増幅回路には CMOS インバータを反転増幅器として用いる手法が考えられる.インバータ増幅回路の回路図を図7に示す.ここではインバータ増幅回路を3段用いている.

CMOS インバータを増幅器として利用するためには、入力信号の電圧を増幅動作領域まで引き上げる必要がある。ここでは増幅器としてのインバータと同じ入出力特性を持つインバータを用意し、このインバータの入力と出力を短絡することで、増幅動作領域の中心の電圧を得ている。この電圧を入力信号にバイアスすることで増幅回路として機能させる。ただし、インバータの入力と出力を短絡した状態は、貫通電流が流れ続けることとなるために通信時、待機時の消費電力が極めて大きくなってしまう。また製造ばらつきの影響で同じ入出力特性のインバータを用意するこ

図 7 インバータ増幅回路の回路図

図 8 プリチャージ増幅回路の回路図

#### とは難しい.

そこで本研究ではプリチャージ増幅回路を提案する.プリチャージ増幅回路の回路図を図8に示す.プリチャージ増幅回路を3段用いており,増幅回路の出力に駆動用のバッファチェーンを挿入している.

この増幅回路の特徴は,増幅動作領域まで引き上げるた めに必要なバイアスを,増幅回路として使用するインバー タ自身で生成するという点である.こうすることで製造ば らつきに関係なく、正確に増幅動作領域まで引き上げるバ イアスを生成することが可能となる.また消費電力の点で もプリチャージ増幅回路は有効である.動作点バイアスを 生成する際にはプリチャージ信号を一定期間 ON にするこ とでインバータの入力と出力を短絡し,動作点バイアスを 放電するときは RES\_amp 信号を ON にする.こうするこ とで,通信時にのみ増幅回路が動作し,待機時の電力を大 幅に削減することが可能となる、ここで初段のプリチャー ジ増幅回路には PMOS トランジスタを挿入した.このイ ンバータで動作点バイアスを生成した場合, 増幅動作領域 のちょうど真ん中に引き上げられることになるため信号未 入力状態がノイズに敏感になる.これを防ぐために小さな PMOS を初段に挿入し,若干の偏りを持たせた.

ここで本研究が想定する入力電圧は非常に微弱であるため, CMOS インバータの機構を3段とした.

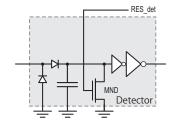

# 3.3.2 検波回路

図 9 に検波回路の回路図を示す.

図中のダイオードは順方向の電圧降下が比較的小さくスイッチング速度の速いショットキーバリアダイオードである.コンデンサで整流後の入力電圧を保持し,その後インバータによって波形の整形を行う.また,コンデンサの電荷を放電するための MND を加えた.ここで検波後の出力信号を確認する度に RES\_det 信号を一時的に ON にし,MND で入力容量の電荷を引きぬくことで次の入力信号に

図 9 検波回路の回路図

図 10 起動回路の回路図

備えるようにする.

#### 3.4 起動回路設計

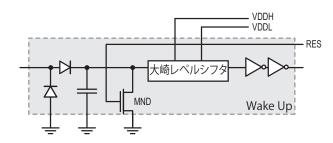

3.3.1 節で述べたように,プリチャージ増幅回路を動作させるためには PRE 信号を生成する起動回路が必要である.この起動回路を実現する機構として,2.2 節で述べた,低入力電圧に対応し低消費電力で動作する大崎レベルシフタを用いる.

起動回路の回路図を図 10 に示す.回路の動作を述べる.入力信号はまず整流回路によって整流され,その後コンデンサに電荷が蓄えられる.一定の電荷が蓄えられると大崎レベルシフタが動作し,VDDHまでレベルシフトされた信号が出力される.その後インバータで整形する.

大崎レベルシフタの設計にあたって,特に注意しなければならないのは初段のインバータの動作である.大崎レベルシフタは図 2 における電圧 IN, INB が決定していなければ正しく動作しない.本研究が想定する環境では入力電圧がサブスレッショルド領域内であることが予測されるため,電圧 IN の論理値に応じて,電圧 INB が大崎レベルシフタの動作に影響のない範囲で反応できているか確認する必要がある.また,大崎レベルシフタの入力容量の電荷を放電するための MND を加えた.

# 4. 評価

## 4.1 増幅回路

プリチャージ増幅回路を用いた場合の通信回路の動作に ついてシミュレーションを行った.

#### 4.1.1 シミュレーション環境

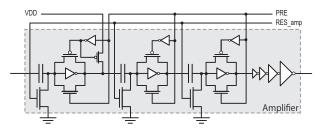

通信回路の全体構成を図 11 に示す.図 11 はバッファチェーンと SWG から構成される送信回路に入力信号を入力し,アンテナを通じて起動回路,また増幅回路と検波回

図 12 増幅回路動作,増幅回路電源波形

路からなる受信回路が接続されており,アンテナで受信された信号が増幅される様子を確認することを目的としている.

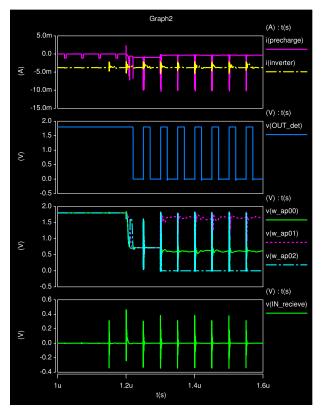

シミュレーションには回路シミュレータ HSPICE を用いた.入力信号は  $20 \mathrm{MHz}$  の矩形波とし,時刻  $1.1~\mu\mathrm{s}$  より入力を開始するものとした.ここで入力信号が入力されていない状態を待機状態,入力信号が入力されておりかつ受信回路が機能している状態を通信状態とする.PRE 信号は時刻  $1.2 \mu\mathrm{s}$  から時刻  $1.3 \mu\mathrm{s}$  の間 ON とし,RES\_det はOUT\_det が立ち上がって  $20 \mathrm{ns}$  後に  $5 \mathrm{ns}$  の間 ON する信号を外部から印加している.アンテナの回路モデルはアンテナ特性を表す  $\mathrm{S}$  パラメータより得られる Touchstone ファイルを使用している.ここでは通信距離を  $1 \mathrm{mm}$  としてモデル化している.電源電圧は  $1.8 \mathrm{V}$  とする.

## 4.1.2 シミュレーション結果

図 12 に図 11 中の各ノードにおける電圧波形を示した.図 12 におけるノード w\_ap00 から w\_ap02 までを見ると,PRE 信号が ON となっている 1.2µs から 1.3µs の間の電圧が 0.8 程度となっており,各増幅回路において動作点バイアスを生成していることがわかる.PRE 信号が再び OFFとなる 1.3µs 以降では増幅回路として機能し,振幅 0.4V 以下の入力信号 IN\_recieve を 1.8V にまで増幅できていることがわかる.受信回路の出力であるノード OUT\_det を見ると,増幅回路がプリチャージし始めた時点より,入力信号のパルスに応じたディジタル信号を得ている事がわかる.

図 13 回路起動時の動作

### 4.2 起動回路

3.4 節で述べた起動回路の動作についてシミュレーションした.

## 4.2.1 シミュレーション環境

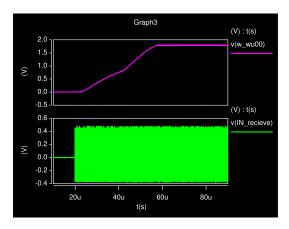

シミュレーション回路図は図 11 と同様である.ここで VDDH は電源電圧と同じ 1.8V とし,VDDL は 0.2V とした.送信側の入力信号には時刻  $20~\mu s$  より,20MHz の矩形 波を入力した.

## 4.2.2 シミュレーション結果

図 13 に , 起動回路の入力であるノード  $IN\_recieve$  と大崎レベルシフタの出力であるノード  $w\_wu00$  の電圧波形を示す . 観測している時間スケールが大きいためノード  $IN\_recieve$  の電圧波形がつぶれているが , 図 12 の信号入力時における  $IN\_recieve$  の電圧波形と同様のものである .

図 13 より,起動回路に入力が開始された時刻 20µs より徐々に電荷が蓄えられ.時刻 60µs 頃に VDDH の電圧である 1.8V にまでレベルシフトしてることが確認できた.このレベルシフトに必要な時間は入力信号の振幅に依存する.アンテナの通信距離が長くなるにつれ入力信号の振幅は減少するため,起動回路が動作することが保証される範囲で通信距離を決定する必要がある.

## 4.3 消費電力

インバータ増幅回路とプリチャージ増幅回路それぞれを 用いた場合の消費電力の比較を行った .

インバータ増幅回路を用いた通信回路は図 11 における プリチャージ増幅回路を図 7 のインバータ増幅回路に置き 換えたものであり,と同条件でシミュレーションを行った.

図 13 にプリチャージ増幅回路とインバータ増幅回路それぞれを用いた場合についての、増幅回路電源の電流波形を示した.これら i(precharge) と i(inverter) について検討する.i(inverter) では通信時、待機時の状態に関わらず常に消費電流が 3mA 以上流れていることがわかる.これは常に動作点バイアスを生成しているためである.一方i(precharge) では 1.2 ps までの待機時にはほぼ電流が流れ

図 11 通信回路の全体構成

表 1 平均消費電力の比較

| F = 1 3/1322 B/3 10 201X |      |           |            |

|--------------------------|------|-----------|------------|

| 状態                       | 回路   | インバータ [W] | プリチャージ [W] |

| 通信時                      | 送信回路 | 1.22e-03  | 1.60e-04   |

|                          | 受信回路 | 2.89e-03  | 8.08e-04   |

|                          | 起動回路 | -         | 4.86e-06   |

|                          | 全体   | 4.10e-03  | 9.74e-04   |

| 待機時                      | 送信回路 | 1.20e-09  | 1.86e-09   |

|                          | 受信回路 | 3.79e-03  | 1.37e-07   |

|                          | 起動回路 | -         | 8.92e-09   |

|                          | 全体   | 3.79e-03  | 1.47e-07   |

|                          |      |           |            |

ておらず, $1.2\mu s$  から  $1.3\mu s$  の間のプリチャージ期間より入力信号のパルス時のみ電流が流れていることがわかる.またプリチャージ OFF 後である  $1.3\mu s$  以降における信号未入力時の消費電流がi(inverter) に比べ大きく抑えられている.これは各増幅回路の電圧が動作点パイアスに完全に固定されていないために 3.3.1 で述べた初段増幅回路の偏りに応じた論理値が出力されるようになり,貫通電流がほぼ流れなくなったためであると考えられる.

表 1 より , プリチャージ増幅回路によりインバータ増幅 回路を用いた場合よりも , 通信時の全体平均消費電力を約 2 分の 1 , 待機時の全体平均消費電力を 4 桁削減できてい ることがわかる .

# 5. まとめ

本稿では電磁波非接触通信手法によるチップ間非接触通信を省電力に実現することを想定し、プリチャージ機構を持ち通信時にのみ動作点バイアスを生成する増幅回路,また微小な入力信号を検知しプリチャージ信号を入力する起動回路を含む非接触通信回路を提案した.提案通信回路における、プリチャージ増幅回路と起動回路の動作を HSPICEシミュレーションを用いて確認し、通信距離 1mm の場合において通信回路が機能することを示した.また提案するプリチャージ増幅回路により、通信回路全体の平均消費電力がインバータ増幅回路を用いた場合に比べ、通信時には約2分の1,待機時には4桁削減できることを示した.

謝辞 本研究は JSPS 科研費 23300015 の助成を受けた.

また本研究は東京大学大規模集積システム設計教育研究センターを通し,シノプシス株式会社および日本ケイデンス株式会社の協力で行われた.

## 参考文献

- [1] Iwata, A., Sasaki, M., Kikkawa, T., Kameda, S., Ando, H., Kimoto, K., Arizono, D. and Sunami, H.: A 3D integration scheme utilizing wireless interconnections for implementing hyper brains, Solid-State Circuits Conference, 2005. Digest of Technical Papers. ISSCC. 2005 IEEE International.

- [2] Khanh, N. N. M., Sasaki, M. and Asada, K.: A fully integrated shock wave transmitter with an on-chip dipole antenna for pulse beam-formability in 0.18-  $\mu$ m CMOS, 2011 16th Asia and South Pacific, Design Automation Conference (ASP-DAC), pp. 107 –108 (online), DOI: 10.1109/ASPDAC.2011.5722161 (2011).

- [3] Moriyama, W., Kubota, S., Kimoto, K., Sasaki, N. and Kikkawa, T.: On-chip Micro-meander-antennas for silicon LSI wireless interconnects, Antennas and Propagation Society International Symposium, 2008. AP-S 2008. IEEE, pp. 1–4 (online), DOI: 10.1109/APS.2008.4619465 (2008).

- [4] Osaki, Y., Hirose, T., Kuroki, N. and Numa, M.: A level shifter circuit design by using input/output voltage monitoring technique for ultra-low voltage digital CMOS LSIs, New Circuits and Systems Conference (NEW-CAS), 2011 IEEE 9th International, pp. 201–204 (online), DOI: 10.1109/NEWCAS.2011.5981290 (2011).

- [5] Shinya Matsuda, Takashi Imagawa, H. T. T. S. Y. N. and Ochi, H.: Architecture for Sealed Wafer-Scale Mask ROM for Long-Term Digital Data Preservation, The 28th International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC), pp. 321– 324 (2013).

- [6] Yuxiang, Y., Miura, N., Imai, S., Ochi, H. and Kuroda, T.: Digital rosetta stone: A sealed permanent memory with inductive-coupling power and data link, VLSI Circuits, 2009 Symposium on, pp. 26 –27 (2009).