ノーマリーオフコンピューティング

# 携帯情報端末における ノーマリーオフコンピューティン

STT-MRAM で実現するノーマリーオフメモリ技術

安部恵子 野村久美子 藤田 忍 野口紘希 (株) 東芝 研究開発センター LSI 基盤技術ラボラトリ

# 不揮発メモリのプロセッサ応用は 消費電力増大を招く?

#### 不揮発メモリをプロセッサ内に

高性能の汎用プロセッサや SoC (System on Chip)は、さまざまな改良により、高性能化と低 消費電力化を進めてきているが、改善の度合いが 徐々に縮小してきている。携帯情報端末向けのプロ セッサは、従来低消費電力重視の設計がされてきた. しかし、タブレット PC やスマートフォン等の高性 能化が進む中、動作周波数が増加し、消費電力も増 え、汎用プロセッサと同じ状況を迎えつつある、携 帯情報端末を構成する部品のうち消費電力が特に大 きいのは、ディスプレイ、無線通信部品、そしてプ ロセッサの3つであるが、今後の消費電力の増大 という観点では、最もリスクが大きい部品はプロセ ッサであると考えられる.

現状、プロセッサ性能の対電力効率を上げる設計 技術として、使用していない回路ブロックを電源 遮断するパワーゲーティング(PG)の高効率化と、 プロセッサコアのマルチコア(MC)化の2つが主 に進められている. 最先端高性能プロセッサでは, PG の空間・時間粒度を細かくすることで、待機電 力の消費を効率的に削減している。しかし、PGで メモリ回路やレジスタの電源を遮断すると、データ が消失するため、PG 細粒度化が進むほど、メモリ 部の消費電力が相対的に目立ってくる、後述するよ

うに、メモリ部の数は年々急増しているため、電力 削減のターゲットは明らかである.

筆者らは、2004年頃より、スタンフォード大学 と共同で、メモリ回路やレジスタに Spin Torque Transfer Magnetic Random Access Memory (STT-MRAM) や ReRAM 等の不揮発メモリを適 用して、PG ベースに高性能ロジック回路の待機電 力を削減することを提案し、その効果を分析してき た<sup>1)</sup>. 当時はまだ PG の具体的な実装技術がない 時代であったが、将来の PG を予測しつつ理論検討 を進めていた. さまざまな不揮発メモリを比較した ところ、用途によって各不揮発メモリの適・不適 があることが分かった。たとえば、2004年より 前に FeRAM を用いた不揮発回路が報告されてい たが<sup>2)</sup>、FeRAM の書き換え回数の上限などから、 動作頻度が高いプロセッサには適していない。比較 分析の結果、高い処理性能と低消費電力を同時に追 及するプロセッサ用途には、STT-MRAM が適し ており、ほかには候補がないことが分かった。まず、 STT-MRAMのメモリ技術について簡単に説明する.

#### 高速不揮発メモリ STT-MRAM

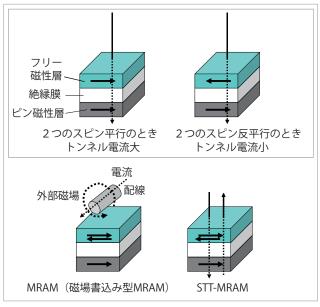

MRAM は、図 -1 で示すように Magnetic Tunnel Junction (MTJ) という2種類の異なる磁性 体薄膜で薄いトンネル絶縁膜を挟み込んだ構造の素 子を用いた不揮発メモリである<sup>3)</sup>. 磁性体薄膜の 一方はピン層と呼ばれ、スピンが安定で半永久的に 変化しない、もう一方は、フリー層と呼ばれ、ある

# 3. 携帯情報端末におけるノーマリーオフコンピューティング

STT-MRAM で実現するノーマリーオフメモリ技術

図-1 MRAM の原理と 2 種類のデータ書込み方式

エネルギーを与えるとスピンの向きが反転するよう な材料が選ばれる、2つの層のスピンの向きが同じ ときと反対のときとで、絶縁膜を流れるトンネル電 流が受ける電気抵抗が異なる.これを利用してフリ -層のスピンの向きを電気的に読み取り、不揮発メ モリとして用いる.

MTJの近くに設けた配線に電流を流し磁場を発 生させることでフリー層のスピンを反転することが できる。100MHz 超の高速メモリアクセスが可能 で、書き換え耐性(Endurance)が 10<sup>15</sup> 回以上で ある. この高速性と高い Endurance がほかの不揮 発メモリと著しく違う点であり、ワーキングメモリ に適している。半導体集積回路(CMOS)の配線 層内に磁性体をインテグレーションすることができ るため、微細化に適している.

単に MRAM と表記されたメモリは、磁場書込み 型のものを指す. この MRAM は、配線電流の消費 電力が大きく、微細化の阻害要因となる。これに対 して、STT-MRAM と呼ばれる MRAM は、電流の 流す方向を変えることで、スピンの向きが変えられ るメモリである. 原理的にスピンを反転する電流密 度は一定であるため、素子サイズを 1/X に微細化 すると、素子の面積が $1/X^2$ になり、書込み電流が 1/X だけ小さくなる. このため、微細化によるス ケーリングメリットが得られる。STT-MRAM が

電流書込み型であるため、SRAM や CMOS の配線 層中に MTJ を配置し、配線を流れる電流の向きを 変えることで STT-MRAM のデータを書き換える ことができる、これは、CMOS 回路内部に不揮発 メモリを混載することができることを意味する。配 置する場所によって速度、面積、消費電力にトレー ドオフが見られ、さまざまな回路を検討した(詳細 は後述)、さらに、これらの不揮発回路を使って消 費電力を削減することを検討した。2008年頃より、 性能、電力をシステムレベルで定量的に評価し始め たところ、予想に反してかなり難解であることが判 明してきた. "不揮発メモリは、静的(待機)消費 電力が小さいが、動的消費電力が巨大であり、結果 的に総消費電力が増大する"という"不揮発メモリ のジレンマ"のためである(筆者らが文献3)にて問 題提起)、このジレンマを超えることがいかに難し いか、次の不揮発キャッシュメモリの事例を用いて 解説する.

#### 不揮発メモリのジレンマを超えるには?

STT-MRAM は、まず DRAM ベースのメインメ モリを置き換えることが期待される不揮発メモリで ある。年々、動作速度も増加しており、メインメモ リより上のメモリ階層となる SRAM ベースのキャ ッシュメモリの置き換えが次に期待される。このと き、消費電力を大幅に下げられるかどうかがポイン トとなる、大きな消費電力削減がないと、不揮発メ モリを使う意味がなくなるからである.

モバイル機器を想定し、バッテリの消耗を抑え るには、消費電力というよりも消費電力量(消費 電力x消費する時間)を抑える必要がある. よっ て、消費電力を下げると同時に高速で書き込める素 子を作らなければならない。 従来の MRAM もしく は STT-MRAM では、磁性層のスピンが平行面内 磁化膜が用いられていたため、Write の消費電力が 大きく、大容量化を阻んできた。2007年に垂直磁 化型の STT-MRAM (perpendicular-STT-MRAM, 以下 p-STT-MRAM と略す)が東芝によって初め て開発され<sup>4)</sup>,消費電力と書込み時間を大幅に下

# 小 特 集 ノーマリーオフコンピューティング

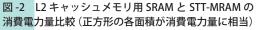

図-3 STT-MRAM の Write 電流と時間の報告例 等高線上は消費電力量が同じで、左下ほどエネルギーが低い

げることが可能となった。最近、ほかの研究機関より、垂直磁化 STT-MRAM で、同様のスペックのものが発表されている。

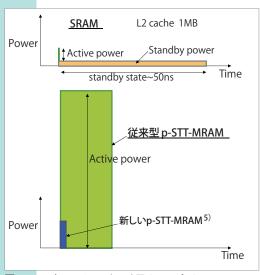

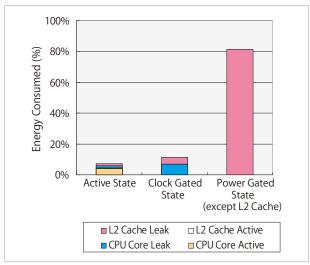

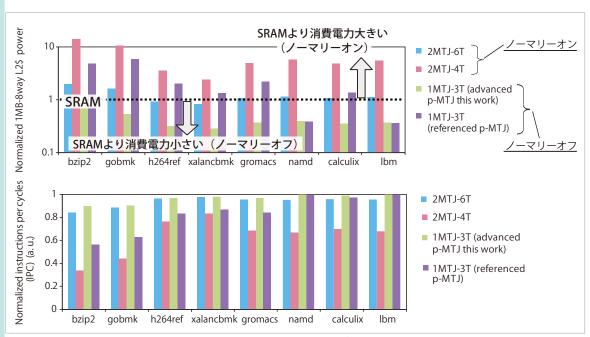

ここで、ハイエンドクラスの 40nmCMOS テクノロジの ARM 系プロセッサを想定し、SRAM とSTT-MRAM の 1 MB クラスの L2 キャッシュメモリの消費電力エネルギーを比較してみた(図 -2)、プロセッサのシミュレータを用いて、ベンチマークソフトを動かして、L2 キャッシュの平均的な Write アクセス間隔を調べると、約 50 サイクル(50ns@1GHz)程度となった。この間キャッシュメモリ全体は約 3mW の待機電力を消費する。一方動的電力(動作メモリは 64B=512b)は約0.5mW だが、その時間は 0.3ns 未満に過ぎないため、待機電力エネルギが支配的となり、トータルで150pJ のエネルギーが消費される。

一方、STT-MRAM ベースのキャッシュでは、周辺回路を含め待機電力を百μW 未満まで下げることが可能となる. しかし、従来 p-STT-MRAMでは、典型的な値として Write 電流が 100 μ A で、Write 時間が 15ns 程度必要となり、結果1,500pJ 消費し、プロセッサのバッテリ消費量が従来よりも 10 倍多くなってしまう. さらにキャッシュメモリの Write 速度も 10 倍以上低下し、プロセッサの演算性能にも影響する. これではコストをかけて新しいメモリデバイスを導入する意味がまっ

たくない。STT-MRAMでは、Write速度を上げるためには、Write電流を増やす(消費電力を増やす)必要がある。逆に、書込み電流を減らすと書込み速度が低下するという、トレードオフ関係があり、いずれもSRAMのエネルギーの壁を破れない。この状況を図-3に示した。

これに対して、最近、東芝の STT-MRAM 研究 グループより汎用低消費電力 SRAM よりも低消費電力となり得る、3ns、 $30\mu$ A で Write できる低消費電力の STT-MRAM 技術(サブ 30nm  $\phi$  MTJ)が報告された 51. これは、図 -3 に示すとおり、キャッシュメモリ低消費電力化の壁を破る初の技術である。

しかし、図-3の例より低消費電力のSRAMも広く使われており、そのSRAMも置き換えるためには、STT-MRAMの動的電力を下げるだけでは限界がある。加えて重要な点は、電力削減に効果的な部分のみを不揮発化させるようなメモリ階層化構造を考え、これを最も効率よく動作させるための回路・システムのハードウェアを設計すること、さらにこのハードを効率よく用いるためのプロセッサアーキテクチャを考案することである。これらを揃えることで、ノーマリーオフ化による超低消費電力プロセッサの実現に近づいていく。今回、主に回路・システムの設計について紹介する。

図-4 モバイルプロセッサの各状態と消費電力エネルギー (= 時間×消費電力)の比率(全消費エネルギーを 100%とする)

# モバイルプロセッサ向けノーマリー フ型回路・システム設計

#### どのメモリ階層を不揮発化すべきか?

まず、低消費電力化のためには、メモリ階層のど の部分を不揮発回路に置き換えるべきかを調べた. 図 -4 に、ケーススタディとして、クロックゲーテ ィングと PG を最大限に活用して電力削減するモバ イルプロセッサの各省電力ステート(クロックゲー ティングと、L2キャッシュメモリ以外のPG)で の累積消費エネルギーを示す.

このユースケースは、ユーザの長期待機状態を含 んでいるので、全体の 95% の時間帯が L2 キャッ シュのみに電力供給されるステートとなっている. ただし、待機時間が 100 µs より長い場合は、従来 型 PG により電力を 100 µW 未満にすることがで きる. PG できないのは、100 μs 以下のオーダの 短い時間帯での待機状態で、これはアプリケーショ ン動作中の待機状態である。この L2 キャッシュの アプリケーション動作中の待機電力が消費電力量の 累積値は全体の80%に及ぶ。一方、L1キャッシ ュメモリを含むプロセッサコアは、PG の効果によ り、待機電力消費が少ない、つまり、プロセッサ内 のキャッシュメモリが消費電力エネルギー量を支配 していると言える. ちなみに, これはモバイルプロ

セッサならではの傾向であり、サーバ向けやハイエ ンド PC 向けのプロセッサでは、プロセッサコアを PG できる頻度が下がるため、プロセッサコア側に 消費エネルギーの分布が偏り、プロセッサコア動作 時の電力が全体の消費電力量を支配する傾向となる. さて、モバイルプロセッサのキャッシュメモリの 容量が近年急増する傾向にある。この理由は、温度 上昇の問題から周波数を高められない状況の中、微 細化に伴って増えるトランジスタ資源をキャッシュ メモリに割り当てているためである。これにより単 純にプロセッサコアから見てメモリアクセススピー ドが増すことにより、プロセッサの処理性能が向上 する。また、前述のマルチコア化により、キャッシ ュメモリ、特に共有キャッシュメモリとなる Last Level Cache (LLC) の容量が増え続けている。よ って、キャッシュメモリの待機電力が、プロセッサ の消費電力エネルギーを支配している。もし、キ ャッシュメモリを不揮発にすることで 100 µs 以 下のオーダの短い時間帯の待機電力を削減できれば、 大きな電力削減効果が期待できるということになる が、これはもちろん容易ではない.

従来の大容量 STT-MRAM に使われる 1 MTJ-1T型, またはその類似の回路では, 読み出し・書 込み速度が SRAM よりも遅い、そのために、速度 を上げるための回路的な工夫が必要となる、次節に て、SRAM キャッシュ並みの動作速度を持つ不揮 発 SRAM 回路の検討について紹介する。

#### ハイブリッド型/不揮発 SRAM

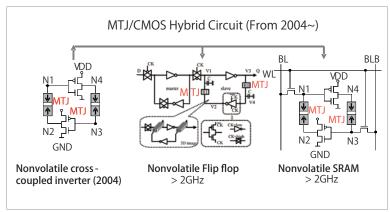

筆者らは、2004年にSTT-MRAMとインバー タをそれぞれ2個ずつクロスカップルさせた,不 揮発ラッチ回路を提案した(図-5)<sup>1)</sup>. 2個のイ ンバータのクロスカップル型 CMOS 回路は,フリ ップフロップや SRAM などの内部に含まれる 1 ビ ットメモリの基本回路であり、それの内部に対称に MTJ 素子 2 個を接続させた回路が不揮発ラッチで ある. これを使うと、図-5のようにフリップフロ ップや SRAM を不揮発にできる.

一般的な不揮発型回路では、STT-MRAM に毎

ノーマリーオフコンピューティング

回データを書込み、それを読み出す ため、CMOSのフリップフロップ と比較してメモリ動作が遅くなって しまう問題があった. これに対して, この不揮発ラッチ回路は, 通常動作 時に通常の SRAM やフリップフロ ップとして高速動作することが可能 である。そして、電源遮断する前に、 2個のMTJに同時に相補的にデー タを書込み、データを格納する(ス トア動作). さらに、電源復帰時に

は、2個の MTJ の抵抗値の違いによって、電源遮 断時前のデータが自動的に CMOS のラッチ回路に 戻される(リコール動作)仕組みである。1つの回 路を揮発回路と不揮発回路に使い分けられる。これ によって、動作時に毎回 MTJ に書込みしないため、 MTJ の書込み電力エネルギーを小さくできる.

通常フリップフロップまたは SRAM として動 作する間、インバータ間に流れる電流は MTJ を Write できる値よりも小さく  $(<<30\mu A)$ , かつ, 流れる時間も短い (<1ns, 1GHz) ので, MTJ内 のデータは書き換えられることがない.

フリップフロップや SRAM を置換する効果を明 らかにするために、"不揮発化による消費電力削減 の損益分岐時間 (Breakeven Time for Replacement by Nonvolatile devices = BT)"を見積もる ことが有効である。この損益分岐時間 (BT) は、"待 機状態での消費エネルギー=電力遮断に必要なオー バヘッドエネルギー"から定義され、フリップフ ロップや SRAM の場合, "1 ビットのフリップフ ロップまたは SRAM の待機電力× BT=1 ビットを MTJ に格納するための電力エネルギー(Write エ ネルギー)"の式から計算できる。40nm CMOSの 標準的なリーク電力と、垂直磁化 STT-MRAM の 損益分岐時間を計算すると、1 ビットのフリップフ ロップまたは SRAM を 1 ビットの不揮発フリップ フロップまたは不揮発 SRAM で置き換えるための BT は、約数百 $\mu$ s ~数 ms のレンジとなる. この 時間よりも長い待機時間の間 PG を続けないと、電

図-5 不揮発クロスカップルインバータを不揮発 SRAM と不揮発フリップフロッ プに適用

力削減につながらない. システムクロックが 1 GHz のプロセッサを考えると、十万サイクルオーダ以上 と、かなり長い待機状態に相当する、これでは、ア プリケーション動作中の短い待機時間 (< 100 μs) で PG すると、逆に電力増大を招いてしまう、従来 の CMOS/SRAM 回路製品では PG は数十~数百 μs 程度の待機時間で行っている。これは、従来型 のほうが電源遮断復帰が高頻度で効率よく(電力削 減率が高くなるという意味で)行えることを意味し ている. しかし、キャッシュメモリの動作を考える と、動作するメモリビット数と、待機状態のメモリ ビット数とで、桁違いに差があるため、実質的に BTが何桁も小さくなり、キャッシュメモリの電力 が削減することが可能になる<sup>6)</sup>. 次にそれについ て説明する.

## Breakeven Time はメモリファクタ分 短縮する

待機状態でリーク電力を生じているのは全部のメ モリであるが、電源復帰時から遮断時までの間に書 込みされるメモリは、全メモリの一部だけである. (書込みされるメモリのビット数) / (メモリの全 ビット数)の比率を"メモリファクタ"と呼んでお り<sup>7)</sup>,BT はメモリファクタ分、オーダで短縮され る. たとえば、1MBのキャッシュメモリがある場合、 64B が書き換えられるとすると、メモリファクタ は 6.4x10<sup>-5</sup>で、実効的な BT は 4 桁以上も小さく なる、大容量のキャッシュほどメモリファクタが小

## 3. 携帯情報端末におけるノーマリーオフコンピューティング

STT-MRAM で実現するノーマリーオフメモリ技術

| Memory<br>Hierarchy         | Volatile<br>Circuit    | NV-<br>Circuit  | Memory<br>factor     | BT<br>case1<br>(Advanced p-<br>STT-MRAM) | BT<br>case1<br>(General p-<br>STT-MRAM) | T (Typical<br>Stand by Time<br>during Write<br>Operation) |

|-----------------------------|------------------------|-----------------|----------------------|------------------------------------------|-----------------------------------------|-----------------------------------------------------------|

| Registers<br>In CPU<br>core | Flip flop              | NV-Flip<br>flop | -                    | 120us                                    | 4ms                                     | <1~2ns                                                    |

| Register<br>File            | SRAM                   | NV-<br>SRAM     | -                    | 120us                                    | 4ms                                     | <1~2ns                                                    |

| L1<br>Cache                 | SRAM                   | NV-<br>SRAM     | -                    | 120us                                    | 4ms                                     | 3~5ns                                                     |

| L2<br>Cache<br>(1MB)        | SRAM<br>(Low<br>power) | D-MRAM          | 6.4x10 <sup>-5</sup> | 7.7ns                                    | 240ns                                   | ~50ns                                                     |

表-1 各メモリ階層におけ る BT とアプリケーション動 作中の待機時間 T

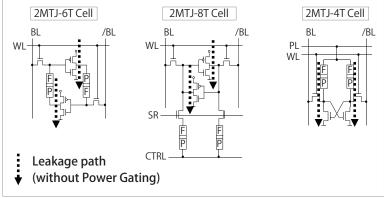

図 -6 不揮発 SRAM 回路の例. すべてにリークパスが存在

さくなり, BT が小さくなる. ゆえに, メモリ階層 の下側ほど、電力削減の機会が増えるということに なる.

表 - 1 に各メモリ階層で予測される BT を記載し た、また、アプリケーション動作中に、各メモリが 待機状態となる時間間隔の平均値 T も示した.

T>BT という状況であれば、アプリケーション 動作中でも不揮発キャッシュ導入によって電力削 減できることになり、理想的な Run-time Power Gaiting を実現する可能性が生まれる。表 -1 を見 ると、L1 キャッシュメモリ以上では、T<<BT とな っており、ここに不揮発 STT-MRAM を適用する と、電力増大を起こすことが分かる、高速動作が必 要なため、不揮発 SRAM を用いる必要があり、メ モリファクタ効果が得られないという背景がある. 逆に、L2(またはL3)キャッシュを不揮発化する ことが電力削減に効果的となることが分かる.

どのメモリ階層を不揮発化すべきか?でプロセッ サコア内のメモリは、もともと待機電力の寄与が小

さいため, 不揮発化の効果が小さ いこと, L2, L3 キャッシュは待機 電力が支配的で、キャッシュメモリ 容量増大化により、待機電力がより 大きな問題となることを述べた. こ れらの理由とBTの長さの両面から、 L2以下の下層のキャッシュメモリ 不揮発化が、モバイルプロセッサの 消費電力削減に有効であることが分 かる.

このようにメモリファクタによる BT 改善のため に空間粒度・時間粒度を細粒度化することになる. このような、細粒度実装の場合、回路オーバヘッド とその分の遅延オーバヘッドの比率が、粗粒度より も指数関数的に大きくなる. キャッシュメモリのよ うな SRAM 領域はチップ全体の半分近くを占める ものが多いので、このオーバヘッドはチップコスト にも大きく影響する。 さらに電源 On・Off による 不安定性増加も問題となる。もっとシンプルな回路 システム、理想的には PG なしで電力削減できる回 路が望まれる.

そもそもの問題点は、図-6に示すように、不揮 発 SRAM では、クロスカップルインバータの部分 が常にリーク電流パスとなっているため、メモリ セルを PG しない限りリーク電流を防ぐことができ ない、つまり、メモリが「ノーマリーオン」状態な のである. 筆者らが提案した6トランジスタ (6T) 型の不揮発 SRAM 以外に, 8T 型<sup>8)</sup> (図 -6), 5 T 型<sup>9)</sup>、4T型<sup>10)</sup>(図-6)等さまざまな回路が提案

されているが、いずれも SRAM 回路を含むノーマ リーオン型メモリ回路である。ノーマリーオフ型メ モリ回路に改良できれば、PG フリーでオーバヘッ ドなしにすることができる.

# PG 有のノーマリーオンメモリ回路から PG フリーのノーマリーオフメモリ回路へ

DRAM を置き換えることが期待されている大容 量向けの STT-MRAM のメモリセル回路は、セル 面積が小さい1トランジスタ+1メモリ素子型で あり、この回路にはリークパスがないことが知られ ている. つまり, ノーマリーオフ型メモリである. しかし、残念ながら、この回路では読み出し書込 み速度が汎用 DRAM 並みにはなるものの、SRAM には遠く及ばない.

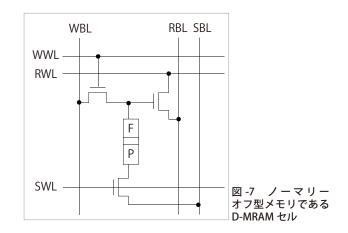

そこで図 -7 のような、新しいノーマリーオフ型 の D-MRAM 回路を考案した 11). この回路は, 3つ のトランジスタと 1 つの MTJ からなる. 3 つのト ランジスタのゲート容量とドレイン容量がキャパシ タンスとして働く、このキャパシタンス容量は汎用 DRAM のキャパシタンス容量よりも桁違いに小さ いため、リテンション時間は 10 μs 程度で短いも のの、その分書込み速度も速い、DRAMと MRAM

のハイブリッド回路として、DRAM または MRAM のどちらかとしてメモリ回路を任意に使い分けるこ とができる。キャッシュに格納するデータで格納す べき時間が短くてもよいデータは、DRAM に格納 し、格納すべき時間が長いものは MRAM に格納す るというふうに使い分けることで、高速で低消費電 力の動作が可能である. プロセッサアーキテクチャ の観点から、どう使い分けるのがより効果的かも細 かく分析している <sup>12)</sup>

不揮発キャッシュメモリを搭載したプロセッサの 性能と電力を計算する環境を整備し、SPEC2006 ベンチマークソフトを用いて、性能と消費電力を SRAM キャッシュのプロセッサと比較した. 図 -8

不揮発 SRAM と D-MRAM(1MTJ-3T)を L2 キャッシュに用いたプロセッサの消費電力(L2 部)と性能 縦軸は SRAM との相対比較(6T 型は粗粒度 PG でメモリファクタは 1. 4T 型は 32 ビット細粒度 PG)

図-9 CMOS のみで実 現できる待機電力がほ ぼ 0 の厚膜 CMOS ハイ ブリッド回路

にその結果を示す. 性能劣化が最小限に抑えられ て、電力が大幅に改善することを示した。この D-MRAM メモリは、動作時以外はメモリセルのリ ーク電力が発生しないので、PG は不要である。よ って、アクセス動作が完了した途端に遅延0で電 力遮断状態と同様の状態に戻ることになる. さらに、 アクセス部分しか電力消費しないので、1 ビット細 粒度のメモリシステムになる、最も無理のないメモ リ回路である.

なお、BT を短縮化し、低消費電力化するため の、もう1つ重要な点は、MTJを格納するための Write 動作時の消費電力が増大しないような回路 設計である。ほかから提案されている 4T 型不揮 発 SRAM では、メモリセル小型化を優先した結果、 残念ながら貫通電流が流れたままになるため、メ モリセルが動作するときの消費電力が SRAM より 100 倍以上大きくなってしまっている。 したがっ て、細粒度 PG を用いて、待機電力を 0 にするこ とができたとしても、動作時電力が100倍以上増 大するため、トータルとして、従来型 SRAM キャ ッシュよりも数倍~10倍程度消費電力が増大して しまうことが図 -8 の結果から分かる。これも不揮 発メモリのジレンマである。このように、トータ ル電力の考慮が求められるため、不揮発回路設計 は難解であり、本当に効用がある回路は限られて いる.

# ハイブリッド型不揮発フリップフロップ 回路の応用

次に、不揮発ラッチの SRAM 以外の応用として、 不揮発フリップフロップ(図-5)について考察する. フリップフロップ,特に D型フリップフロップは, 同期式順序回路として、プロセッサコア内のパイプ ラインレジスタや、バス回路、メモリのバッファな どに広く使われている。近年、類似のハイブリッド 型の不揮発フリップフロップ回路がほかのグループ から報告されている <sup>13)</sup>.

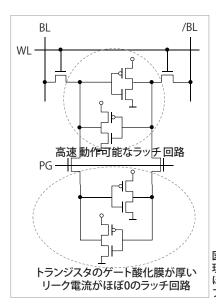

BT を計算すると、前節同様に約数百 µs ~数 ms のレンジとなる. フリップフロップは 1 ビットメ モリなのでメモリファクタ効果もない、前述したと おり、従来型のほうが電力削減率が高くなり、最先 端技術を駆使して不揮発素子を導入する意義がない. そもそも、同様のハイブリッド回路は、ゲート酸化 膜の厚いトランジスタを使った CMOS 回路で構成 するラッチ回路をフリップフロップや SRAM に接 続することでも実現できる(図-9)、この場合、面 積は同等で、リーク電流を100分の1以下に低減 できるため、待機電力が無視できるレベルでデータ を保持でき、不揮発にほぼ近い、STT-MRAMを 外部接続したハイブリッド回路より、この"厚膜 CMOS ハイブリッド型"回路の方が明らかにコス トパフォーマンスが高い(STT-MRAM を外付け するタイプの不揮発 SRAM も同様).

STT-MRAM の不揮発フリップフロップの方が フリップフロップの動作頻度がもっと低い応用に適 しているという考え方もある。しかし、このような 場合、STT-MRAM のような動作電力が大きい不 揮発素子よりも、前述した FeRAM のように動作 電力が低い不揮発素子(すでに製品化)の方が明ら かに有利である。かくして、STT-MRAM不揮発 フリップフロップの有望な用途は現状見つかってい ない

# 電圧引加型 MTJ は SRAM を超えられ るか?

近年、電圧引加型 MTJ に関する基礎研究が注目

# ormally-Off Computing 小特集 ノーマリーオフコンピューティング

されている <sup>14)</sup>. これは電流を流さずに MTJ のス ピンを反転するもので、原理的には低消費電力に なり得る. しかもスピン反転速度が "SRAM 並み" に高速である. 筆者らは, L1 キャッシュ向けに電 圧引加型 MTJ を想定して先の 6T- 不揮発 SRAM を電圧引加型に改良した回路も提案している 15). 高速動作主体での応用なので、待機電力よりも動 作電力が支配的となる.動作電力は ½ xCV²+ItV となる。CはMTJの容量や周囲の配線の容量, It はMTJをトンネルする電流. 現状 ▽ が大きい MTJや、Itが大きい実験例(事実上の電流書込 み)が多く、動作電力は SRAM よりも遥かに大きい. ある程度高速になると、メモリ部分より配線部分の 遅延で支配されるため、実際には SRAM より高速 に動作させることは無理である. しかし、SRAM と対等な高速性と動作電力を持つ不揮発 RAM が使 えるようになれば、高速で低消費電力の L1 キャッ シュメモリが実現できる。今後の電圧引加型 MTJ の研究進展が期待される.

#### まとめ

携帯情報端末のモバイルプロセッサの消費電力を削減するためにSTT-MRAMをメモリに導入する方針について解説した。通常STT-MRAMを実装すると、消費電力増大の弊害を招くため、L2キャッシュまたはラストレベルキャッシュに、ノーマリーオフ型のD-MRAMメモリ回路を使うことを考案した。これにより、アプリケーション動作中のごく短時間待機時の電力もほぼ0することができ、プロセッサの消費電力を大幅に削減でき、ノーマリーオフプロセッサ実現に近づく。さらなるメモリ開発の進展と、新たなプロセッサアーキテクチャにより、完全なノーマリーオフプロセッサの実現も可能になっていくことが期待される。

#### 参考文献

1) Abe, K., et al.: European Micro and Nano Systems

- 2004, 20-21th October, Paris, France (2004), Abe, K., Fujita, S. and Lee, T. H.: 2005 NSTI Nanotechnology Conference, Vol.3, pp.203-206 (2005).

- Fujimori, Y., et al.: Technical Report of IEICE. ICD2002-10.

- 3) Ando, K., et al.: Roles of Non-Volatile Devices in Future Computer System: Normally-off Computer, ISBN978-1-4666-1842-8 (June 2012).

- 4) Yoda, H., et al.: 7th International Workshop on Future Integration Process Technology (2007).

- 5) Kitagawa, E., et al.: 29. 4, Technical Digests of IEDM (2012).

- 6) Abe, K., et al.: SSDM, pp.1144-1145 (2010).

- 7) Yoda, H., et al.: 29. 4, Technical Digests of IEDM (2012).

- 8) Yamamoto, S., et al.: Jap. J. Appl. Phys. Vol.48, 4, 2009. 090204/1 (2010).

- 9) Fujita, S., et al.: Japanese Patent P2011-166070. US and Chinese patent (2011).

- 10) Ohsawa, T., et al. : Jap. J. Appl. Phys. 51 (2012) 02BD01.

- Abe, K., et al.: 10.5 in Technical Digests of IEDM (2012).

- 12) Noguchi, H., et al.: To be Presented in Design Automation and Test in Europe (Mar. 2013).

- Masui, S., et al.: IEEE 2003 Custom Integrated Circuits Conference (2003), Sakimura, N., et al.: IEEE 2008 Custom Integrated Circuits Conference (2008).

- 14) Maruyama, T., et al.: Nature Nanotech. 4, 158 (2009), Nozaki, T., et al.: Appl. Phys. Lett. 96, 022506 (2010), Shiota et al.: Nature Mat. 11, 39 (2012), Nozaki, T., et al.: Nature Physics, Volume:8, pp.492–497 (2012).

- 15) Fujita, S., et al: GF-05, The 12th Joint MMM/Intermag conference (2013). (IEEE Trans. Mag. in printing)

(2013年3月5日受付)

謝辞 本研究成果の一部は、NEDO「ノーマリーオフコンピューティング基盤技術開発プロジェクト」によるものである。また、STT-MRAM を使った新しいプロセッサアーキテクチャの研究は、同プロジェクトにおける東京大学 中村宏教授のグループとの共同研究にて進行中である。

#### 藤田 忍 I shinobu.fujita@toshiba.co.jp

1989 年東京大学工学部博士課程修了、同年(株)東芝入社、東芝研究開発センターにて、次世代不揮発性メモリの回路・システム応用の研究・開発に従事。

#### 安部恵子 │ keiko2.abe@toshiba.co.jp

岡山大学卒業. 次世代不揮発性メモリの回路・システム応用の研究・開発に従事.

#### 野村久美子(正会員) kumiko.nomura@toshiba.co.jp

2005 年東京工業大学院理工学研究科集積システム専攻、博士課程修了、同年より(株)東芝研究開発センターに勤務現在に至る。主にアーキテクチャの研究に従事。

#### 野口紘希 | hiroki.noguchi@toshiba.co.jp

2006 年神戸大・工・情報知能卒業. 2011 年同大大学院工学研究科情報知能工学専攻博士課程修了. 現在, 東芝研究開発センターに勤務. 工博. 計算機アーキテクチャの研究に従事.