# 電力モード協調によるプロセッサと主記憶の省電力化の検討

宮 創 <u></u>† 沂 章 部 藤 正 孝 多 弘 樹 和  $\blacksquare$ 康 本

## 1. はじめに

近年、半導体の微細化にともない、プロセッサのリーク消費電力の増大が問題になっている。また、計算機システムの主記憶装置として通常用いられているDRAMデバイスもアクセスが行われていない際の消費電力が多く、その電力削減が課題となっている。本研究では、プロセッサ待機時のリーク電力削減手法としてパワーゲーティング(PG)を、DRAMの待機時電力削減手法としてDRAMデバイスに備わる低電力モードを利用することを前提とし、両者のの電力モード管理を協調して行うことで、従来よりも効率的に消費電力を削減することを目指す。

#### 2. 電力モードの協調

## 2.1 L2 キャッシュミス時における協調

通常の DRAM の場合、メモリアクセスが無い場合には省電力効果は低いが、省電力モードからの復帰が高速な Fast Exit モードを利用することが一般的である。本電力モード協調手法では、ラストレベルキャッシュミスなどによりプロセッサが長期間ストールする場合には、使用してない DRAM ランクをそれらのランク内のデータがアクセスされるまで電力削減効果は高いが復帰に時間がかかる Slow Exit モードや Self Refresh モードへ移行させる。これにより、大幅な性能低下を防ぎつつ、電力削減効果を高めることができると期待される。

#### 2.2 DRAM リフレッシュ時における協調

DRAM がリフレッシュ中はプロセッサから当該 DRAM デバイスへのアクセスはできない。そのため、主記憶アクセスが頻発するプログラムでは、リフレッシュ中プロセッサを強制的に省電力モードにすることで、性能低下を防ぎつつリーク電流を削減することができると考えられる。

#### 3. 評 価

シミュレータ MARSSx86 with DRAMSim $2^{1/2}$  を用い、評価を行った。ベンチマークプログラムにはSPEC-CPU2006 の中から 6 つ選択し、使用した。各

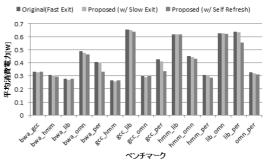

図 1 2 コアでの DRAM の平均消費電力

## 4. ま と め

本研究ではプロセッサと主記憶の省電力モードを協調させることで、電力を削減する手法を提案した。評価を行った結果、従来手法に比べ平均消費電力を削減できる可能性があることを示した。しかし、キャッシュミス時における協調では大幅に実行時間が増加する場合があった。そのため、メモリアクセス頻度によって使用する省電力モードを変更するなどの改良が必要だと考えられる。

### 参考文献

- 1) MARSSx86:http://marss86.org/

- 2) Paul Rosenfeld, Elliott Cooper-Balis, Bruce Jacob, "DRAMSim2: A Cycle Accurate Memory System Simulator", Computer Architecture Letters, pp16-19,2011

<sup>†</sup>電気通信大学大学院情報システム学研究科