## 負論理実装を可能とする 新型光再構成型ゲートアレイ VLSI

## 森脇烈† 渡邊実†

今我々は、高速再構成と大規模な回路情報の記憶が可能な動的再構成デバイスである光再構成型ゲートアレイの開発を進めている。本稿では明点ビット数の最小化により再構成の高速化が可能な新しい VLSI チップと、その効果について報告する

# New optically reconfigurable gate array VLSI to enable a negative logic implementation

Retsu Moriwaki<sup>†</sup> and Minoru Watanabe<sup>†</sup>

Up to now, as one of multi-context devices, an optically reconfigurable gate array (ORGA) has been developed to achieve high-speed reconfiguration and to provide numerous reconfiguration contexts. For an acceleration method by reducing the number of bright bits, we have developed a new ORGA VLSI-chip. This paper presents reconfiguration acceleration results on the new ORGA-VLSI chip.

#### 1. はじめに

近年、家電、携帯電話、産業用ロボットなどさまざまな用途に組込みシステムが用いられており、年々、より高い性能が求められるようになっている。これまでの組込みシステムは、主に、ASIC (Application Specific Integrated Circuit) で構成されてきた。しかし、ASIC は特定の用途に対して高い性能を発揮するが、開発費や開発期間が多大であることが問題であった。

そこで近年ハードウェアをソフトウエアのように書き換えることが可能なプログラマブルデバイス、FPGA (Field Programmable Gate Array) に注目が集まっている[1][2]. プログラマブルデバイスではハードウェアの仕様を容易に変更できるので,他品種,少量生産に最適であること,また,開発工数を大幅に削減できるメリットがある. FPGA は通常,不揮発性の外部メモリとセットで用いられる. 電源起動時に外部メモリに蓄えられた回路情報を FPGA 内部のメモリにシリアル転送し,FPGA のゲートアレイは動作する. ここで,もし,この外部メモリを大容量化すれば,大規模な回路情報を蓄えることも可能になる. しかし,一般に,FPGA の性能は,ゲートアレイをプログラマブルにしていることから,ASIC と比較して低い. よって性能の改善が課題であった[3].

プログラマブルデバイスの性能を改善するためには、プログラマビリティーの積極的な活用しかない.ある瞬間に必要な回路のみをプログラムし、ゲートアレイ上で実行し、不必要な回路を取り除き続けることで、ゲートアレイの利用効率を最大限まで高める手段が有効である.しかし、この実現のためには、高速再構成と大量の回路情報の保持が必須条件となる.しかし、FPGA内への回路情報はシリアル的に転送しているので、回路実装に数十msから数百msの時間を要する.高速な動的再構成は難しい.

そこで我々は高速再構成が可能なプログラマブルデバイスである光再構成型ゲートアレイを研究開発している[4][5][6]. 光再構成型ゲートアレイはレーザアレイ, ホログラムメモリ, 光再構成型ゲートアレイ VLSI で構成される. 光再構成型ゲートアレイでは次世代の光メモリである3次元ホログラムメモリに回路情報を蓄える. レーザアレイの各レーザとホログラムメモリ内の各回路情報は一体一対応となっており, 所望の回路情報に対応しているレーザを点灯させるだけでその回路情報を読み出すことができる. 回路情報は完全並列の2次元回折パターンで転送されるため高速な再構成が可能である. このように, 光再構成型ゲートアレイは高速再構成と大規模な回路情報の保持が可能で, 仮想的に大規模なゲートを実現することが可能になる.

<sup>†</sup> 静岡大学工学部電気電子工学科

Shizuoka University Electric and Electronic Engineering

このように高速再構成は光再構成型ゲートアレイの重要なファクターであり、これまでに、より高速な再構成を実現するために明点ビット数の最小化による高速化手法を提案してきた[7][8]. この度、その高速化手法を効率的に実装できる新設計の光再構成型ゲートアレイ VLSI を開発した. 本稿では、その VLSI を用いて、明点ビット数の最小化による高速化手法の有効性を示す.

#### 2. 光再構成型ゲートアレイ

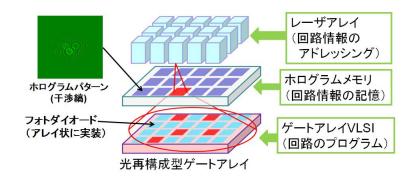

図1 光再構成型ゲートアレイの基本構成

#### 2.1 光再構成型ゲートアレイ

光再構成型ゲートアレイの基本構成を図1に示す。光再構成型ゲートアレイはレーザアレイ、3次元ホログラムメモリ、光再構成型ゲートアレイ VLSI で構成される。回路情報は3次元ホログラムメモリ内に干渉縞の形で記憶される。レーザアレイ内の各レーザとホログラムメモリ内の各回路情報は一体一対応している。あるレーザを点灯させるとそれに対応している干渉縞に光が照射され、回路情報をもった2次元の回折パターンが生じる。光再構成型ゲートアレイ VLSI 上にはフォトダイオードがマトリクス状に実装されており、それらのフォトダイオードがその回折パターンを受光することにより光再構成型ゲートアレイ VLSI 内に所望の回路がプログラムされる。

光再構成型ゲートアレイでは高容量の光メモリである3次元ホログラムメモリに干渉縞として回路情報を蓄えているため、大規模な回路情報を蓄えることが可能である[9]. また、2次元の光バスによりプログラムを行うため、高速な再構成が可能である.このように光再構成型ゲートアレイは高速再構成と大規模な回路情報の保持が可能な次世代のプログラマブルデバイスである.

#### 2.2 光再構成型ゲートアレイ VLSI

光再構成型ゲートアレイ VLSI は論理ブロック、スイッチングマトリクス、入出力ブロックの3つのブロックで構成される. 論理ブロックには AND 回路や OR 回路などの論理回路がプログラムされ、スイッチングマトリクスは配線の切り替えに用いられる. 光再構成型ゲートアレイ VLSI 上にはフォトダイオードがマトリクス上に実装されており、これらのフォトダイオードの出力はプログラマブルゲートアレイの各プログラマブルポイントに接続されており、光照射による再構成が可能になっている. 光再構成型ゲートアレイ VLSI のゲートアレイ構造は既存の FPGA と同じである. 違う点は先に述べたフォトダイオードがプログラムポイントに接続されている点である.

図 2 0.18 μ m CMOS プロセス再構成型ゲートアレイ VLSI のチップ写真

表 1 0.18 u mCMOS プロセス再構成型ゲートアレイ VLSI の仕様

| プロセス         | 0.18 μ m Double poly triple metal CMOS process    |  |

|--------------|---------------------------------------------------|--|

| チップサイズ       | 4.3mm×2.1mm                                       |  |

| 供給電圧         | Core:1.8V I/O: 3.3V                               |  |

| フォトダイオードサイズ  | $6.08 \mu \mathrm{m}  \times 6.08 \mu \mathrm{m}$ |  |

| フォトダイオード間隔   | 横: 30.08 μ m 縦: 30.24 μ m                         |  |

| フォトダイオード数    | 10,402                                            |  |

| 論理ブロック数      | 80                                                |  |

| スイッチングマトリクス数 | 90                                                |  |

| チャネル数        | 8                                                 |  |

| 入出力ブロック数 | 8(32bits) |

|----------|-----------|

| ゲート数     | 2,720     |

今度の試験に用いた新型光再構成型ゲートアレイ VLSI の写真を図 2 に、仕様を表 2 に示す. 基本的には新型光再構成型ゲートアレイ VLSI は以前の光再構成型ゲートアレイ VLSI と同様な構造であるが、負論理実装による再構成の高速化機能が追加されている.

#### 3. 明点ビット数の最小化による高速化手法

#### 3.1 ホログラムメモリの基本特性

再構成速度はフォトダイオードの応答速度に依存することから、照射するレーザの出力を増加させることで容易に再構成の高速化が達成できる.しかし、レーザの出力を増加させると消費電力の増加、さらに、それにより熱も発生するため、最悪の場合、クーリングシステムまで導入しなくてはならず、得策とは言えない.

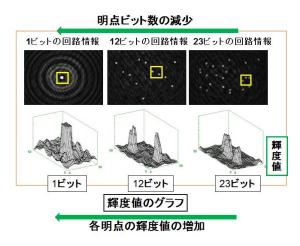

図3 ホログラムメモリの基本特性

そこで、レーザの出力を増加させずに再構成の高速化を達成するためにホログラム の基本特性を用いる。ホログラムメモリからの回折パターンは2値で表現される。明 点が High を意味し、その他の暗い部分は Low を意味する. 図 3 を示されるように、回折パターン内の明点の数、つまり High の数が減少するにつれ、各明点の輝度値が上昇していることが分かる. 再構成速度はフォトダイオードの応答速度に比例するので、回路の機能を変更せずにコンテキスト内の明点の数を削減することができれば、再構成の高速化が達成できる.

#### 3.2 明点ビット数の削減手法

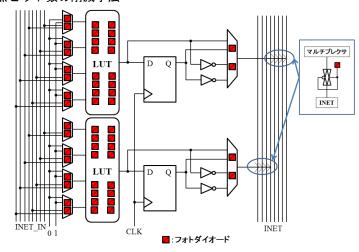

図4 論理ブロック内部の回路図

図4は論理ブロック内部の回路図である.論理ブロック内には4入力1出力のルックアップテーブル(LUT: Look-Up Table)が2つずつ実装されている.これらLUTには任意の組み合わせ回路がプログラムできる.論理ブロック内のルックアップテーブルの各ステートにはフォトダイオードが接続されている.あるフォトダイオードへ明点を照射した場合,そのフォトダイオードに対応しているステートにはHighが記憶され、あるフォトダイオードへ暗点を照射した場合,そのフォトダイオードに対応しているステートにはLowが記憶される.

ここで1つのLUTに対し、フォトダイオードへの明点の照射数がLUTの状態数の半分を超えた場合、つまり4入力の場合には9ビット以上が明点になった場合、LUTへの照射パターンを反転させ、その代わりにLUT後段のインバータを使用し、LUT出力を反転させることにする。このような手法を取れば、明点数を大幅に削減することが可能になる。新型VLSIでは、この反転、非反転をLUT単位で決定できる。

## 4. 再構成試験

#### 4.1 再構成試験光学系

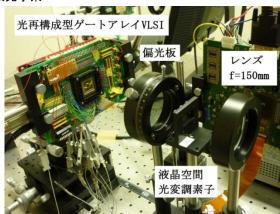

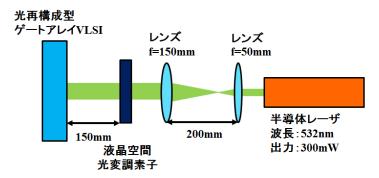

図 5 試験光学系

図 6 試験光学系略図

図 5 に試験光学系の写真を示し、図 6 にそのブロック図を示す. ハードウェアリソースの制限により、レーザ光源として複数のレーザを用いずに単体のレーザを用いている. レーザ (torus 532:Laser Quantum Ltd.) の波長は 532nm, 出力は 300mW である. また、本試験にはホログラムメモリとして液晶空間光変調素子を用いた. この液晶空間光変調素子はセイコー社製の L3D07U-81G00 である. この液晶パネルの画素数は 1,920 ピクセル×1,080 ピクセル、1 画素のサイズは  $8.5 \, \mu$  m である. 本試験に

用いたホログラムパターンは 700 ピクセル×700 ピクセルで構成されている. ホログラムメモリから光再構成型ゲートアレイ VLSI までの距離は 150mm である.

#### 4.2 実装回路

表 2 実装回路の明点ビット数

| 実装回路                      | 明点ビット数 | 実装回路                                                         | 明点ビット数 |

|---------------------------|--------|--------------------------------------------------------------|--------|

| 2-input OR                | 10     | 2-input NOR +INV                                             | 9      |

| 3-input OR                | 16     | 3-input NOR +INV                                             | 11     |

| 3-input XOR               | 15     | 3-input XNOR +INV                                            | 12     |

| 3-input Odd-detector      | 14     | 3-input Even-detector +INV                                   | 13     |

| 4-input OR                | 26     | 4-input NOR +INV                                             | 13     |

| 4-input XOR               | 25     | 4-input XNOR +INV                                            | 14     |

| 4-input Comparator (A≠B)  | 23     | 4-input Comparator (A=B) + INV                               | 16     |

| 4-input Comparator (A=>B) | 21     | 4-input Comparator(A <b) +="" inv<="" td=""><td>18</td></b)> | 18     |

| 4-input Odd-detector      | 20     | 4-input Even-detector +INV                                   | 19     |

| 3-bit down-counter        | 25     | 3-bit down-counter +INV                                      | 23     |

今度の試験では組み合わせ回路 18 パターンと順序回路 2 パターンを実装した。表 2 に実装回路名と実装回路の明点ビット数を示す。下記に実装回路について記述する。 2-input OR 回路は 2 入力 OR 回路であり,2-input NOR+INV は 2 入力 NOR 回路とその後段にインバータを接続した回路である。このような回路変更をすると,1 ビットの明点が削減できる。同様に,3-input OR は 3 入力 OR 回路であり,3-input NOR +INV は 3 入力 NOR 回路とその後段にインバータを接続した回路で,この場合,5 ビットの明点の削減が可能になる。その他の回路も同様の回路セットとなる。

#### 4.3 試験結果

先の実装を行い,明点数を削減した結果を表3に示す.試験結果から明点を平均22%削減することにより,再構成時間を平均39%削減することに成功した.

表3 実装回路の再構成時間

| 実装回路                        | 再構成時間(ns) | 実装回路                                                         | 再構成時間(ns) |

|-----------------------------|-----------|--------------------------------------------------------------|-----------|

| 2-input OR                  | 35        | 2-input NOR +INV                                             | 24        |

| 3-input OR                  | 94        | 3-input NOR +INV                                             | 41        |

| 3-input XOR                 | 78        | 3-input XNOR +INV                                            | 56        |

| 3-input Odd-detector        | 69        | 3-input Even-detector +INV                                   | 59        |

| 4-input OR                  | 188       | 4-input NOR +INV                                             | 42        |

| 4-input XOR                 | 180       | 4-input XNOR +INV                                            | 53        |

| 4-input Comparator<br>(A≠B) | 147       | 4-input Comparator<br>(A=B) +INV                             | 63        |

| 4-input Comparator (A>=B)   | 131       | 4-input Comparator<br>(A <b) +inv<="" td=""><td>97</td></b)> | 97        |

| 4-input Odd-detector        | 122       | 4-input Even-detector +INV                                   | 109       |

| 3-bit down-counter          | 180       | 3-bit down-counter +INV                                      | 148       |

## 5. まとめ

今回の試験では、明点ビット数の最小化による高速化手法をサポートできる新型光再構成型ゲートアレイ VLSI を用いて検証を行った. 試験結果として、明点ビット数を約22%削減することにより、再構成時間を約39%短縮することに成功した. これらの試験結果から明点による再構成の高速化手法の有効性を示すことができた.

**謝辞** 本チップ試作は東京大学大規模集積システム設計教育研究センターを通しローム(株)および凸版印刷(株)の協力で行われたものである.

## 参考文献

- 1) Altera Corporation, "Altera Device," <a href="http://www.altera.com">http://www.altera.com</a>.

- 2) Xilinx Inc., "Xilinx Product Data Sheets," http://www.xilinx.com.

- 3) Kuon, I. and Rose, J.: Measuring the Gap between FPGAs and ASICs, IEEE Transactions on Computer-Aided Design of Integrated Circuit and Systems, Vol. 26, pp. 203-215, Feb. 2007.

- 4) Mumbru, J. et al.: Optically Reconfigurable Gate Array, SPIE of Optics in Computing 2000, Vol. 4089, pp. 763-771 (2000).

- 5) Mumbru, J. et al.: Optical memory for computing and information processing, SPIE on Algorithms, Devices, and Systems for Optical Information Processing III, Vol. 3804, pp. 14-24 (1999).

- 6) Mumbru, J. et al.: Optically Reconfigurable Processors, SPIE Critical Review 1999 Euro-American Workshop on Optoelectronic Information Processing, Vol. 74, pp. 265-288 (1999).

- 7) Moriwaki, R. and Watanabe, M.: An optical configuration acceleration method using negative logic implementation, International Conference on EMERGING TRENDS IN ELECTRONIC AND PHOTONIC DEVICES & SYSTEMS, pp. 565-568, Varanasi, INDIA, (2009).

- 8) Moriwaki, R. and Watanabe, M.: A configuration speed acceleration method for a sequential circuit using a negative logic implementation, IEEE International Conference on Space Optical Systems and Applications, pp. 213-217, Santa Monica, USA (2011).

- 9) KINCADE K: Holographic data storage prepares for the real world, Laser Focus World. Vol. 39, no. 10, pp. 68,70-73. (2003).