# 誘導結合による三次元積層チップのためのパケット転送ネットワーク

紀<sup>††</sup> 宏† 佐々木 大 輔 谷 宏 竹 己† 小 野 友 西 Ш 幸 徳†  $\blacksquare$ 忠 広† 天 野 英 晴

誘導結合によるチップ間ワイヤレス接続技術は,製造後にチップを重ねて実装することで,三次元積層が可能であり,その高い柔軟性と転送性能が注目されている.この三次元転送技術を有効に利用するためには,積層されたチップのコア間で容易にデータを転送を行う方式を確立する必要がある。本論文では,ワイヤレス誘導結合を用いてチップ間でコミュニケーションを行う手法として,垂直バブルフローを利用したリング型  ${

m NoC}$  を提案し,仮想チャネルを用いたリング型  ${

m NoC}$  ,および,垂直バス方式と比較する.さらに,これらの通信方式を搭載したプロトタイプチップを実装し,それぞれの手法による性能,および,面積の違いを測定する.シミュレーションによる評価の結果,プロトタイプチップは  $200{

m MHz}$  で動作し,誘導結合部分は  $4{

m GHz}$  超のクロック伝送によるダブルデータレート伝送を実現,平均消費電力は最大は  $33.8{

m mW}$  となった.垂直バブルフローおよび仮想チャネルを用いたリング型  ${

m NoC}$  は,垂直バス方式と比べ高いスループット性能を実現した.さらに,垂直バブルフローは既存の仮想チャネルを用いる方式よりも面積性能比で優れることが分かった.

## Packet Transfer Networks for 3-D Stacked Chips with Inductive Coupling

Daisuke Sasaki,† Hiroki Matsutani,†† Yasuhiro Take,† Yuki Ono,† Yukinori Nishiyama,† Tadahiro Kuroda† and Hideharu Amano†

Wireless chip-interconnect using inductive coupling, which enables us to stack know-good-dies after the chip fabrication, receives an attention with its high degree of flexibility and communication performance. To make the best use of the benefits, communication scheme between cores on different chips must be established. As the communication scheme for the wireless chip-interconnect, we propose a ring-based NoC with vertical bubble flow control and compare it with a ring-based NoC with virtual-channel flow control and a conventional vertical bus structure. These communication schemes are implemented on a real wireless 3-D IC, and they are evaluated in terms of the performance and area. Simulation results show that the prototype chip works at 200MHz. The wireless interconnect supports 4GHz double data rate transfer and consumes 33.8mW at average. The ring-based NoCs achieve a significantly higher throughput compared to the bus-based one. The ring-based NoC with vertical bubble flow outperforms that with conventional virtual-channel flow control in terms of the cost per performance.

## 1. はじめに

半導体技術の進歩にともない,多数の Intellectual Property (IP) コアを 1 チップ上に実装できるようになった.このような System-on-a-Chip (SoC)では,単ーチップ上の IP コア間の接続を密にすることで,高い効率で協調動作をさせることができる.しか

† 慶應義塾大学 理工学部

Faculty of science and Technology, Keio University

†† 東京大学大学院 情報理工学系研究科

Graduate School of Information Science and Technology, The University of Tokyo

し、プロセスが進むにつれ、複雑な工程により増加したマスク数によるコストと設計のコストが増え、最初の一個のチップが出来上がるまでに必要なコストが高騰している。このため、少量多品種の製品ごとに SoCを新規開発することは困難になりつつある。そこで、個別に開発されたチップ同士をパッケージ内で接続することができる System-in-Package (SiP)技術が開発されている。特に、チップ同士を垂直方向に積層する3次元積層1)は、最長配線の短縮、クリティカルパス遅延の短縮、リピータバッファの削減、消費電力の削減などの利点により近年実用化が進んでいる。

現在の三次元積層技術の主流はマイクロバンプ方

式 $^2$ )やスルーシリコンビア方式 $^3$ )などの有線方式である.一方で,ワイヤレス接続による $^3$ 次元積層も研究が進んでおり,中でも誘導結合方式 $^4$ ) $^5$ )は,製造後のチップ同士をボンディングなしに接続できることからチップの追加,削除,入れ替えを柔軟に行うことができる.既に誘導結合を用いた三次元積層システムは試作されている $^6$ ) $^7$ )が,今までの試作では誘導結合を配線の一部として利用している.つまり,システム毎に誘導結合の使い方が統一されておらず,様々なチップを接続することはできなかった.

本論文では,誘導結合を用いて様々なチップを柔軟に三次元積層して SiP を構築するためのチップ間パケット転送ネットワークを提案する.本パケットネットワークはチップ内とチップ間の両方で切れ目無く利用可能で,チップ内のネットワークの形状に依存せずにデッドロックフリーで動作し,三次元的な拡張性に優れている.

提案するパケット転送ネットワークを各チップが持つことでこれらを自由に重ねることができ、ビルディングブロック型に LSI システムを構築していくことが可能となる.つまり、メモリ、CPU、アクセラレータなど様々な機能を持ったチップを単体で作り、これらを用途に応じて組み合わせることで、様々な性能や機能を持ったシステムを構築することができる.これによって目的用途別に開発してきた SoC の開発費用を大幅に節約できる.また、電源の問題が解決できれば、非接触型の LSI カードの抜き差しで、システムの変更が可能になり、必要に応じてカードを集めることで性能や機能を変更でき、効率的な LSI チップの運用が可能となる.また、これらの LSI カードは、製品の寿命を超えて再利用することができることから、環境への貢献も期待できる.

本論文の構成は次の通りである.まず 2章で三次元積層技術を紹介し,本論文で用いる誘導結合方式の利点を示す.次に 3章で,誘導結合を用いた三次元積層のための通信手法として垂直バブルフローを用いたリング型 NoC (Network-on-Chip)を提案し,比較相手として仮想チャネルを用いたリング型 NoC,および,垂直バス方式を紹介する.4章では,垂直バブルフロー方式と垂直バス方式の 2 つを搭載したプロトタイプチップについて述べ,5章ではこれらの 3方式をシミュレーションによりスループット性能,および,面積の点で評価する.最後に 6章で本論文をまとめる.

## 2. 三次元積層技術

積層されたチップ間の結合網には有線方式と無線(ワイヤレス)方式の2つが考えられる.有線方式であるマイクロバンプ<sup>2)</sup>とスルーシリコンビア<sup>3)</sup>は,小さな面積で三次元方向の通信路を確保できるため,既に実チップでの利用が進んでいる.しかし,直接チッ

プ間に結合網を構成するため,チップ試作後にチップ の積層枚数を変更することは困難である.

一方,無線方式としては容量結合<sup>8)</sup>と誘導結合<sup>4)</sup>がある.このうち容量結合方式は,チップの合わさった面同士でしか通信を行えないため積層可能なチップ数が制限され拡張性に乏しい.これに対して,誘導結合方式では磁界を利用したデータ転送を行うことができるため,複数のチップを積層することが可能である.本論文では,チップの組みあわせを柔軟に変更可能なSoCを目標としており,このためには誘導結合方式が最も適している.

誘導結合方式は,配線層を用いてインダクタを形成することができることから,通常の CMOS プロセスが変更なしで用いることができ,インダクタ当たり  $8{\rm GHz}$  を越えた転送レートで  $10^{-16}$  を下回る BER (Bit Error Rate )を実現している $^{7}$ . 転送に要するエネルギーも  $0.14{\rm pJ/bit}$  と小さい.

一方で,インダクタの面積は最も小さいものでも  $30\mu\mathrm{m}\times30\mu\mathrm{m}$  は必要であり,有線方式よりも大きい.また,三次元的に重なったインダクタ間ではデータのプロードキャストが可能である反面,干渉を避けようとすれば時分割利用が必要となる.さらに現在の実装技術では各チップにワイヤで電源供給が必要であるため,I/O パッドの面積を確保するためずらして積層する必要があるなどの問題点がある.

誘導結合方式は,既に GPU と DRAM の接続<sup>7)</sup>に用いられ,異なったプロセスで作られたチップの接続にも成功している.また,MuCCRA-Cube<sup>6)</sup>では,三次元構成の動的リコンフィギャラブルプロセッサの構成に利用された.しかし,これらの試作例において誘導結合路は,三次元方向の配線の代替として利用されており,様々なチップを自由に積層することは考慮されていない.このためには3章で提案するような統一されたデータ転送方式が必要不可欠である.

### 3. 誘導結合ネットワーク方式

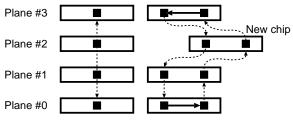

誘導結合による三次元積層のメリットは,製造後のチップ同士をボンディングなしに接続できる点,それによって,チップの追加,削除,入れ替えを柔軟に行うことができる点である.三次元チップ全体を1つのネットワーク,各チップ上のコアをノードと考えると,誘導結合による三次元積層ではノードの追加,削除,入れ替えが発生する.これを実現する最もシンプルかつ低コストな結合網は共有パス,もしくは,リプルかつ低コストな結合網は共有パス,もしくは,リプルかつ低コストな結合網は共有パス,もしくはかいカンクである(図1).これより複雑なカトワークトポロジではノードの追加,削除,入れ替えによってルーティング情報が変化するため,トポロジの認識,および,デッドロックフリーな経路計算と各ルータにおける経路表の更新が必要な場合がある.一

(1) Shared bus (2) Ring network

図 1 ノードの追加,削除,入れ替えが容易な誘導結合向け垂直 ネットワーク.1)垂直共有バス,2)リングネットワーク.

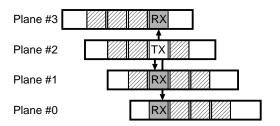

図 2 垂直共有バス方式による積層 . タイムスロットに応じて TX と RX を動的に切り替える .

方,バスやリングではこのような煩雑な処理をせずともノードの追加,削除,入れ替えができるため,誘導結合による三次元積層に適している.

以降,まず,垂直共有バス方式,および,リング型NoC向けに仮想チャネルを用いた方式を紹介し,次に,同じくリングネットワーク向けに垂直バブルフロー制御を用いた方式を提案する.5章の評価ではこれらの3つの方式をスループット性能と面積の点で評価する.

#### 3.1 垂直共有バス方式

最も単純なチップ間結合網は図2に示すように垂直 方向に同じ位置にインダクタを重ねてバスを形成し, その上でパケット転送を行う方法である.

通常のバス同様,一時期にデータを送信できるチッ プは一つに限られる.しかし,三次元誘導結合を用い て,アービトレーションをチップ間で行うのはオーバー ヘッドが大きいため,あらかじめ転送可能なタイムス ロットを決めておく方が効率が良い. 例えば,4章で 紹介するプロトタイプチップでは,8クロックのタイ ムスロットを各チップに周期的に割り当てている. あ るチップのインダクタは,自分の順番のタイムスロッ トでのみ送信状態(TX)となり,他のスロットでは受 信状態(RX)となる.この手法では,単一のインダ クタでチップ間を接続可能であり , 誘導結合のブロー ドキャストが生かせる利点がある.一方で,タイムス ロットが決っていることから,接続できるチップ数に 制限が生じること、自分のタイムスロット以外では転 送ができないため利用率が低いこと、遠隔のチップま でデータを届けるためにインダクタのサイズを大きく する必要があること,送受信の高速な切り替えが必要 であることなど欠点も多い.

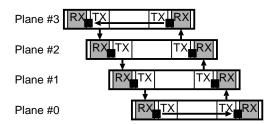

図3 片方向リングネットワークによる積層.

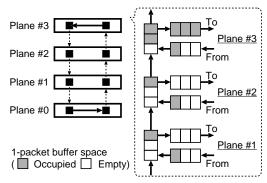

図 4 垂直バブルフロー制御.

#### 3.2 リングネットワーク

誘導結合による積層の柔軟性を活かしつつ , バス方式の欠点を解決するために , リング型 NoC を用いる (図3).この例では片方向リングを採用しているが , リングを多重化すること , 双方向リングに拡張することは容易である . リング型 NoC では , インダクタのモード (TX もしくは RX)は固定とし , 図3のように隣接チップの TXと RX が重なるように積層する . 隣接チップ同士でのみ通信を行うため通信距離が短く , インダクタのサイズを抑えることができる .

しかし,リング構造は本質的に循環依存を内包するため,パケット通信のデッドロックを防ぐ必要があるこのために,まず,仮想チャネルを用いる従来方式を紹介し,そのうえで,垂直パブルフロー制御を用いる方式を提案する.

### 3.2.1 リングにおける仮想チャネル方式

循環依存を断ち切る最も一般的な方法はルータバッファの多重化,つまり,仮想チャネル $^{9}$ )の利用である.リングトポロジの場合,入力物理チャネルごとに仮想チャネルを $^{2}$  本持たせ,パケットがリング上のあるリンク(dateline と呼ぶ)をまたぐときに,仮想チャネル番号を切り替える.これによって dateline の前後で循環依存が切れ,デッドロックが発生しなくなる.

この方式は,一般的な仮想チャネルルータをそのまま利用できるという利点があるが,オンチップルータの面積の大半を占めるバッファを多重化するため,その分,面積コストが増えるという欠点がある.

3.2.2 リングにおける垂直バブルフロー方式 バブルフロー制御<sup>10)11)</sup> によって,循環構造(リン グ)を内包するネットワークにおいて仮想チャネルを用いずにデッドロックを回避できる.本論文ではこのバブルフロー制御を誘導結合によるリング型 NoC に適用することを提案する.図4のようなリングネットワークにおいて,ルータがすべてのバッファを使いきらない限りブロッキングによるデッドロックは起きない.つまり,すべてのルータにおいてバッファを使いきらないように常に1パケット分の空き(バブル)を残しておくようにフロー制御することで,デッドロックを回避できる.具体的には,リングにおけるパケット転送に以下の3つのルールを課す.

- 転送ルール1: リング内のパケット転送の場合,

転送先ルータに1パケット分の空きバッファがあれば前進できる.

- 転送ルール 2: リング外のルータおよびコアからリング内へのパケット注入は,転送先ルータの入力ポートに2パケット分の空きバッファがある場合にのみ転送を許可する.

- 転送ルール3: リング内からリング外のルータ およびコアへのパケット出力の場合,転送先ルー タの入力ポートに1パケット分の空きバッファが ある場合のみ転送を許可する.出力できない場合 はリング内を直進する,つまり,リングをもう一 周回る(ミスルーティングする)ことになる.

図 4 の例では,プレーン 1 と 2 では水平方向から 垂直リングにパケットを注入できるが,プレーン 3 は 注入できない(転送ルール 2). また,プレーン 1 と 2 の垂直バッファのパケットはリング外に出ることが できるが,プレーン 3 のパケットはこの状態ではリン グ外に出ることができず,リングをもう一周する必要 がある(転送ルール 3).

この方式は仮想チャネルは不要であるが,各入力 バッファはパケットを最低 2 個格納できるだけの容量 が必要である.パケットのスイッチング方法はワーム ホール方式ではなく,バーチャルカットスルー(virtual cut-through,VCT)方式となる.このため,パケット長が長くなると必要なバッファサイズが増える という欠点がある.

5章では,本章で提案したリング向け垂直バブルフロー方式に加え,垂直バス方式,リング向け仮想チャネル方式をスループット性能と面積について評価する.

### 4. プロトタイプチップ

3章で導入した3つの通信方式を実機で検証するために,プロトタイプチップ Cube-0を設計,実装した.このチップを積み重ねることで,まず,垂直バス方式と垂直バブルフロー方式の動作検証,面積コスト,転送スループットを測定できる.また,このチップのルータは仮想チャネルを2本搭載しているため,仮想

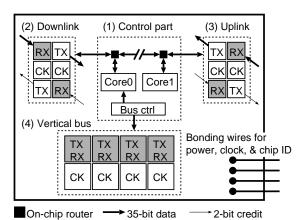

図 5 Cube-0 チップのアーキテクチャ .

チャネル方式の面積コストの見積りができる .

### 4.1 Cube-0 チップの構成

図 5 に Cube-0 の構成を示す.このチップは次の 4 つのコンポーネントから構成される:1) コントロール部,2) リング型 NoC の Downlink 用誘導結合インターフェイス,3) 同じく Uplink 用誘導結合インターフェイス,4) 垂直バス用誘導結合インターフェイス.

コントロール部には,パケット生成器とパケットカウンタから成るコアが 2 個 ( Core~0~e~1 ),リング型 NoC 用のオンチップルータ ( 図中の黒い四角 ) が 2 個,垂直バス用コントローラが 1 個実装されている.それぞれの詳細は 4.3~節~4.5~節で説明する.

誘導結合インターフェイスにおける TX は送信モジュール , RX は受信モジュール , CK は転送用クロックである . この 4GHz クロックに同期してデータがシリアル転送される . 垂直バス方式では 4) の誘導結合インターフェイスを使い , リング型 NoC では 2) と 3) の Downlink と Uplink を組み合わせて片方向リングを形成する . 垂直バス方式およびリング型 NoC の 積層方法は 4.2 節で説明する .

なお , リング型  $\mathrm{NoC}$  と共有バス方式では , 積層の方法が異なるため , 両者は同時にテストすることはできず , 外部からモード切り替え信号を与えて制御する .

#### 4.2 チップの積層方法

図 3 にリング型 NoC の積層方法を示す.リング型 NoC ではチップ同士は point-to-point で接続される ため,図のように隣接するチップの TX と RX が垂直に重なるようにチップを横方向にずらしながら積層する.CK はデータ送信を行うチップが送信データと同期して 4GHz の周波数で転送する.CK とデータを別のインダクタで同期して転送するため,全体で転送ク

ただし,実装上の理由から仮想チャネルの一部をデバッグおよび 測定用のパケット転送に割り当てたため,正確にはこのチップで 仮想チャネル方式の動作検証を行うことはできない.仮想チャネ ル方式のスループットは,デバッグおよび測定用のパケットを流 さないように修正した RTL モデルを用いることで測定できる. ロックを同期させる必要はない. 仮想チャネル方式および垂直パブルフロー方式では,転送先ルータのバッファの空き容量(credit)を転送元ルータに示す必要がある. つまり, credit-base フロー制御のために通信データとは逆方向のリンクが必要であり,そのために Uplink, Downlink 共に TX と RX の両方を持っている.

チップをずらして積層することによってチップ一辺の I/O にボンディングを行うことができ,ここから電源とシステムクロック を供給する.また,今回はテスト用の実装であるため,モニタ用の端子も設けられている(図5).

一方,図 2 に垂直バス方式の積層方法を示す.本来,共有バス方式は各チップに 1 個のみインダクタを用意してチップを横にずらさずに積層する.しかし,今回の実装では I/O のボンディングスペースを確保するため,および,同一チップ上にリング型 NoC と垂直バスの両方を実装するため,リング型 NoC と同じチップ上にインダクタのサイズ分ずらしてバス構造を実現している.そのため,最大 4 枚のチップを積層するために各チップに 4 組のインダクタを実装したが,実際に使われるのは 1 組だけである.

#### 4.3 コア(パケット生成器・カウンタ)

図 5 に示すとおり, Cube-0 チップは 2 個のコアを持つ. 本チップは純粋にテスト用であるので, コアはパケット生成器とパケットカウンタを装備した簡単なものである.

コアはチップ外から与えられる信号がアサートされると,パケットを 1 個生成してリング型 NoC 用のルータあるいは垂直バスコントローラに転送する.パケットは,32-bit のデータと 3-bit の制御信号から成る 35bit 幅で,ヘッダを含め 5 フリットの固定サイズであり,転送周波数は 200MHz である.また,外部からのトリガーによるパケット生成以外にも,ランダムな宛先に自動的に連続生成を行うモードを持っている.受信パケット数は内部の 45-bit カウンタで集計され,チップ外からモニタすることが可能である.

### 4.4 リング型 NoC 用オンチップルータ

図 5 に示すとおり,Cube-0 チップは 2 個のルータを持つ.同一チップ上のルータ間リンクは,リングを形成するために,最上位チップと最下位チップで使われ,それ以外のチップでは使われない.

各ルータはコア,隣接ルータ,誘導結合インターフェイスと接続するために35-bitの入出力ポートを3つ持つ.ルータ中央にクロスバースイッチとアービタを持ち,各入力ポートには16フリット分の入力バッファ,各出力ポートには1フリット分の出力バッファを持つ.ルータに入力されたパケットは,入力バッファでバッ

コア, オンチップルータ, 垂直バスコントローラへ供給する 200MHz のクロック.

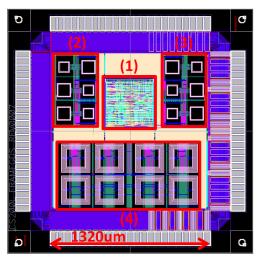

図 6 Cube-0 チップのフロアプラン .

ファリングされ , 宛先アドレスに応じた出力ポートが割り当てられる . その後 , クロスバスイッチを通過して , 出力バッファで一度バッファリングされた後 , コア , 隣接ルータ , 誘導結合インターフェイスのいずれかへ転送される . デッドロックを防ぐためのフロー転送制御として , 3 章で提案した転送ルールが実装されており , これを満足する場合のみ転送が許可される . コア同様 , ルータも 200MHz で動作する .

#### 4.5 垂直バス用コントローラ

共有バス方式の制御用ハードウェアは,コアからパケットを受け取り自分の送信タイムスロットに送信する.受信時のタイムスロットではパケットを受け取り,自分宛のパケットの場合,コアにパケットを渡す.

各タイムスロットは 8 クロックの長さであり,1 クロック目と 8 クロック目はパケットを転送できない.これは違うチップ同士のパケット転送が競合しないようにする配慮である.また,誘導結合はタイムスロットごとに TX と RX を切り替えながら動作する.タイムスロットは割り当てられたチップ番号によって決定する.あるチップが自分のタイムスロットになったときには誘導結合インターフェイスは TX となり,自分のタイムスロット以外のときには RX となる.

#### 4.6 Cube-0 の実装

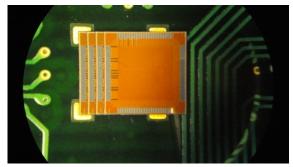

Fujitsu e-shuttle 65nm CMOS プロセスの 2.1mm 角上に実装した、論理合成には Synopsys 社の Design Compiler を使用し、コアなどの各モジュールの配置配線、TOP 階層の設計には同社の IC Compiler を使用した・インダクタのレイアウトは、Cadence 社の Virtuoso によりフルカスタムで行った・図 6 に Cube-0のフロアプランを示す・フロアプラン上の (1)~(4) は図 5 のコンポーネントの番号に対応している・また、図 7 に現在開発中の Cube-0 の基板写真を示す・4 枚の Cube-0 チップを横方向にずらしながら積層してい

図 7 Cube-0 チップ 4 枚積層時の基板 (開発中).

表 1 Cube-0 チップの仕様

|   | 表 I Cube-0 デックの仕様.  |                                          |  |

|---|---------------------|------------------------------------------|--|

|   | Process technology  | Fujitsu CS202SZ 65nm                     |  |

|   | Chip size           | $2.1 \text{mm} \times 2.1 \text{mm}$     |  |

|   | System clock        | $200 \mathrm{MHz}$                       |  |

| • | # of ports          | 3                                        |  |

|   | # of VCs            | 2                                        |  |

|   | Router input buffer | 16-flit FIFO for each VC                 |  |

|   | Flit size           | 32-bit data + 3-bit control              |  |

|   | Packet size         | 5-flit                                   |  |

| • | Inductor for bubble | $150\mu\mathrm{m}\times150\mu\mathrm{m}$ |  |

|   | Inductor for bus    | $250\mu\mathrm{m}\times250\mu\mathrm{m}$ |  |

|   | Inductor bandwidth  | 35 [bit/cycle/channel]                   |  |

#### る様子が分かる.

表 1 に Cube-0 の仕様を示す.今回はテスト用チップであり,安定な転送を目指して,垂直バス方式,リング型 NoC 共にインダクタのサイズはかなり大きめにしてある.特に垂直バス用のインダクタは,4 枚積層した最長距離までデータを転送するため,隣接間通信を行うリング型 NoC 用の 2.7 倍の面積を使っている.インダクタサイズは  $30\mu \mathrm{m} \times 30\mu \mathrm{m}$  にすることが可能である  $^{5}$

### 5. Cube-0 の評価

本章では,垂直バス方式,リング向け仮想チャネル方式,リング向け垂直バブルフロー方式をスループット性能および面積の点で評価する.さらに,Cube-0チップにおけるルータの面積内訳,インダクタのポストレイアウトシミュレーション結果と消費電力を示す.

#### 5.1 転送スループット

Cube-0 チップは現在チップの製造は終了し,基板上に積層実装中である.ここでは,Candence NC-Verilog を用いた RTL シミュレーションにより各方式の転送スループットを評価した.

RTLシミュレーションには以下の3種類のトラフィックパターンを用いた.

• Uniform traffic:各ノードはランダムに選んだ宛先にパケットを送信する.片方向リングにおいてノード数を N とするとき,平均ホップ数 H=N/2 となる.

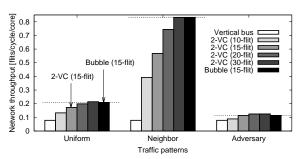

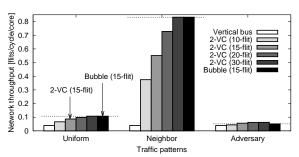

図 8 転送スループット(4枚積層した場合).

図 9 転送スループット(8枚積層した場合).

- Neighbor traffic: 各ノードは1 ホップ先のノードにパケットを送信する. 平均ホップ数は H=1 となる.

- Adversary traffic: 各ノードは最も遠いノード にパケットを送信する . 平均ホップ数は H=N-1 となる .

シミュレーションではパケット長は 5-flit とした.垂直バブルフロー方式では,3 パケット分のバッファ容量として,各入力チャネルに 15-flit 分のバッファを持たせた.ここではこれを Bubble (15-flit) と表記する.一方,仮想チャネル方式では,デッドロックを防ぐために 2 本の仮想チャネルが要る.ここで,2-VC (n-flit) は各仮想チャネルが(n/2)-flit 分のバッファを持つこととする.なお,両方の仮想チャネルの負荷は必ずしも同じにはならないため,2-VC (15-flit) のスループットは,仮想チャネル 0 に 10-flit バッファを割り当て,仮想チャネル 1 に 5-flit バッファを割り当て,仮想チャネル 1 に 10-flit バッファを割り当て,仮想チャネル 10 に 10-flit バッファを割り当て,仮想チャネル 10 に 10-flit バッファを割り当て,仮想チャネル 10 に 10-flit バッファを割り当て

図 8 と図 9 に積層枚数を 4 枚と 8 枚としたときの 転送スループットを示す . グラフ中の Vertical bus , 2-VC (*n*-flit) , Bubble (15-flit) はそれぞれ垂直バス 方式 , 仮想チャネル方式 , バブルフロー方式に対応す る . 2-VC (15-flit) と Bubble (15-flit) はバッファ容 量が等価である .

グラフより,垂直バス方式のスループットはトラフィックパターンに依らず一定となった.これは垂直バスではタイムスロット方式を採用しているためであ

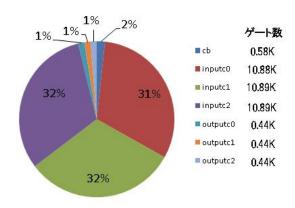

図 10 垂直バブルフロー制御用ルータのゲート数と内訳.

る.また,垂直バス型のスループットはリング型 NoC よりかなり低いことが分かる.

リング型 NoC においては, Bubble (15-flit) は 2-VC (15-flit) とほぼ同等以上のスループットが出ている. 仮想チャネル方式において仮想チャネルの切り替えが生じない Neighbor traffic では, Bubble (15-flit) と仮想チャネル当たり 15-flit のバッファを持つ 2-VC (30-flit) のスループットが等しくなった. 以上より, 垂直バブルフロー方式のほうが仮想チャネル方式より効率が良いことが分かった.

さらに , コア部分にレイアウト後の Verilog ネットリスト , インダクタ部分には等価な Verilog モデルを用いた遅延付きポストレイアウトシミュレーションを実施した . その結果コア部分が 200MHz で動作することを確認した .

### 5.2 ルータのハードウェア量

図 6 に示すように,Cube-0 のコントロール部(パケット生成・受信コア, $\mu$ ータ 2 個, $\mu$ スコントローラを含む)は高々 $350\mu$ m 角のエリアに実装されており,その面積はさほど大きくない.

図 10 に垂直バブルフロー方式のルータの面積内訳 を示す . グラフ中の cb はクロスバスイッチ , inputc は入力チャネル, outputc は出力チャネルである.3 ポートルータであるため, inputc および outputc は 3 個ずつある . 4.4 節で述べたとおり , 各入力チャネル は2個の仮想チャネルを持ち,各仮想チャネルは16 フリット分の FIFO バッファを持つ.一方,出力チャ ネルは1フリット分の出力バッファを持つのみである. グラフより,入力チャネル $(inputc0 \sim 2)$ がルータ面 積の 90%以上を占めていることが分かる . ルータの ポート数が3と小さいため,クロスバスイッチcbの 面積も非常に小さくなっている.このようにルータ面 積の大部分を入力バッファが占めており, 垂直バブル フロー制御の実装に要する面積はバッファに比べると ごくわずかである.なお,垂直バブルフロー制御では デッドロック回避のために仮想チャネルを用いない.

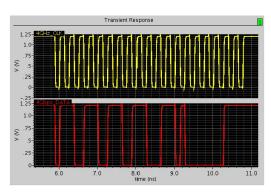

図 11 誘導結合部分のポストレイアウトシミュレーションの結果.

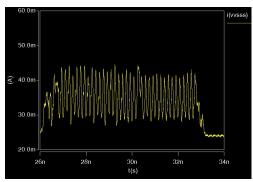

図 12 誘導結合部分の電流値シミュレーションの結果.

このルータでは仮想チャネルを 2 本実装しているが, 実際には仮想チャネルは 1 本で十分(つまり仮想チャネルは不要)であるため,ルータの inpute の面積を 半分以下に削減することが可能である.

### 5.3 誘導結合の消費電力

図 11 に誘導結合部分の SPICE によるポストレイ アウトシミュレーションの結果,図 12 に誘導結合部 分の電流値の SPICE によるシミュレーションの結果 を示す.

図 11 は、上がクロック、下がデータ波形を示す.シミュレーション結果より、誘導結合部分で 4GHz 超クロック伝送と 8Gbps のダブルデータレート伝送を確認し、NoC ルータに対する入出力信号タイミングも正しいことを確認した.また、図 12 より、誘導結合 1チャネルあたりの平均動作消費電力が 33.8mW であることを確認した.以上より、Cube-0チップにおいてコア自身がインダクタを制御し、なおかつ、正常に動作していることをシミュレーション上で確認できた.

### 6. まとめと今後の課題

誘導結合によるチップ間ワイヤレス接続技術を有効 に利用するためには,積層されたチップのコア間で容 易にデータを転送を行う方式を確立する必要がある. 本論文では,ワイヤレス誘導結合を用いてチップ間で コミュニケーションを行う手法として,垂直バブルフローを利用したリング型 NoC を提案し,仮想チャネルを用いたリング型 NoC,および,垂直バス方式と比較した.シミュレーション結果より,垂直バブルフローおよび仮想チャネルを用いたリング型 NoC は,垂直バス方式と比べ高いスループット性能を実現した.また,垂直バブルフローは既存の仮想チャネルを用いる方式よりも面積性能比で優れることが分かった.

さらに,本研究ではこれらの通信方式を搭載したプロトタイプチップ Cube-0 を実装した.ポストレイアウトシミュレーション上ではあるが Cube-0 は 200MHzで動作し,チップ間のワイヤレス通信もできていることが分かった.

今後は,現在,積層実装中の Cube-0 の実チップを用いて,性能,消費電力を測定する必要がある.また,Cube-0 はテスト用であるため,コアはパケット生成器とカウンタのみであったが,現在,設計中の Cube-1では MIPS ライクなプロセッサおよびキャッシュメモリをワイヤレスで接続する予定である.さらには,電源の供給をボンディングワイヤではなく,ワイヤレスで供給する研究<sup>12)</sup> も進めていくことも必要であると考えられる.

#### 謝 辞

本研究は株式会社半導体理工学センター,平成 21 年度「次世代回路アーキテクチャ技術開発事業」の一貫として,東京大学大規模集積システム設計教育研究センターを通し,株式会社半導体理工学研究センター・(株)イー・シャトルおよび富士通株式会社・シノプシス株式会社・日本ケイデンス株式会社・メンター株式会社の協力で行なわれた.

### 参 考 文 献

- Davis, W. R., Wilson, J., Mick, S., Xu, J., Hua, H., Mineo, C., Sule, A. M., Steer, M. and Franzon, P. D.: Demystifying 3D ICs: The Pros and Cons of Going Vertical, *IEEE Design and Test of Computers*, Vol. 22, No. 6, pp. 498–510 (2005).

- Ezaki, T., Kondo, K., Ozaki, H., Sasaki, N., Yonemura, H., Kitano, M., Tanaka, S. and Hirayama, T.: A 160Gb/s Interface Design Configuration for Multichip LSI, Proceedings of the International Solid-State Circuits Conference (ISSCC'04), pp. 140–141 (2004).

- 3) Burns, J., McIlrath, L., Keast, C., Lewis, C., Loomis, A., Warner, K. and Wyatt, P.: Three-Dimensional Integrated Circuits for Low-Power High-Bandwidth Systems on a Chip, Proceedings of the International Solid-State Circuits Conference (ISSCC'01), pp. 268–269 (2001).

- 4) Mizoguchi, D., Yusof, Y. B., Miura, N., Sakurai, T. and Kuroda, T.: A 1.2Gb/s/pin Wire-

- less Superconnect Based on Inductive Inter-Chip Signaling (IIS), *Proceedings of the In*ternational Solid-State Circuits Conference ( ISSCC'04), pp. 142–151 (2004).

- 5) Miura, N., Ishikuro, H., Sakurai, T. and Kuroda, T.: A 0.14pJ/b Inductive-Coupling Inter-Chip Data Transceiver with Digitally-Controlled Precise Pulse Shaping, *Proceedings of the International Solid-State Circuits Conference (ISSCC'07)*, pp. 358–359 (2007).

- 6) Saito, S., Kohama, Y., Sugimori, Y., Hasegawa, Y., Matsutani, H., Sano, T., Kasuga, K., Yoshida, Y., Niitsu, K., Miura, N., Kuroda, T. and Amano, H.: MuCCRA-Cube: a 3D Dynamically Reconfigurable Processor with Inductive-Coupling Link, Proceedings of the Field-Programmable Logic and Applications (FPL'09), pp. 6–11 (2009).

- Miura, N., Kasuga, K., Saito, M. and Kuroda, T.: An 8Tb/s 1pJ/b 0.8mm2/Tb/s QDR Inductive-Coupling Interface Between 65nm CMOS and 0.1um DRAM, Proceedings of the International Solid-State Circuits Conference (ISSCC'10), pp. 436-437 (2010).

- 8) Kanda, K., Antono, D. D., Ishida, K., Kawaguchi, H., Kuroda, T. and Sakurai, T.: 1.27-Gbps/pin, 3mW/pin Wireless Superconnect (WSC) Interface Scheme, *Proceedings of the International Solid-State Circuits Conference (ISSCC'03)*, pp. 186–187 (2003).

- 9) Dally, W. J. and Towles, B.: *Principles and Practices of Interconnection Networks*, Morgan Kaufmann (2004).

- 10) Puente, V., Beivide, R., Gregorio, J. A., Prellezo, J. M., Duato, J. and Izu, C.: Adaptive Bubble Router: A Design to Improve Performance in Torus Networks, *Proceedings of the International Conference on Parallel Process*ing (ICPP'99), pp. 58–67 (1999).

- 11) Abad, P., Puente, V., Prieto, P. and Gregorio, J. A.: Rotary Router: An Efficient Architecture for CMP Interconnection Networks, Proceedings of the International Symposium on Computer Architecture (ISCA'07), pp. 116–125 (2007).

- 12) Yuan, Y., Yoshida, Y., Yamagishi, N. and Kuroda, T.: Chip-to-Chip Power Delivery by Inductive Coupling with Ripple Canceling Scheme, Proceedings of the International Conference on Solid State Devices and Materials, pp. 502–503 (2007).