# 90nm 標準 CMOS プロセスを用いて試作した 40Gb/s 4:1 MUX/1:4 DEMUX

神田浩一 山崎大輔 山本拓司 掘中実 小川淳二 田村泰孝 小野寺裕幸 株式会社 富士通研究所 システム LSI 開発研究所 ネットワーク SoC 開発部

〒211-8588 神奈川県川崎市中原区上小田中 4-1-1

E-mail: kouichi.kanda@jp.fujitsu.com

あらまし 本論文では、90nm 標準 CMOS プロセスを用いて試作した、1.2V 単一電源動作可能な 40Gb/s 4:1 MUX 及び 1:4 DEMUX 回路について、主に以下の三つの技術的内容に焦点を置きながら説明する。一つ目は、最適なインダクタ・ピーキングを施した MUX の出力ドライバ回路についてである。二つ目は、低電圧動作に適した高速セレクタ回路、及びラッチ回路についてである。三つ目は、このような高周波回路を試作する上で必要となるデバイスモデルに関してである。試作した MUX 及び DEMUX は 1.2V 単一電源で動作し、消費電流は各々110mA, 52mAであった。実験では比較的良好なアイ・パターンが得られた。

キーワード: 40Gb/s, MUX, DEMUX, 90nm CMOS, インダクタ・ピーキング

# 40Gb/s 4:1 MUX/1:4 DEMUX in 90nm standard CMOS technology

Kouichi Kanda, Daisuke Yamazaki, Takuji Yamamoto, Minoru Horinaka, Junji Ogawa, Hirotaka Tamura, and Hiroyuki Onodera

System LSI Development Laboratories, Fujitsu Laboratories LTD.

4-1-1, Kamikodanaka, Nakahara-ku, Kawasaki, 211-8588, Japan E-mail: kkanda@labs.fujitsu.com

**Abstract** This paper describes a 1.2V, 40Gb/s, 4:1 MUX and 1:4 DEMUX designed in 90nm standard CMOS technology, mainly focusing on three design challenges to meet the speed requirement. First, optimization of peaking inductors for 40Gb/s tapered output buffer is explained using effective frequency response analysis. Secondly, circuit topologies of high-speed latch and selector circuits suitable for low-voltage operation are presented. Finally, precise high-frequency device models based on the measured s-parameters up to 40GHz are described. The MUX and DEMUX operate off a single 1.2V supply and consume 110 and 52mA, respectively. Experimental results showed a clear eye opening at a data rate of 40Gb/s. **Keyword:** 40Gb/s, MUX, DEMUX, 90nm CMOS, inductor peaking

## 1. 背景

CMOS テクノロジの急速な進歩に伴って、現在では 10Gb/s で動作する通信用 IC が量産可能なレベルに到達している。ITRS ロードマップによれば、次の技術的課題は CMOS で 40Gb/s の速度を実現することであり、最近の ISSCC でも 40Gb/s 動作する要素回路の発表が相次いでいる[1-10](表 1 参照)。

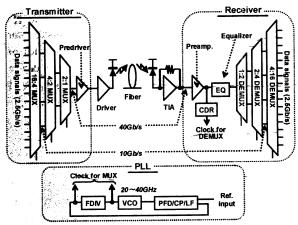

40Gb/s インターフェイスの典型的な構成例を図 1 に示す。CMOS で実現することが期待されているのはグレーの領域である。左側にあるのは、低速なパラレル信号(例えば 2.5Gb/s の信号 16 本)から、40Gb/s のシリ

アル信号を生成するトランスミッタ(TX)である。TX の構成要素は主に MUX とドライバ回路である。右側にあるのは、40Gb/s の信号を受信し、もとのパラレル信号に戻すレシーバ(RX)である。RX の構成要素は入力アンプ、イコライザ、クロック・データ復元回路(CDR)、及び DEMUX である。また、図 1 の下部に示されるように、TX と RX の他に PLL が必要になる。ハーフ・レート方式を用いる場合、PLL の出力周波数は 20GHz になる(フル・レートなら 40GHz)。以下、図 1 の構成において、どの回路ブロックが既に CMOS で実現されているかを簡単に振り返ることにする。

|        | 2002                               | 2003                                       | 2004                                                               |

|--------|------------------------------------|--------------------------------------------|--------------------------------------------------------------------|

| 0.18µm |                                    | 40Gb/s CDR [3]                             | 40Gb/s dist, amp. [9]<br>40Gb/s amp./ESD [8]                       |

| 0.13µm | 25GHz divider [1]<br>51GHz VCO [2] | 40Gb/s 2:1 MUX [4]<br>30Gb/s 1:4 DEMUX [5] | 90GHz dist. amp. [10]                                              |

| 90nm   |                                    |                                            | 43Gb/s 2:1 MUX [7]<br>50Gb/s 2:1 MUX [6]<br>25GHz clock buffer [6] |

表 1: 過去 3 年間の間に ISSCC で発表された 40Gb/s 関係の論文一覧.

まず、TX の中で所望の動作速度を達成するのが難しい回路ブロックは、20Gb/s から 40Gb/s への 2:1 MUX と、入出力共に 40Gb/s で動作する出力ドライバである。このような高速 MUX 回路では、回路の帯域を増加させるためにインダクタ・ピーキングが多用される[4,6,7]。出力ドライバは、インダクタ・ピーキングを用いた CML 回路[7,8]や、分布定数アンプ[9,10]などで実現される。

RXでは、やはり 40Gb/s のデータ信号を扱う入力アンプや 1:2 DEMUX が、動作速度的には厳しい回路になる。インダクタ・ピーキングを用いて 40Gb/s を達成した 1:2 DEMUX[4]や、逆にピーキングを用いずに 30Gb/s を達成した 1:4 DEMUX[5]などが報告されている。入力アンプについては TX 出力ドライバと同じタイプの回路[7-10]が使用可能である。

クロック系の回路では、PLLの中にある電圧制御発振器(VCO) [2]と分周器(FDIV)[1]、クロックを TX に届けるために必要なクロック・バッファ[6]、及び RX のCDR[3]などが CMOS で実現されている。

図 1: 典型的な 40Gb/s インターフェイスの例.

このように、40Gb/s の速度を達成する CMOS 回路はほぼ揃って来てはいるが、これらは最高動作速度が求められる部分のみに注力した要素回路レベルの技術である。そのため高集積化することで面積、電力、コストを低減できる CMOSテクノロジの恩恵を十分に活かしきれていない。このような状況を受けて 2005 年の

ISSCCでは、低速動作する回路部と高速動作する回路部を組み合わせた試作チップが 2 件報告されている [11,12]。ただし 32:1 MUX と PLL を搭載した TX に関する [12]は 130nm 世代のテクノロジを用いているため、動作速度を上げるために 1.5V という比較的高い電圧を回路に加えており、電力も 2.7W と大きい。 40Gb/s のインターフェイスを将来的には high-end ディジタル用途(高速サーバの I/O など)にも使えるようにするためには単一電源で動作し低電力であることが望ましい。

次節以降は主に[11]の内容に沿って 40Gb/s 動作する 4:1 MUX と 1:4 DEMUX について述べる。第 2 節では 本 MUX/DEMUX の構成について説明する。第 3 節では 40Gb/s の動作速度を達成するために必要となる三つの技術的課題について述べる。第 4 節では試作チップの測定結果を示し、第 5 節で結論を述べる。

# 2. MUX/DEMUX の構成

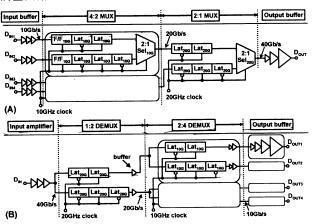

図 2(A)及び(B)に 4:1 MUX  $\ge 1:4$  DEMUX の全体構成を示す。MUX の出力電圧振幅は差動で  $1.2V_{PP}$  とした。 MUX の電力を削減するために、出力にはファン・アウト(以下 F.O.)を 1 以上にとった多段バッファを配置することとした。 DEMUX 側では差動で  $200mV_{PP}$  の入力信号を 18dB のゲインを持つ 3 段構成のアンプで  $1.2V_{PP}$  まで増幅しており、これにより 1:2 DEMUX の動作を保証している。 20GHz のクロック信号はパッドを通して外部から与え、チップ上の 1/2 分周器と位相 調整回路によって 10GHz のクロックを生成している。

図 2: (A)4:1 MUX の構成, (B) 1:4 DEMUX の構成.

MUX と DEMUX は、共に広く用いられている 5-latch アーキテクチャを採用している。20Gb/s-40Gb/s の変換を行う 2:1 MUX と 1:2 DEMUX は、10Gb/s-20Gb/s の変換を行う 4:2 MUX と 2:4 DEMUX に比べて動作速度の要求が厳しいため、異なる回路トポロジを用いて実現

した。4:2 MUX と 2:4 DEMUX は従来の CML タイプの 回路で構成されており、図 2 ではラッチが LAT $_{10G}$ , 2:1 セレクタが SEL $_{10G}$  として示されている。2:1 MUX と 1:2 DEMUX では、より高い帯域を持つラッチ LAT $_{20G}$  と 2:1 セレクタ SEL $_{20G}$  を用いた。

MUX 出力で 1.2Vpp という比較的高い振幅を出すために、全ての内部回路(ラッチやセレクタを指す)の入出力振幅を同一の値 1.2Vpp で設計した。仮に内部回路で振幅を落とすと、出力までのどこかで増幅を行う必要がある。必要な帯域を確保しながら同時にゲインも稼ぐことは、この周波数領域では難しい。また内部回路の振幅を全て統一することで、トランジスタの動作点が限定されるため、設計も大幅に簡易化されるというメリットも生じる。

## 3. 回路設計

40Gb/s の動作速度を 90nm CMOS テクノロジを用いて達成するために直面した技術的課題は主に三つあり、本節ではこれらについて述べる。回路設計における難しさは、「1.2V という低い電源電圧で、このような高速アナログ回路を設計しなければならない」という命題に由来する。課題の一つ目は 40Gb/s 動作する出力バッファの設計である。二つ目はラッチ回路とセレクタ回路の高速化である。三つ目は高周波領域まで正確なデバイスモデルの構築である。

#### A: 40Gb/s 出力バッファ回路

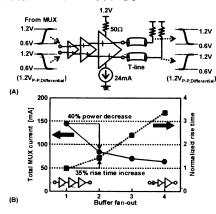

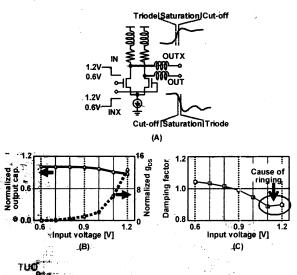

図 3(A)に出力バッファの動作条件を示す。先述の通り入出力の振幅は 1.2V<sub>PP</sub>である。バッファ回路は抵抗負荷型 NMOS 差動 CML 回路である。出力は 50 Ω 系なので最終段のバッファに流す電流は 24mA になる。ここでバッファの F.O.をいくつにするかによって、電力をどの程度減らせるかが決まる。

図 3: (A)出力バッファの動作条件, (B)バッファの F.O.に 関する電力と速度のトレードオフ.

図 3(B)に F.O.に関する電力と速度のトレードオフを示す。 F.O.が 1 から 2 になると電力は 40%減るが、速度も 35%遅くなる。しかし、この 35%という値は、まだ慎重な回路設計によってカバーできる範囲である。 F.O.が 3 以上になると電力削減の効果は小さくなる一方で、動作速度は 2 倍以上遅くなる。この速度劣化を回路設計でカバーすることはきわめて難しい。速度劣化は主に、前段から見た後段の容量性負荷が大きくなることに因る。本設計では F.O.を 2 とした。

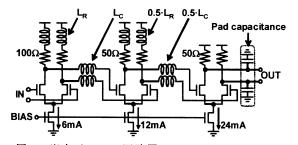

図 4 にトランジスタ・レベルでのバッファ回路を示す。初段のバッファは抵抗負荷型 NMOS 差動増幅器をベースとし、負荷抵抗と直列にインダクタ  $L_R$ を、次段の入力ゲートとの間にインダクタ  $L_C$  を挿入した形になっている。2 段目は初段のトランジスタのサイズを 2 倍にし、抵抗とインダクタを半分の値にしたものである。この回路の重要な設計パタメタは  $L_C/L_R$  である。

図 4: 出力バッファの回路図.

図4の回路トポロジは"Triple-resonance amplifier"として[8]の中に示されており、3つの共振点によってインダクタが全く無い場合に比べて回路の帯域が約3.5倍になる、とされている。しかし本設計と[8]の設計では大きく異なる点が二つある。

まず、[8]ではバッファの入力容量と出力容量の値がほぼ等しいという仮定の下に、最適な $L_c/L_R$ の値が1であることを導出している。これはF.O.が約1の場合に対応しており、本設計のようにF.O.が2の場合には最適な $L_c/L_R$ の値は変わってくる。

次に[8]での解析は動作点まわりで線形化し、トランジスタの  $g_{DS}$  を省略した簡単なものになっている。 際には図 5(A)に示すように、トランジスタは一部の配圧範囲で線形領域に入るため小信号パラメタが大きで変化し、このような線形アンプとしての扱いは不可えるである。図 5(B)に出力ノードの容量値とトランジスタはである。図 5(B)に出力ノードの容量値とトランジスタはである。図 5(B)に出力ノードの容量値とトランジスタによって変化する様子を示した。この結果、図 5(C)に示すようにバッファクタをい値が動作範囲の中で変化し、仮に DC 動作点で $\xi=1$ (臨界制動)となるようにしたとしても、振幅が大きい所では $\xi<1$ となってしまう。この結果、バッファの出力過渡波形に過剰なピー

キングによるリンギングが観測されるようになる。 塞以上の理由から、動作点周りの AC 解析のみではインダク:外の最適化はうまくいかない。AC 解析を用い て帯域を最大化するように設計すると、逆に eye 波形 が乱れることさえある。

図 5: (A)出力バッファでのトランジスタの動作領域. (B)入力電圧に対する容量及び gDS の変化, (C)入力電圧に対するダンピング・ファクタの変化.

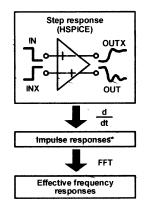

非線形効果の影響がある時にバッファの性能を確認する手段としては、直接出力のアイ波形を見るのがる工確である。しかし SPICE の過渡解析を実行して長いデータ系列に対するアイ波形を得るのには通常多くの時間がかかり、バッファの最適化手段としては多くない。そのため本設計では最適なインダクタのましくない。そのため本設計では最適なインダクタのなった数応答(effective frequency response)を計算することとした。その計算フローを図6に示す。

図 6: 実効的な周波数応答の計算フロー.

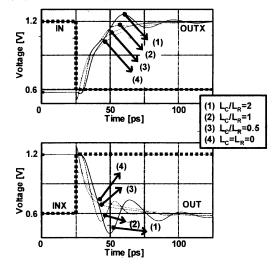

まず HPICE でステップ応答を計算する。入力端子 IN は 1.2V から 0.6V に変化し、INX は 0.6V から 1.2V に変化する。異なる  $L_R$  と  $L_C$  の値に対する出力端子 OUT 及び OUTX の波形を図 7 に示す。このステップ応答は、このような  $1.2V_{PP}$  差動入力の時のみに得られる応答であり、入力振幅を変えた場合の出力波形は、この応答をスケールしても得られない。この 0.6V 入力に対するステップ応答を微分し、さらに FFT をかけることで実効的な周波数応答を得る。この計算フローはソフトウエェアを用いて自動的に回るようにした。このようにして非常に短い過渡解析から、非線形効果を含んだ周波数応答が得られる。

図 7: 4種類の  $L_R$ ,  $L_C$  の値に対してバッファのステップ応答を計算した結果。入力は 0.6V 差動。

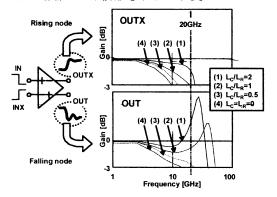

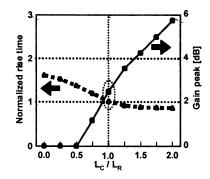

図 8 に得られた実効周波数応答を示す。大振幅入力のため出力の立上がりと立下りで異なる応答を示す。入力と出力は共に 0.6V 振幅であるので DC ゲインは 0dB になる。この図から、バンド幅のワーストケースは出力の立上がり特性から決まり、逆にゲイン・ピークのワーストケースは立下り特性から決まることがわかる。このゲイン・ピークが現れる主な理由はトランジスタが線形領域に入るため、gps が増大することによる。図 8 の結果をゲイン・ピークと信号の立上がり時間のトレードオフとして示したのが図 9 である。本設計では Lc/LR の値として 1 を選んだ。

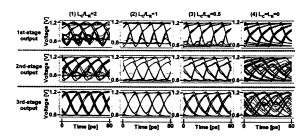

このパラメタ選択が最適かどうかを確認するために、過渡解析を実行して eye 波形をプロットしたのが図 10 である。 $Lc/L_R=2$  の場合、立下り波形のリンギングがアイ波形を大きく乱している。一方  $Lc/L_R=0.5$  の場合、このリンギングは小さくなるが、逆に立上がり特性の劣化によってアイが乱れる。これに対して、 $Lc/L_R=1$  の場合に最も良好なアイ波形が得られており、

実効的な周波数応答から予測された結果と一致している。なお、図には参考のためにピーキング・インダクタが無い場合のアイ波形も示してある。

図 8: OUT 及び OUTX の実効的な周波数応答.

図 9: Lc/LR に関するゲイン・ピークと立上がり時間のトレードオフ.

図 10: 異なる Lc/LR に対してプロットしたアイ波形.

## B: 高速ラッチ回路及びセレクタ回路

ラッチ回路とセレクタ回路は高速化するのが難しい。理由は、二つの差動トランジスタ対が一つの出力ノードに接続されるため、出力ノードの負荷容量が大きくなり帯域を制限するためである。従ってこの帯域ネックとなるノードにおける波形が乱れないように細心の注意が必要である。また、ラッチは10Gb/sの入力を受けた場合出力も10Gb/sで動作するが、セレクタの場合は10Gb/sの入力を二つ受けて20Gb/sの信号を出力する。このためセレクタの方がラッチに比べて高速

化がより厳しくなる。

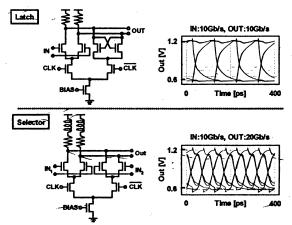

図 11 に 10Gb/s 入力を受けるラッチとセレクタの回路図、及びその動作波形を示す。回路はバッファと同様にポリ抵抗を負荷とした NMOS 差動形の CML 回路であり、幅広く使われてきた回路トポロジである。セレクタの方は出力が 20Gb/s になるため、帯域を増加させるために負荷抵抗に直列にピーキング・インダクタを挿入している。

図 11: 入力が 10Gb/s のラッチ/セレクタ回路、及びその動作波形.

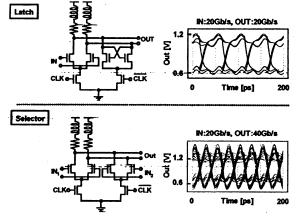

図 12 に 20Gb/s 入力を受けるラッチとセレクタの回路図、及びその動作波形を示す。共にインダクタ・ピーキングを用いて広帯域化を図っている。更にここでは従来の CML 回路の代わりに、定電流源を削除したタイプの回路(以下ではこれを reduced-stack トポロジと呼ぶ)を用いている[6]。1.2V という低電圧で 20Gb/s以上の高速動作をさせるためには、縦積みトランジスタの数を減らした方が有利だからである。

図 12: 入力が 20Gb/s のラッチ/セレクタ回路、及びその動作波形.

reduced-stack トポロジを用いる場合の注意点は二つ

ある。一つ目は、この回路の出力コモン電位は CML 回路のように抵抗と定電流の積で決まらないため、出力波形が乱れやすい点である。そのため、この回路を多段に接続する場合は段数を極力少なくする必要がある。20Gb/s 以上で動くから、と言って同じトポロジを20Gb/s 以下の回路に用いなかったのは、このことによる。また、各段の波形劣化を小さくするために、データ信号用のトランジスタとクロック信号用のトランジスタのサイズ比を慎重に選ぶ必要がある。

二つ目は、CML 方式のラッチやセレクタに比べ、reduced-stack トポロジでは必要になるクロック振幅が大きくなる点である。20GHz のクロックを大振幅でチップ内に分配するのは容易ではない。今回は 20GHz クロックはチップ外部から与え、チップ内での分配にはインダクタ・ピーキングを施した CMOS インバータ[6]を用い、rail-to-rail のクロック信号を MUX/DEMUX に供給した。

#### C: 高周波デバイスモデル

40Gb/s の回路を設計するためには、正確な高周波デバイスモデルが必要である。しかし、通常ファウンドリから提供されるデバイスモデルは低い動作周波数のディジタル回路のために最適化されている。そのため、20GHz程度の周波数領域では実測とモデルが異なる振る舞いをする。回路シミュレーションの信頼性を向上するため、トランジスタ、インダクタ、抵抗やその他の回路素子のデバイス TEG を作成し、40GHz まで sパラメタを測定した。この測定結果をもとにモデルパラメタの抽出を行った。

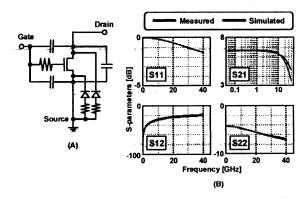

図 13(A)に示すのは、パラメタ抽出の際に用いたトランジスタ・モデルである。モデル化を行ったのは 2 種類のトランジスタである。一つは高速データ及びクロック信号をゲートに受ける、最小ゲート長のトランジスタであり、もう一つは CML 回路の定電流源あるがした長が少し長めのトランジスタでありた。モデル化を行った 2 種類のトランジスタのみを用いている。また、レイアウト・パターンも、グート、ドレイン、ソースの形状はイスと同ーになる、からにしている。そのため、1 種類のトランジスタについて、ゲート幅 W とゲート長さしは固定値のみが許され、設計自由度は finger 数のみになっている。

トランジスタのモデル化では、実測とシミュレーションを合わせこむために5つのパラメータを調整した。それらは、ゲート抵抗、バックゲート抵抗、ドレイン容量、ゲート容量、及びソース容量である。図13(B) にsパラメタのフィッティング結果を示す。約20GHz程度まで良好な一致を示している。

インダクタに関してはRLGCタイプの伝送線路モデルを用いている。MUX と DEMUX の中で用いられるインダクタの多くは負荷抵抗に直列に挿入されるため、インダクタの Q 値は高くなくても良い。一方、出力ドライバで用いられているインダクタ(図 4 の中の Lc と 0.5Lc)については、インダクタの寄生抵抗と次段の入力ゲート容量によってローパス・フィルタの効果が生まれるため、寄生抵抗を極力小さくするようにしている。具体的には上層のメタル 3 層(8,9,10 層)を併走させ、各層の間にはビアを敷き詰めた。この結果、インダクタの Q 値としては約 9 程度の値を得た。

図 13:設計に用いたトランジスタ・モデルとsパラメタ(実測 とモデルのシミュレーションを比較).

## 4. 測定及びシミュレーション結果

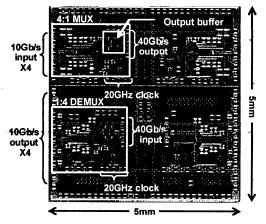

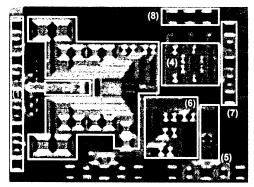

図 14 にチップ写真を示す。5mm 角上に 4 種類の TEG を作成した。テクノロジはディジタル用の 90nm トリプルウェル CMOS プロセスで、メタル層数は 10 である。4:1 MUX の面積は 2.4mm x 1.9mm であり、1:4 DEMUX の面積は 2.4mm x 2.8mm である。1:4 の拡大写真を図 1:5 に示す。

図 14:チップ写真.

- (2) Input buffers

- (3) 4:1 MUX

- (4) Output driver

- (1) 4 pads for 10Gb/s inputs (5) 20GHz clock buffer (6) Frequency divider

- (7)40Gb/s output pad

- (8) Bias pads for the buffer

図 15:MUX 部の拡大写真.

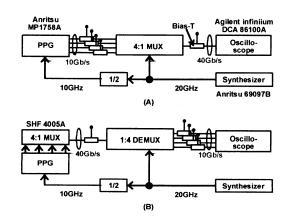

図 16(A)に MUX の測定セットアップを示す。テスト チップはセラミック・パッケージにマウントし、高周 波信号は 50Ωのストリップ線路を介してチップに与 えた。10Gb/s のデータ信号はアンリツ社製の パル ス・パターン・ジェネレータ(MP1758A)を用いて発生 し,1.2V<sub>PP</sub> 20GHz のクロック信号は同アンリツ社製の シンセサイザ(69097B)を用いて発生させた。データ及 びクロック信号は高周波プローブを通してチップに与 え、1.2V 単一電源はボンディングワイヤを通して与え た。出力波形はアジレント社製のオシロスコープ (86100A Infiniium DCA oscilloscope)にて測定した。

図 16(B)に示す DEMUX の測定セットアップは、MUX のセットアップとほぼ同じである。 ただし 40Gb/s の信 号は SHF 社製の 40Gb/s MUX を用いて生成している。

図 16: 測定系、(A)MUX、(B)DEMUX.

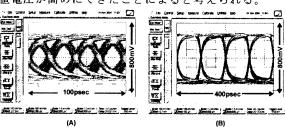

図 17(A)及び(B)に 各々4:1 MUX と 1:4 DEMUX の 出力アイ波形を示す。40Gb/s 動作時の MUX のアイ開 口は約 400mV<sub>PP</sub> であり、 DEMUX のアイ開口は 900mV<sub>PP</sub> である(注:この振幅値は差動信号の振幅)。

入力データパターンは PRBS 2<sup>23</sup>-1 である。MUX のア イはシミュレーションと比べてジッタが大きいが、こ れはプロセスバラツキによってトランジスタのしきい 値電圧が高めにできたことによると考えられる。

図 17: 1.2V 単一電源で 40Gb/s 動作時の測定波形、 (A)MUX, (B)DEMUX.

MUX と DEMUX の電力は各々 132mW と 62mW で あり、この値は 1.2V 単一電源動作させた時のものであ る。チップとテクノロジの概要を表 2 にまとめた。

| テクノロジ | 90nm標準CMOSプロセス                               |

|-------|----------------------------------------------|

|       | トリプル・ウェル、メタル10層                              |

| 電源電圧  | 1 <i>2</i> V(単一)                             |

| 面積    | 2.4 x 1.9mm <sup>2</sup> (MUX)               |

|       | $2.4 \times 2.8 \text{mm}^2 \text{ (DEMUX)}$ |

| 電力    | 132mW (MUX)                                  |

|       | 62mW (DEMUX)                                 |

|       |                                              |

表 2: チップとテクノロジのまとめ

#### 5. 結論

90nm 標準 CMOS プロセスを用いて 40Gb/s 動作する 4:1 MUX と 1:4 DEMUX を試作した。試作回路は、同 世代のディジタル回路と同じ単一電源 1.2V で動作し た。MUX の電力を削減するために、F.O.=2 の出力バ ッファを設計した。1.2Vppの振幅で動作させるため、 顕著になる非線形効果を考慮しながらピーキング・イ ンダクタの最適化を行った。最適化では、従来の AC 解析の代わりに、大振幅ステップ入力から得られる実 効的な周波数特性を用いた。また、高速化が難しいラ ッチ回路やセレクタ回路において、1.2V での動作を可 能にするため、20Gb/s 以上の高速回路(2:1 MUX と 1:2 DEMUX)では、インダクタ・ピーキングと併せて reduced-stack トポロジを用いた。回路シミュレーショ ンの精度を高めるために、デバイスの実測sパラメタ に基づいた高周波デバイスモデルを作成した。これら の結果として、40Gb/s での動作を試作チップで確認す ることができた。MUXと DEMUX の電力は各々132mW と 62mW である。

### 文 献

- [1] H. Knapp, H.-D. Wohlmuth, M. Wurzer, and M. Rest, "25GHz Static frequency divider and 25Gb/s multiplexer in 0.12µm CMOS," IEEE International Solid-State Circuits Conference, pp. 302-303, 2002.

- [2] M. Tiebout, H.-D. Wohlmuth, and W. Simbürger, "A JV 51GHz fully-integrated VCO in 0.12µm CMOS," IEEE International Solid-State Circuits Conference, pp. 300-301, 2002.

- [3] J. Lee and B. Razavi, "A 40Gb/s Clock and Data Recovery Circuit in 0.18µm CMOS Technology," IEEE International Solid-State Circuits Conference, pp. 242-243, 2003.

- [4] D. Kehrer, H. D. Wohlmuth, H. Knapp, M. Wurzer, A. L. Scholtz, "40Gb/s 2:1 Multiplexer and 1:2 Demultiplexer in 120nm CMOS," IEEE International Solid-State Circuits Conference, pp. 344-345, 2003.

- [5] A. Rylyakov, S. Rylov, H. Ainspan, S. Gowda, "A "30Gb/s 1:4 Demultiplexer in 0.12μm CMOS," IEEE International Solid-State Circuits Conference, pp. 176-177, 2003.

- [6] D. Yamazaki, T. Yamamoto, M. Horinaka, H. Nomura, K. Hashimoto, H. Onodera, "A 25GHz Clock Buffer and a 50Gb/s 2:1 Selector in 90nm CMOS," IEEE International Solid-State Circuits Conference, pp. 240-241, 2004.

- [7] T. Yamamoto, M. Horinaka, D. Yamazakil, H. Nomura, K. Hashimoto, H. Onodera, "A 43Gb/s 2:1 Selector IC in 90nm CMOS Technology," IEEE International Solid-State Circuits Conference, pp. -238-239, 2004.

- [8] S. Galal and B. Razavi, "40Gb/s Amplifier and ESD Protection Circuit in 0.18µm CMOS Technology," IEEE International Solid-State Circuits Conference, pp. 480-481, 2004.

- [9] H. Shigematsu, M. Sato, T. Hirose, F. Brewer, and M. Rodwell, "40Gb/s CMOS Distributed Amplifier for Fiber-Optic Communication Systems," IEEE International Solid-State Circuits Conference, pp. 476-477, 2004.

- [10] J. Kim, J.-O. Plouchart, N. Zamdmer, R. Trzcenski, R. Groves, M. Sherony, Y. Tan, M. Talbi, J. Safran, L. Wagner, "A 12dBm 320GHz GBW Distributed Amplifier in a 0.12µm SOI CMOS," IEEE International Solid-State Circuits Conference, pp. 478-479, 2004.

- [1,1] K. Kanda, D. Yamazaki, T. Yamamoto, M. Horinaka.

J. Ogawa, H. Tamura, and H. Onodera, "40-Gbps 4:1

MUX/1:4 DEMUX in 90-nm standard CMOS

technology," IEEE International Solid-State Circuits

Conference, pp. 152-153, 2005.

- [12] J. Kim, J-K. Kim, B-J. Lee, M-S. Hwang, H-R. Lee, S-H. Lee, N. Kim, D-K. Jeong, W. Kim, "Circuit Techniques for a 40Gb/s Transmitter in 0.13μm CMOS," IEEE International Solid-State Circuits Conference, pp. 150-151, 2005.