# 微細MOSFETのリーク電流を考慮した 2電源型システムLSIの低消費電力設計法

渡辺重佳、金井雅樹、永澤晃、花見智、小林学、高畠俊徳 湘南工科大学 情報工学科 〒251-8511 神奈川県藤沢市辻堂西海岸 1-1-25 E-mail: watanabe@info.shonan-it.ac.jp

あらまし 微細 MOSFET の充放電電流、ゲートリーク電流、サブスレッショルドリーク電流による消費電力を考慮した 2 電源型 ( $V_H$ 、 $V_L$ 方式) システム LSI の消費電力の削減効果について解析した。消費電力の削減率は充放電電流のみを考慮した場合には電圧比 $V_L$ / $V_H$ と $V_H$ の絶対値によって決定される。詳細な解析の結果 65nm、45nm、32nm いずれの世代でも従来通り充放電電流による消費電力を最小にする $V_L$ / $V_H$ と $V_H$ の絶対値によって決定される。 詳細な解析の結果 65nm、45nm、32nm いずれの世代でも従来通り充放電電流による消費電力を最小にする $V_L$ / $V_H$ で2 電源方式を最適化すると、リーク電流による消費電力もほぼ最小に出来る。以上の解析より 2 電源型は微細 MOSFET を用いて設計されたシステム LSI にとってリーク電流による消費電力が支配的になる世代でも、低消費電力化にとても有効な方式である事が分かった。

キーワード システムLSI、 2電源方式、充放電電流、 ゲートリーク電流、 サブスレッショルドリーク電流、 MOSFET、 スケーリング則、 パスディレイ分布

## Design method of low-power dual-supply-voltage system LSI

## taking into account leakage current of MOSFET

Shigeyoshi Watanabe, Masaki Kanai, Akira Nagasawa, Satoshi Hanami, Manabu Kobayashi, and Toshitoku Takabatake

Department of Information Science, Shonan Institute of Technology

1-1-25 Tsujido-Nishikaigan, Fujisawa, 251-8511 Japan E-mail: watanabe@info.shonan-it.ac.jp

Abstract Reduction of power dissipation caused by dynamic current, gate leakage current, and subthreshold leakage current of dual-supply-voltage (V<sub>H</sub>, V<sub>L</sub>) system LSI has been analyzed. The reduction ratio of power dissipation due to leakage current is strongly depend on V<sub>H</sub>. Not only dynamic current but also leakage current can be successfully reduced with using conventional dual-supply- voltage scheme for 32nm-65nm generation.

**Keyword** system LSI, dual supply voltage scheme, dynamic current, gate leakage current, subthreshold leakage current, MOSFET, scaling rule, path-delay distribution

### 1. はじめに

MOSFETの微細化が着実に進んでいるシステムLSIでは、90nm以下のデザインルールを用いる事によりGHz動作、GIPSの高速な情報処理能力が実現されている[1][2]。その際高速化に伴い動作時の負荷容量の充放電による消費電力、微細 MOSFETのサブスレッショルドリーク電流による消費電力が増加し、これがシステムLSIの更なる高速化、高機能

化の大きな阻害要因となっている [3] [4]。この問題を解決するために過去多数の低消費電力化手法が提案されてきた [5] ~ [10]。並列処理方式はこれらの消費電力だけでなく 50 n m世代以降に問題となると予測されるゲートリーク電流[11]による消費電力を低減できる特長がある[5]。反面チップ面積が大幅に増加する、チップ全体の構成が複雑になる等の欠点がある。一方 VTCMOS 方式[6]はチップ面積、チップ全体の構成に関しては問題無いがゲートリーク電流による消

費電力を削減出来ない。それに対し2電源( $V_{\text{II}}$ 、 $V_{\text{L}}$ )方式 [7] ~[10]は両者の長所を併せ持ち、チップ面積をほとんど増加させること無くゲートリーク電流分を含めリーク電流による消費電力を削減できる特長を持つ。しかも高速動作が必要な部分を高電圧  $V_{\text{H}}$ で動かし、動作速度が遅い部分を低電圧  $V_{\text{L}}$ で動かすという比較的簡単な構成になっているため現在システム LSI に広く使われている。

2電源方式に関しては過去充放電による消費電力を考慮した場合[7]~[10]、ゲートリーク電流による消費電力のみを考慮した場合[12]の消費電力の削減効果について報告されている。しかし将来の微細MOSFETを用いたシステム LSI で問題となる充放電、サブスレッショルドリーク、ゲートリークを全て考慮した消費電力の削減効果に関する報告はまだ無い。本論文ではこれらを全て考慮した場合の消費電力の削減効果に関して詳細に解析したので報告する。

### 2. 充放電、ゲートリーク、サブスレッショルド リークによる消費電力の削減効果の高電圧 (V<sub>B</sub>) 依存性

2電源電圧方式の有効性の指標として従来消費電力の削減率比Rが広く用いられてきた[8] [10] [12]。本論文でも電力削減効果の指標として用いる。従来の充放電による消費電力のみを考慮した場合の消費電力 $P_D$ は  $V_H=V_L$ の時以下のように表される [8]。

$$P_{\rm p} = (1/2) \ {\rm f} \ \alpha \ {\rm CV_H}^2$$

(1)

ここで f は動作周波数、 $\alpha$  は活性化率、C はシステム LSI の総容量である。 $V_L < V_H$  の場合には(1)は以下のように変形される [8]。

$$P_{p}=(1/2) \text{ f } \alpha C_{VL} V_{L}^{2} + (1/2) \text{ f } \alpha (C-C_{VL}) V_{H}^{2}$$

(2)

ここで $C_{VL}$ は $V_L$ で駆動されるクロック部分の総容量を示す。(1)(2)を用いると充放電のみを考慮した R(以下 Dynamic の頭文字を用いて  $R_D$ と略す)は以下の式で表される [8]。

$$R_{p} = (C_{VL}/C) (V_{L}/V_{H})^{2} + 1 - C_{VL}/C$$

(3)

(3) の計算において $C_{v.L}$ /Cの値はシステム LSI のロジックを構成する各ノードの遅延時間の分布 p (t): パスディレイの分布の値によって異なる。例え

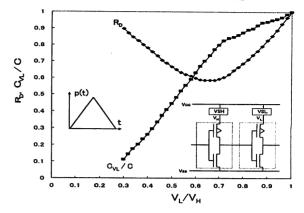

ば代表的な分布"山型"の場合に $R_D$ と $C_{VL}$ /Cは図1のようになる。ここで各 $V_L$ における $C_{VL}$ /Cの値

図1 R<sub>D</sub>、C<sub>VL</sub>/CのV<sub>L</sub>/V<sub>H</sub>依存性

は [8] の $R_D$  の値と(3)から求めた。 $V_L/V_H=0.6\sim0.7$  で $R_D$  は約 0.6 になる。すなわち $R_D$  に $V_L/V_H$  を存性があり、最適な $V_L/V_H=0.6\sim0.7$  では電力は約 6 0%に削減できる。充放電のみを考慮した(3)は電圧に関しては $V_L/V_H$  のみの関数として表され $V_H$  の絶対値に依存しない事が充放電の場合の特徴である。スケーリングが進んだ次世代のシステム LSI でも $V_L/V_H$  の値が同じならばほぼ同じ $R_D$  となる。これは後で述べるゲートリーク、サブスレッショルドリークを考慮した場合との大きな違いとなる。

次にゲートリーク電流のみを考慮した消費電力の削減効果について解析する。ゲートリーク電流による消費電力のみを考慮した場合の消費電力  $P_T$  は  $V_H=V_L$  の時以下のように近似できる「13」。

$$P_T = k A V_H exp (5.6 V_H)$$

(4)

ここでAはシステム LSI におけるMOSFETの総ゲート面積、k は比例定数である。 $V_L < V_H$  の場合には(4) は以下のように変形される。

$$P_{T} = k ((A - A_{L}) V_{H} exp (5.6 V_{H}) + A_{L} V_{L} exp (5.6 V_{L}))$$

(5)

ここで $A_L$ は $V_L$ で駆動されるロジック部分のMO S F E T の総ゲート面積である。Aは総容量C に比例し、 $A_L$ は $V_L$ で駆動される総容量 $C_{V_L}$ に比例するので [12]、

$$A_L/A = C_{VL}/C \qquad (6)$$

(5)(6)を用いてゲートリーク電流のみを考慮した 消費電力の削減率R,は、

$$R_{T} = (C_{VL}/C) \exp (5.6V_{H} (V_{L}/V_{H}-1))$$

$$\times (V_{L}/V_{H}) + 1 - C_{VL}/C \qquad (7)$$

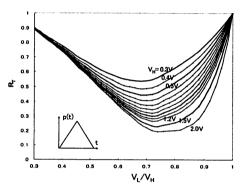

と表される。(7) の特徴は $R_T$ が電圧に関しては $V_L$ / $V_H$ のみでなく $V_H$ の絶対値に依存する事である。これは元々ゲート電流の原因となっているゲート絶縁膜のトンネル電流が電圧の指数関数で表されている事に起因している。図2に $R_T$ の $V_L$ / $V_H$ 依存性を $V_H$ を

図2 R<sub>T</sub>のV<sub>L</sub>/V<sub>H</sub>依存性

次にサブスレッショルドリーク電流のみを考慮した消費電力の削減効果について解析する。サブスレッショルド電流による消費電力のみを考慮した場合の消費電力  $P_S$ は  $V_H=V_L$ の時以下のように近似できる。

$$P_s = b A V_H 1 0^{-(v t - k t V H)/s}$$

(8)

ここで b は比例定数、V t はドレイン電圧が低い場合のしきい値電圧、K 1 はしきい値電圧のドレイン電圧依存性を示す比例定数、S はサブスレッショルドファクタである。 $V_L$  <  $V_H$  の場合には(S)は以下のように変形される。

$$P_{S} = b \left( (A - A_{L}) V_{H} 1 0^{-(V \iota - k 1 V H) / S} + A_{L} V_{L} 1 0^{-(V \iota - k 1 V L) / S} \right)$$

(9)

(6)(9)を用いてサブスレッショルドリーク電流の みを考慮した消費電力の削減率R<sub>s</sub>は、

$$R_{s} = 1 \ 0^{(k_{I}VH (VL/VH-1))/S} \times (C_{VL}/C)$$

$$\times (V_{L}/V_{H}) + 1 - C_{VL}/C \qquad (1 \ 0)$$

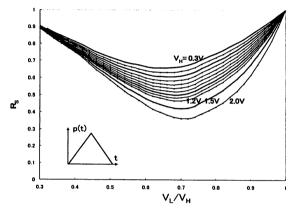

と表される。(10) の特徴は $R_T$ 同様 $R_S$ が電圧に関しては $V_L/V_H$ のみでなく $V_H$ の絶対値に依存する事である。これはサブスレッショルドリーク電流の $V_H$ 依存性が、しきい値電圧のドレイン電圧依存性から発生している事に起因する。図3に $R_S$ の $V_L/V_H$ 依存性

図3 R<sub>s</sub>のV<sub>L</sub>/V<sub>H</sub>依存性

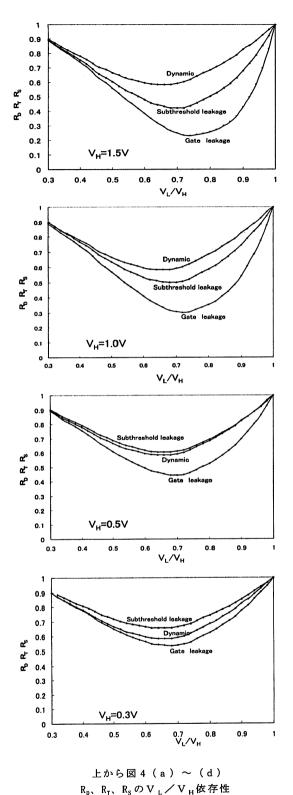

以上の結果よりゲートリーク電流、サブスレッショルドリーク電流による消費電力の削減率には充放電の場合と異なり $V_H$ 依存性があることが分かった。そこで幾つかの $V_H$ で以上の3種の消費電力の削減率を比較した(図4(a)~(d))。ゲート長が0.1um以上の世代に対応する $V_H=1.5V$ では3種類の差は大きい。削減率の最小値、それを実現する $V_L/V_H$ の値(充放電のみの場合には0.66)共に大きな違いが有る。しかしながら $V_H$ の値を下げるに従い(MOSFET の微細化に対応)3種類の差は徐々に小さくなり、 $V_H=0.3V$

程度では削減率、それを実現するV<sub>L</sub>/V<sub>H</sub>の値共に

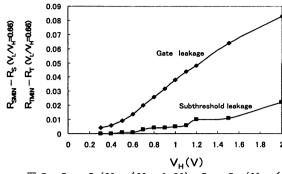

図 5 R<sub>TMIN</sub>-R<sub>T</sub>(V<sub>L</sub>/V<sub>H</sub>=0.66), R<sub>SMIN</sub>-R<sub>S</sub> (V<sub>L</sub>/V<sub>H</sub>=0.66)のV<sub>H</sub>依存性

大差は無くなる。その傾向を更に顕著に示したのが図 5 である。図 5 の縦軸には R<sub>TMIN</sub> (R<sub>T</sub>の最小値) - R<sub>T</sub> (V<sub>L</sub>/V<sub>H</sub>=0.66) 及び R<sub>SMIN</sub> (R<sub>S</sub>の最小値) - R<sub>S</sub> (V \_/VH=0.66)のVH依存性を示す。VHが大きい時に はV」/Vuを充放電を最小にする値に設定するとゲ ートリークやサブスレッショルドリークは最小値より 大きくなる (Vн=2Vの時、ゲートリークで 0.09 程 度)。つまり現在の2電源方式の設計で広く採用されて いるように充放電による電力を最小にするVL/Vu を用いるとゲートリークやサブスレッショルドリーク のよる電力が最小値からずれ余分な電力が発生する。 一方V<sub>1</sub>が小さい時には図4からも予想されるように V./V.を充放電を最小にする値に設定してもゲー トリークやサブスレッショルドリークは最小値よりほ とんど大きくならない事が分かる (V<sub>H</sub>=0.5V の時、 ゲートリークで 0.01 以下)。

### 3. 3種類の消費電力を全て考慮した場合の削減 効果の世代推移

2. では3種類の消費電力の削減率を別々に解析したがここではそれらをまとめて解析し、更にその世代推移に関して考察する。3種類の消費電力の和である $P_{TOT}$ は $V_H=V_L$ の時(1)(4)(8)の和として表される。それを(2)(5)(9)を参考に $V_L<V_H$ の場合に変形し、更に(6)を用い(3)(7)(10)を参考にして計算すると、3種類の消費電力の和の削減率 $R_{TOT}$ は以下のように表わされる。

$$R_{TOT} = (C_{VL}/C) (V_{L}/V_{H}) F (V_{L}) /F (V_{H}) + 1 - C_{VL}/C (1 1) F (V) = 0.5 f \alpha V + b 1 0 - (V_{L}-k_{L}V) /S + k e^{5.6V} (1 2)$$

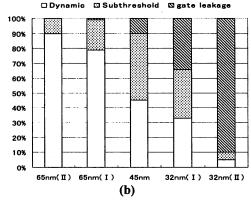

(11) (12) でF ( $V_H$ ) を構成する 3 項の大きさの比を外部から指定すればその時の  $R_{TOT}$  が計算できる。例えば 3 項の大きさの比を  $V=V_H$  で与えれば良い。 3 項の比を各世代毎に示す (図 6)。 65nm 世代の中でサ

| Technology Node    | VH (V) | Dynamic | Subthreshold | gate leakage |

|--------------------|--------|---------|--------------|--------------|

| 65nm(II)           | 1.2    | 0.9     | 0.1          | 0            |

| 65nm( I )          | 1.2    | 0.79    | 0.2          | 0.01         |

| 45nm               | 1      | 0.45    | 0.45         | 0.1          |

| 32nm( I )          | 0.8    | 0.33    | 0.33         | 0.34         |

| 32nm( <b>I</b> I ) | 0.8    | 0.05    | 0.05         | 0.9          |

(a)

図6 各時代での消費電力の推移

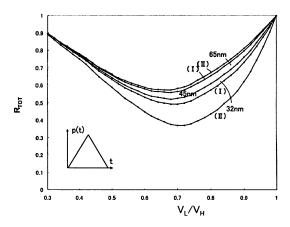

図7 R<sub>TOT</sub>のV<sub>L</sub>/V<sub>H</sub>依存性(世代をパラメータ)

ブスレッショルドリークが少ない物(90nm 世代に近い物)を 65nm( $\Pi$ )とした。また 32nm 世代でゲートリークが多い物(22nm 世代に近い物)を 32nm( $\Pi$ )とした。世代が進むにつれまずサブスレッショルドリークが増加し、更に微細化が進むとゲートリークが増加する。図 7に(11)(12)及び図 6を用いて計算した $R_{TOT}$ の値を示す(山型の場合)。削減率の絶対値に差

はあるものの  $(0.3\sim0.6)$ 、最小値を実現する $V_L/V_H$  の値に殆ど差が無い。その様子を図 8 にまとめた。  $R_{TOTMIN}$  ( $R_{TOT}$  の最小値)  $-R_{TOT}$  ( $V_L/V_H$  = 0.66) の値も小さく現在の設計技術通り充放電電流のみを考慮

| Technology Node | R <sub>TOTMIN</sub> | (V <sub>L</sub> /V <sub>H</sub> )<br>for R <sub>TOTMIN</sub> | R <sub>TOTMIN</sub><br>—R <sub>TOT</sub> (V <sub>L</sub> /V <sub>H</sub> =0.66 ) |

|-----------------|---------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|

| 65nm( II )      | 0.574               | 0.68                                                         | 0                                                                                |

| 65nm( I )       | 0.559               | 0.68                                                         | 0                                                                                |

| 45nm            | 0.521               | 0.68                                                         | 0.004                                                                            |

| 32nm( I )       | 0.492               | 0.69                                                         | 0.006                                                                            |

| 32nm( II )      | 0.369               | 0.72                                                         | 0.007                                                                            |

図8 図7のまとめ、解析結果

して $V_L/V_H$ を設定しても電力削減率の増加は 0.01以下に抑えられる。

以上の結果は以下のように考察される。Vnが高い MOSFET の微細化が余り進んでいない時は、消費電力 の削減率の最小値を与えるVL/Vuの値は充放電電 流とリーク電流では大きく異なる。充放電電流を中心 にVL/VHの値を最適化するとリーク電流が最小値 の時より多く発生する(図5)。しかしその時消費電力 の大部分を充放電電流が占め、リーク電流はわずかし か流れない (図 6)。その結果充放電とリーク電流の両 方を考慮した R<sub>TOT</sub> では絶対値の大きい充放電が支配 的になりその特徴が観察される(図7の65nm世代)。 一方 V<sub>H</sub>が低い MOSFET の微細化が進んだ時は、消費 電力の削減率の最小値を与えるVェ/Vェの値は充放 電電流とリーク電流ではほぼ同じになる (図5)。その 結果消費電力の大部分をリーク電流が占め、充放電電 流は余り流れない(図6)状況でもR<sub>TOT</sub>は充放電を中 心にV<sub>L</sub>/V<sub>H</sub>の値を最適化しても良い(図7の 32nm 世代)。以上のような結果が得られるのはリーク電流の 削減効果に強い VH依存性があるためである。

### 4. むすび

微細 MOSFET の充放電電流、ゲートリーク電流、サブスレッショルドリーク電流による消費電力を考慮した 2 電源型( $V_H$ 、 $V_L$ 方式)システム LSI の消費電力の削減効果について解析した。消費電力の削減率は充放電電流のみを考慮した場合には低電圧との比 $V_L$ / $V_H$ によって決定されるのに対し、リーク電流のみを考慮した場合には $V_L$ / $V_H$ と $V_H$ の絶対値によって

決定される。詳細な解析の結果  $65\,\mathrm{nm}$ 、  $45\,\mathrm{nm}$ 、  $32\,\mathrm{nm}$  いずれの世代でも従来通り充放電電流による消費電力を最小にする  $V_L/V_H$ で 2 電源方式を最適化すると、リーク電流による消費電力もほぼ最小に出来る。以上の解析より 2 電源型は微細 MOSFET を用いて設計されたシステム LSI にとってリーク電流による消費電力が支配的になる世代でも、低消費電力化にとても有効な方式である。

#### 謝辞

本研究を遂行するにあたって幾つかの有益なコメントをいただいた東京工業大学の松澤昭先生(低消費電力全般、ゲートリーク電流)、芝浦工業大学の宇佐美公良先生(しきい値電圧のドレイン電圧依存等)、東京大学の池田誠先生(低消費電力全般)、宮城工業専門学校の桜葉弘先生(ゲートリーク電流の電圧依存性等)に深謝致します。

#### 文献

- [1]D. C. Pham, et al., "Overview of the architecture, circuit design, and physical implementation of first-generation cell processor," IEEE JSSC vol. 41, no. 1, pp. 179-196, 2006.

- [2]S. Naffziger, B. Stackhouse, T. Grutkowski, D. Josephson, J. Desai, E. Alon and M. Horowitz, "The implementation of 2-Core, Multi-threaded Itanium family processor," IEEE JSSC vol. 41, no. 1, pp. 197-209, 2006.

- [3] Gorden E. Moore, "No exponential Is forever: But "Forever" can be delayed," ISSCC invited papers, 2003.

- [4]SIA 半導体ロードマップ 2 0 0 3 年版

- [5]渡辺重佳、"微細 MOSFET のリーク電流を考慮したシステム LSI の高速低消費電力設計法の検討、" 信学論 (C)、vol.86-C, no.9, pp.1034-1035, Sept. 2003.

- [6]T. Kuroda et al, "A 0.9-V, 150-MHz, 10-mW, 4mm2, 2D discrete cosine transform core processor with variable threshold-voltage (VT) scheme," IEEE JSSC vol.31, no.11, pp.1770-1779, 1996.

- [7]K. Usami and M. Horowitz, "Clustered voltage scaling technique for low-power design," Proc. Of the International Symp. Of Low Power design, pp. 3-9, 1995.

- [8]M. Hamada et al, "A Top-down low power design technique using clustered voltage scaling with

- variable supply-voltage scheme," Proc. CICC pp. 495-498, 1998.

- [9]K. Usami and M. Igarashi, "Low power design methodology and applications utilizing dual supply voltages," Proc. CICC pp. 123-126, 2000.

- [10]桜井貴康、"低消費電力、高速 LSI 技術" リアライズ社 1998.

- [11]S. Lo et al., "Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultra-thin oxide nMOSFETs," IEEE Trans. Electron Device Lett., vol. 18, no. 5, pp. 209-211, 1997.

- [12] 渡辺重佳、"微細 MOSFET のゲートリーク電流の低消費電力用 2 電源方式に及ぼす影響に関する検討、"信学論(C)、vol. 86-C, no. 6, pp. 658-660, June. 2003. [13] http://www.ssc.pe.titech.ac.jp/class/class\_j.htm

- [14]L. Yan, J. Luo and N. Jha, "Joint dynamic voltage scaling and adaptive body biasing for heterogeneous distributed real-time embedded systems," IEEE Trans. CAD Desin of Integrated Circuits and Systems, vol. 24, no. 7, pp. 1030-1041, 2005.

- [15]M. Hamada et al., "Utilizing surplus timing for power reduction," Proc. CICC pp. 89-92, 2001.