# 高信頼セルによる演算器の耐故障性と遅延時間の評価

鈴 木 一 範<sup>†1</sup> 中 田 尚<sup>†1</sup> 中 西 正 樹<sup>†1</sup> 山 下 茂<sup>†1</sup> 中 島 康 彦<sup>†1</sup>

トランジスタの性能ばらつきおよびトランジスタの故障率増大に対する解決策として、我々は高信頼セルを提案している。本報告ではセルの耐故障性を評価する指針として、レイアウトを用いた新しい故障モデルを提案する。新しい故障モデルを用いて耐故障性を評価した結果、高信頼セルを用いて構成された回路は従来セルを用いて構成された回路より高い耐故障性を備えていることがわかった。またアナログシミュレーションの結果、回路について故障を正しく検知できることを確認した。さらに、入力値に依存しない耐故障性を確認するための LSI の設計手法について述べる。

## A Functional Unit with Highly Reliable Cells and its Evaluation of Fault tolerance and Delay Time

Kazunori Suzuki, $^{\dagger 1}$  Takashi Nakada, $^{\dagger 1}$  Masaki Nakanishi, $^{\dagger 1}$  Shigeru Yamashita $^{\dagger 1}$  and Yasuhiko Nakashima $^{\dagger 1}$

We have proposed highly reliable cells to solve an increase in transistor variation and in failure rate of transistors. In this paper, we propose a new fault model that uses the cell's layout as a guideline of evaluating fault tolerance of the cells. We evaluate fault tolerance based on new fault model and show that the circuit composed of highly reliable cells is better than the circuit composed of traditional cells. We performed analog simulation and show that the circuit can detect faults. In addition, we describe how to design an LSI that evaluates the fault tolerance that does not depend on input values.

## 1. はじめに

近年、プロセス微細化によってトランジスタの性能 ばらつきが大きくなる傾向にある. ばらつきの中でも 特に関値電圧とゲート長のばらつきが多くを占めている. 1)-4). これらのばらつきは遅延時間を悪化させ、結果として高速化や低消費電力化といった最適化の実現が困難となる. また、プロセス微細化によってトランジスタの故障率も増加する傾向にある. 故障率が増加することによって回路の歩留まり率が減少する.

上記の問題に対する解決策として,我々は少品種の高信頼セルを提案した<sup>5),6)</sup>.このセルは伝送ゲートを基本単位として構成されており,かつトランジスタが規則的に配置されている.規則的に配置することによってトランジスタの性能ばらつきを抑え,歩留まり率を向上させる<sup>7)</sup>.また少品種によっても性能ばらつきを抑える.提案したセルは以下の機能を持つ.

- (1) ある一定数以下の PMOS もしくは NMOS が 故障しても正しい値を出力する

- (2) 一定数よりも多く故障した場合は故障している

#### †1 奈良先端科学技術大学院大学 Nara Institute of Science and Technology

### ということが検出できる

本論文では従来セルおよび高信頼セルの耐故障性を 評価する指針として、レイアウトを用いた新しい故障 モデルを提案する.次に高信頼セルを用いて構成され た演算器の入力値に依存しない耐故障性を確認するた めの LSI の設計手法について述べる.

以降の本論文の構成は以下の通りである。まず2章ではセルのレイアウトを用いた新しい故障モデルについて述べる。3章では2章で述べた故障モデルを用いて演算器の耐故障性を評価する。4章では、2章で述べた故障が発生しているセルを埋め込んだ回路のシミュレーション結果を示す。5章では現在のシミュレーション評価の問題点、およびその解決方法として現在試作を行っている高信頼セルを埋め込んだ LSI の設計手法について述べる。最後に6章でまとめを述べる。

#### 2. レイアウトを用いた故障モデル

本節ではセルの耐故障性を評価する指針として,従来セルおよび高信頼セルのレイアウトを用いた新しい故障モデルについて述べる.高信頼セルの概要は文献6)で述べられているので,本論文では省略する.

従来の故障モデルは、セル内の任意のトランジスタ

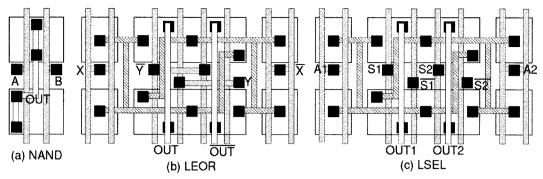

**図1 NAND**, LEOR, LSEL のレイアウト

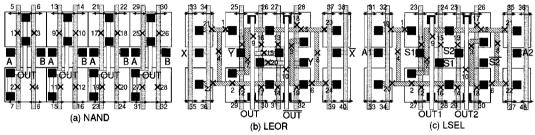

図 2 NAND, LEOR, LSEL の故障箇所

が確率 p で故障しており、故障が発生したトランジスタは動作しないというものであった。しかし実際の回路において発生する故障では、トランジスタそのものが動作しないという故障だけでなく配線のオープン故障なども存在する。つまり、トランジスタに故障が発生しているという故障モデルだけでは現実の故障を反映していないといえる。そこで我々は従来セルおよび高信頼セルのレイアウトを用いた新しい故障モデルを提案する。

図1(a) は NAND のレイアウトを示している. 同様に(b) は LEOR のレイアウトを,(c) は LSEL のレイアウトを示している. 我々はセル内に発生する故障を以下のように仮定した.

- (1) セル内の任意の1本の配線が断線する(オープン故障)

- (2) PMOS, あるいは NMOS 内でのオープン故障, 特にソース・ドレイン間のオープン故障が発生 する

従来の故障モデルは(2)の PMOS あるいは NMOS のオープン故障にあたる. 我々は従来の故障モデルである MOS のオープン故障に加えて、配線のオープン故障を新しく付け加えた上で耐故障性を評価する.

図 2 は各セルにおける典型的な故障箇所を示している。図 2 において  $\times$  は配線のオープン故障を,  $\leftrightarrow$  は MOS のオープン故障を示している。図 2 (a) では NAND を 4 つ並べているが, これは NAND の面積と LEOR, LSEL の面積を等しくさせるためである。

まず配線のオープン故障について説明する. NAND において、図 2 (a) で示した配線のオープン故障のどれか 1 つでも発生したとする. 図 2 (a) で示す故障箇所はすべてゲート信号を供給する配線上である. 故障が発生することにより、ゲート信号が供給されないのでは供給されなくなる. ゲート信号が供給されないのでトランジスタは正常な値を出力することができない.よって、回路全体としても正常に動作しない.

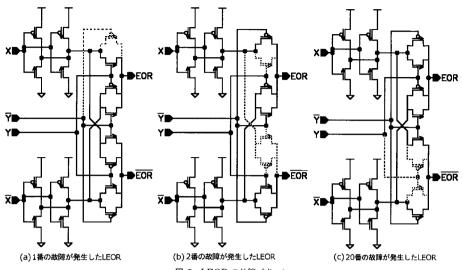

LEOR, LSEL では配線のオープン故障が発生した場合は 3 つのパターンが存在する. 図 3 中において点線の部分はオープン故障によって故障したトランジスタを示している. 図 3 (a) は LEOR において 1 番の  $\times$  で故障が発生した場合を示している. この故障パターンでは 1 つのトランジスタに影響を与える.

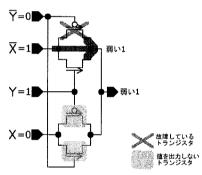

図 3 (a) のような故障が発生した場合の動作について述べる。図 4 は EOR を出力する回路である。図 4 は図 3 (a) と同様の箇所のトランジスタが故障している場合を示している。入力信号のうち Y は 1 であり、 $\overline{Y}$  は 0 なので、4 つあるトランジスタのうち下 2 つのトランジスタにはゲートに電圧がかからず、値を出力しない。よって、図 4 では上から 2 番めにある NMOS のみが動作し値を出力する。NMOS への入力は 1 であり、また NMOS は 1 を通しにくいという特徴があるので、この NMOS は弱い 1 を出力する。同様に、PMOS への入力が 0 の場合、PMOS は弱い 0 を出力する。他の配線のオープン故障についても、トランジスタ 1 つのみに影響を与える故障パターンの場

図 3 LEOR の故障パターン

合は正常に動作する.

図3 (b) は2番の×で故障が発生した場合を示している。2番の×で故障が発生した場合、3つのトランジスタに影響を与える。特に $\overline{EOR}$ を出力する4つのトランジスタの中で2つが故障している。この2つは伝送デートを構成してたトランジスタである。伝送ゲートを構成していたトランジスタが故障しているので $\overline{EOR}$ は正常な値を出力しない。結果として図3(b)は回路全体として正常に動作せず異常値を出力する。

図 3 (c) は 20 番の  $\times$  で故障が発生した場合を示している. 20 番の  $\times$  で故障が発生した場合, 2 つのトランジスタに影響を与える. この 2 つのトランジスタは伝送ゲートを構成するペアではないので, 結果として回路は正常に動作する.

また 21番の×で故障が発生した場合は、伝送ゲートを構成するトランジスタに影響は与えない。しかしインバータから1が出力されないので、回路は正常に動作せず異常値を出力する。同様に4番の×で故障が発生した場合でもインバータの出力が伝送ゲートに正常に伝わらないので回路は正常に動作せず異常値を出力する。

次に MOS のオープン故障について説明する. MOS のオープン故障は MOS のソース・ドレイン間が接続されていない状態とみなすことができる. つまりオープン故障した MOS は正常に動作しない. NANDでは MOS のオープン故障が発生した場合, その MOS は正常な値を出力せず回路は正常に動作しない. しかし LEOR や LSEL において MOS のオープン故障が発生している状態は図 3 (a) と同じ状態であり,回路全体としては正常に動作する.

図4 1箇所故障が発生した場合の挙動

#### 3. 新しい故障モデルを用いた耐故障性の評価

本節では、2節で述べた新しい故障モデルを用いて 演算器の耐故障性について評価を行った。評価を行っ た演算器は文献 6)で述べられている従来セル(3重 化)で構成された比較器と高信頼セル+EOR(2重化) で構成された比較器である。

評価においては故障率pを単位面積あたり1つ故障が発生する確率とし、また単位面積にはトランジスタが16 個含まれているとした。つまり、NANDでは図2 (a) に示すように単位面積あたり4つの NANDが含まれている。LEOR および LSEL では単位面積あたりそれぞれ1つの LEOR と LSEL が含まれている。従来セルを用いて構成された64 ビット比較器には63 個の2 ビット比較器は4つの NANDで構成されているので、単位面積の数は63 となる。高信頼セルを用いて構成された64 ビット比較器には63 個の2 ビット

表 1 高信頼セル(2重化)における出力パターン

|      |       |      | 回路 A  |       |

|------|-------|------|-------|-------|

|      |       | 正常   | 検出可能  | 間違った値 |

|      | 正常    | 正常   | 正常    | 検出可能  |

| 回路 B | 検出可能  | 正常   | 検出可能  | 間違った値 |

|      | 間違った値 | 検出可能 | 間違った値 | 間違った値 |

比較器と 120 個の LEOR が含まれている、 高信頼セ ルの 2 ビット比較器は 2 つの LSEL で構成されてい るので、高信頼セルの 64 ビット比較器には 126 個の LSEL が存在する.

従来セル、および高信頼セルの歩留まり率はセルが 正しい値を出力する確率とする. また従来セルを用い て構成された回路では、1つでもセルが壊れている場 合を回路が故障しているとみなす.よって従来セル(3 重化)で構成された回路における故障とは、3つある 回路のうち2つ以上の回路で故障が発生している状態 となる.

高信頼セルを用いて構成された回路では以下に示す 3つの出力パターンが存在する.

- 回路が正常値を出力する(正常)

- 回路が異常値を出力する(検出可能)

- 正負が逆転した値を出力する(間違った値)

正常値を出力する場合とは回路内のセルが全く故障 していない、あるいは異常値を出力するような故障が 発生していない場合である. 異常値を出力する場合と は、回路内のセル1つで異常値を出力するような故障 が発生している場合である. 本論文では, 高信頼セル で構成された回路の歩留まり率を、回路が正常値ある いは異常値を出力する確率とする。正しい値を出力す る確率を $p_1$ , 異常値を出力する確率を $p_2$  とした場合, 回路の歩留まり率は $p_1+p_2$ となる。また、故障率は  $1-(p_1+p_2)$  と表す事ができる. 高信頼セル (2 重化) で構成された回路の場合、各回路それぞれにおいて3 つの出力パターンがあるので、回路全体における出力 パターンは9つとなる. 表1に全パターンを示す. 高 信頼セル(2重化)で構成された回路における歩留ま り率は表1における「正常」と「検出可能」にあたる. また故障率は表1における「間違った値」にあたる.

故障率 p を単位面積あたり故障が 1 箇所発生する 確率とした場合、単位面積あたりの NAND の故障率 は p, LEOR の故障率は 8/40p, LSEL の故障率は 8/38p となる. 故障率 p は非常に小さいので、8/40pと 8/38p はほぼ等しいとみなすことができる. よって 以下の議論では LEOR の故障率を 8/38p とする. 加 えて、64 ビット比較器は246 個の単位面積で構成さ れているとする. 各回路の故障率は以下のように表す ことができる.

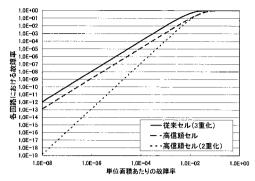

図 5 各回路における故障率

表 2 シミュレーション条件

| 故障させたセル | LSEL           |

|---------|----------------|

| 故障箇所    | 20番の×          |

| 入力パターン  | A > B から A < B |

$$f(p) = 1 - (1 - p)^{63} \tag{1}$$

$$F(p) = f(p)^3 + {}_{3}C_{1}f(p)^2(1 - f(p))$$

(2)

$$F(p) = f(1-p)$$

(1)

$$F(p) = f(p)^{3} + {}_{3}C_{1}f(p)^{2}(1-f(p))$$

(2)

$$g_{1}(p) = (1 - \frac{8}{38}p)^{246}$$

(3)

$$g_2(p) = {}_{246}C_1(\frac{8}{38}p)(1 - \frac{8}{38}p)^{245} \tag{4}$$

$$g_3(p) = 1 - (g_1(p) + g_2(p)) \tag{5}$$

$$G(p) = (g_3(p))^2 + {}_2C_1(g_2(p))(g_3(p))$$

(6)

f(p) は従来セルを用いて構成された 64 ビット比較 器の故障率を示している. F(p) は従来セル (3 重化) で構成された比較器の故障率を示している.  $g_1(p)$  は 高信頼セルを用いて構成された比較器が正常値を出力 する確率を示している.  $g_2(p)$  は高信頼セルを用いて 構成された比較器が異常値, つまり検出可能な値を出 力する確率を示している.  $g_3(p)$  は高信頼セルを用い て構成された比較器の故障率を示している. G(p) は 高信頼セル(2重化)で構成された比較器の故障率を 示している.

**図5**は確率pを $10^{-8}$ から1まで変化させた場合の 各回路における故障率を示している.図5から,高信 頼セルは従来セルより耐故障性に優れており、また高 信頼セル(2 重化)は高信頼セルよりも耐故障性に優 れていることが分かる.

### 4. 故障を含む回路のシミュレーション評価

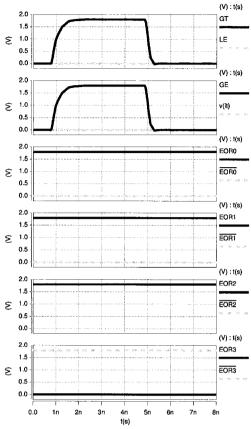

本節では2節で説明した、異常値を出力する故障を 含む回路に対してシミュレーションを行った. シミュ レーション条件を表2に、シミュレーション結果を 図6に示す.

入力パターンは A > B から A < B へと変化する. A > B という入力に対しては GT, GE が 1 を出力

図 6 故障を含む回路の出力結果

する. 逆に A < B という入力に対しては LE, LT が 1 を出力する.

A > B という入力に対しては図 6 内の GT, GE は 1 を, LE, LT は 0 を出力している. GT, GE, LE, LT の出力を見る限り、これは正しい出力であるといえる. しかし、EOR に注目した場合、EOR2 および  $\overline{EOR2}$  は異常値を出力している. このことから内部で 故障が発生していることが分かる.

A < B という入力に対しては GT, GE, LE, LT 全てが 0 を出力しており、この出力は異常値となる。 また EOR2 および  $\overline{EOR2}$  も異常値を出力しており、このことからも内部で故障が発生していることを示している.

#### 5. 考 察

4節で示したように、シミュレーション上では異常値を出力する故障を含む回路は異常値を出力する事が分かった.異常値を出力する故障を含む回路が正しく動作していることを確認するには、入力信号パターン

を調整し、実際に異常値が出力されることを確認する必要がある。しかし異常値を出力しないような故障パターンの場合は、全ての入力パターンにおいてその回路が異常値を出力しない事を確認する必要がある。64ビット比較器だと全ての入力パターンは 2<sup>128</sup> 個となり、HSPICE を使ったシミュレーションでは時間がかかりすぎるという問題がある。そこでシミュレーション高速化のために LSI の試作を行う。

#### 5.1 試作 LSI の設計方法

本節では 64 ビット比較器を評価する LSI の設計方法について述べる. 試作する LSI において使用する比較器は 2 重化しておらず, 選択回路を設置していない単体の比較器とする. 評価する項目は次の 2 点である.

## (1) 耐故障性

比較器内のセル1個において故障が発生した場合でも正常に動作する(正常に動作する故障の場合), 異常値が出力される(異常値が発生する故障の場合)ことを示す

#### (2) 遅延時間

故障を含まない比較器と故障を含む比較器とでは、出力にどれぐらいの遅延が発生するのかを 計測する

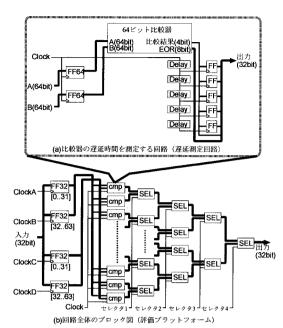

(1) を評価するために、1 箇所故障した比較器を複数個用意する。それぞれの比較器において故障している箇所は異なっている。また、複数個ある比較器のうち1つだけ選択して LSI の外部に出力させるために、比較器の後方にセレクタを設置する。(2) についてであるが、正確な遅延時間を測定することは難しい。64 ビット比較器の演算時間は約 1ns 前後であり、オシロスコープ等で測定できないからである。よって試作する LSI 内に遅延時間を測定する回路を組み込む必要がある。以上 2つの項目を満たした LSI 全体のブロック図を図 7 に示す。本論文では図 7 (a) に示す比較器の遅延時間を測定する回路を組み込んだ LSI 全体を評価プラットフォームと呼ぶ。図 7 においてバッファを一部省略している。

まず図 7 (a) の遅延測定回路から説明する.図 7 (a) 中の Delay はインバータを 4 つ直列に接続した回路である.遅延測定回路は演算器である 64 ビット比較器、比較器の前にある FF64、比較器の前にある FF64 は 64 ビットの値を保持しておく事ができる.FF64 は各入力用に 2 個設置されている.FF64 を設置することによって C に依の立ち上がりと同時に FF64 に格納されている信号を比較器に入力することができる.比較器の後ろにある FF は 4 ビット保持でき、入力信号として比較結果 4 ビットが与えられている.5 つある FFに入力される C になり上でり違する.よって、FFが比較結果を取り込むタイミングはすべて異なっ

図7 遅延時間測定回路および回路全体のブロック図

ている. 比較結果の信号が到達するより前のタイミングで Clock が到達した FF は比較結果を取り込む事ができない. 逆に, 比較結果の信号が到達するより後のタイミングで Clock が到達したどの FF も比較結果を保持することができる. よって, どの FF 以降で比較結果を保持しているかによって遅延時間の測定を行うことが可能となる.

次に図 7 (b) の評価プラットフォームについて説明する. 評価プラットフォーム内には遅延測定回路が 16 個設置されている. 16 個のうち 15 個は 64 ビット比較器の一部で故障が生じている回路である. 先に述べたように、これら 15 個の比較器の故障箇所は全て異なっている. 今回は故障している部位を LSEL のみとした. 評価プラットフォームでは 32 ビットのビット幅を使って入力信号 128 ビット分を生成する. そのために 32 ビット保持できる FF32 と 4 つのクロック信号を使用する. セレクタ 1 からセレクタ 4 は 16 個ある遅延測定回路のうち 1 つのみを選択して外部に出力するためのセレクタ信号である. セレクタである SEL は高信頼セルである LEOR で構成されている.

#### 6. まとめ

我々はトランジスタの性能ばらつきおよびトランジスタの故障率増大に対する解決策として、少品種の高信頼セルを提案した。このセルは壊れにくい、故障が発生した場合はその故障を検出できる、故障検出機能を演算器に埋め込む事ができるという特徴がある。

本論文ではセルの耐故障性を評価するための指針として、従来のトランジスタが確率 p で壊れるという故障モデルの代わりにレイアウトを用いた故障モデルを新しく提案した。提案した故障モデルを用いて 64 ビット比較器の耐故障性の評価を行った結果、高信頼セルを用いて構成された比較器より耐故障性に優れている事が分かった。また、故障を含む回路はシミュレーション上では異常値を出力している事が分かった。さらに入力値に依存しない耐故障性を確認するために、比較器を含む遅延測定回路および評価プラットフォームの設計手法について述べた。

今後は VDEC を通じて試作された LSI を使っての評価を行う予定である.

謝辞 本研究の一部は科学研究費補助金(基盤研究(B)課題番号 19300012)による。また、本研究は東京大学大規模集積システム設計教育研究センターを通し、シノプシス株式会社、日本ケイデンス株式会社、ローム(株)および凸版印刷(株)の協力で行われたものである。

## 参考文献

- Berkelaar, M. and Jacobs, E.: "Sources and quantification of delay variations in a 250nm CMOS digital cell library", Proceedings of International Workshop on Logic Synthesis, pp. 335–339 (1998).

- Orshansky, M., Spanos, C. and Hu, C.: "Circuit performance variability decomposition", Proceedings of International Workshop on Statistical Metrology, pp.10-13 (1999).

- Orshansky, M., Milor, L., Chen, P., Keutzer, K. and Hu, C.: "Impact of systematic spatial intra-chip gate length variability on performance of high-speed digital circuits,", Proceedings of IEEE/ACM International Conference on Computer-Aided Design, pp.62-67 (2000).

- Nassif, S.: "Within-chip variability analysis", IEEE International Electron Devices Meeting Technical Digest, pp.283-286 (1998).

- 5) 鈴木一範, 中田 尚, 中西正樹, 山下 茂, 中 島康彦: "細粒度命令分解と少品種セルによる高 信頼化アーキテクチャの提案", 情処研報, 2007-ARC-175, pp.61-66 (2007).

- 6) 鈴木一範,中田 尚,中西正樹,山下 茂,中 島康彦: "少品種高信頼セルによる演算器の提案 と評価",信学技報,CPSY2007-80,pp.167-172 (2008).

- MUTA, H. and ONODERA, H.: "Manufacturability Aware Design of Standard Cells", IE-ICE Trans. Fundamentals, E-90A, NO.12, pp. 2682–2690 (2007).