# 不揮発性 FF を用いた CGRA 設計探索のためのばらつきを 考慮した MTJ への書き込みエネルギー推定モデルの提案

亀井 愛佳 $^{1,a)}$  天野 英晴 $^1$  小島 拓也 $^2$  横山 大輝 $^3$  宮内 陽里 $^3$  宇佐美 公良 $^3$  平賀 啓三 $^4$  鈴木 健太 $^4$  別所 和宏 $^4$

概要:粗粒度再構成可能アーキテクチャ CGRA は電力効率に優れたデバイスであり,さらに磁気トンネル接合(MTJ)ベースの不揮発性フリップフロップ(NVFF)を利用した NV Power Gating と組み合わせることで非稼働時の静的消費電力を削減できるため,バッテリ駆動を強いられるエッジ環境におけるアクセラレータとして期待される.我々は過去に,MTJ ベース NVFF の欠点である大きいストアエネルギーを削減するための改良版 NVFF を採用した CGRA を提案し,実チップ評価により一定の条件におけるエネルギーの削減効果を示した.しかし,ストアエネルギーは動作電圧,周波数及びストアする NVFF の数といったアプリケーションごとに異なる条件に依存するため,条件ごとに最適な NVFF やストア手法を選択することが必要である.ただし,あらゆる条件で実機測定を行うは非効率的であり,また,わずかな設計変更を反映したチップを再実装することは現実的に難しい.本研究では,様々な条件下における MTJ へのストアエネルギーを算出可能なモデル式を提案する.ストア時間を設定するために必要な MTJ のスイッチング遅延時間の推定については,本質的にばらつきを含む確率的な量であるため,実測結果に対する近似を用いて解析的に算出する手法を提案し,エネルギー推定モデルに組み込んだ.提案モデルは,最適なストア手法の選択において,実測結果と同様の判断を導くことが可能であることから,十分な実用性を持つと言える.

キーワード: CGRA, 粗粒度再構成可能アーキテクチャ, 不揮発性メモリ, 磁気トンネル接合

# A Variation-Aware MTJ Store Energy Estimation Model for Design Exploration of CGRA with Nonvolatile Flip-Flops

#### 1. はじめに

近年、注目度が高まっている IoT やエッジコンピューティングのアプリケーション実行環境においては、バッテリ駆動などエネルギーに関する制約が厳しい中で AI 処理や画像処理といった多様で高い性能要求に対処する状況が想定される。こうした要求に応える低消費電力で高性能かつフレキシブルなデバイスの1つに粗粒度再構成可能アーキテクチャ(coarse-grained reconfigurable architecture:CGRA)がある。同じく再構成可能なアクセラレータとして広く普及している FPGA は、ビットレベルの再構成に

より高い柔軟性を提供しうるが、再構成にかかるオーバー ヘッドの高さに課題がある.一方 CGRA はワードレベル の再構成により適度な柔軟性と電力効率を両立する.

また、間欠動作をすることの多い IoT アプリケーションの特性上、不揮発性メモリ(non-volatile memory: NVM)を使用した不揮発性パワーゲーティング(NVPG)による非稼働時のリーク電力の削減も有効である。特に、MTJ(magnetic tunnel junction)を記憶素子に用いた STT-MRAM(spin-transfer torque magnetoresistive RAM)は、電流により MTJ の磁化を反転させることでデータの書き換えを行い、値を不揮発に保持する仕組みを持ち、高速な書き込み・読み出し性能、高い CMOS 互換性等のメリットから有望な NVM 技術の 1 つとして注目されている。

しかし STT-MRAM はストア(MTJ 磁化反転)エネルギーが高いという欠点があり、これまでにストアエネルギーの低減を目的とした改良版の STT-MRAM ベース FF が提案されてきた [1-4]. 以前我々は、すべての記憶素子

<sup>&</sup>lt;sup>1</sup> 慶應義塾大学大学院 理工学研究科 Kejo University

<sup>&</sup>lt;sup>2</sup> 東京大学大学院 情報理工学系研究科 The University of Tokyo

芝浦工業大学大学院 理工学研究科 Shibaura Institute of Technology

<sup>4</sup> ソニーセミコンダクタソリューションズ株式会社 Sony Semiconductor Solutions Corporation

a) wasmii@am.ics.keio.ac.jp

#### 情報処理学会研究報告 IPSJ SIG Technical Report

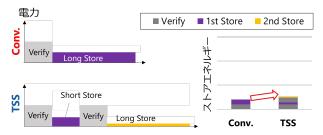

(a) ストアするNVFF数が多い場合: $E_{\text{Conv.}} > E_{\text{TSS}}$

(b) ストアするNVFF数が少ない場合: $E_{Conv.} < E_{TSS}$

図 1 各ストア手法での電力推移とストアエネルギー比較

で改良版 NVFF を使用した NVCMA/MC (Non-volatile cool mega array/ Multi-context)を設計・チップ実装した [5]. 採用した Verify-and-Retriable NVFF (VR-NVFF) [4] は、MTJ のスイッチング遅延時間(磁化反転が生じるまでの時間)が確率的にばらつく性質 [6] を考慮した Two-step Store (TSS) 制御というストアエネルギー削減手法を提供する. 従来のストア手法では1回のストア動作ですべての MTJ のスイッチングを完了させるために、十分に長い時間すべての NVFF に対して電流を流す. 一方 TSS 制御では、1回目の短時間のストア動作後、ストアの成功可否を検証 (Verify)し、失敗した NVFF に対してのみ十分な時間をかけて再度ストア (Retry)する仕組みであるため、従来手法のようにストアを早々に成功させた NVFF に対して電流を流し続けるというエネルギーの浪費が少ない (図 1(a)).

NVCMA/MC の実機評価 [5] では、2,400 個の NVFF に ストアする場合、従来手法と比較して TSS 制御ではエネル ギーが 65%削減できることが示された (図 1(a) のパター ン). 一方, 100 個程度の少ない数の NVFF をストアする 場合には、Verify 動作のオーバーヘッドが少ない従来手法 の方がエネルギー消費が小さかった (図 1(b) のパターン). 実際にアプリケーションごとにストアする NVFF 数、要求 される動作電圧・周波数等の条件は異なり、それによって ストアエネルギーは変化する. つまり, アプリケーション ごとに選択すべきストア手法が異なることがわかった. ま た、Verify 動作はあるまとまったメモリ領域に対して一斉 に実行されるため、Verify エネルギーはそのメモリ領域の サイズに依存する. すなわち、ストアエネルギーはメモリ 領域の分割方法によっても左右される.NVCMA/MC で は、ストアエネルギーを削減する手段として TSS 制御の ほかにエラー訂正機能を使用してストア時間を短縮する機 能を持つが、様々な条件ごとに最適なストア手法を決定するためにすべてのパターンで実測定を行うことは非効率的である。また、異なるメモリ分割方法でのチップ実装を行うことは現実的に難しい。

本研究では、実チップの実測結果に基づいた、NVFFストアエネルギー推定モデルを提案する. ばらつきを含みむため確率的な挙動となる MTJのスイッチング遅延時間についても実測に基づく解析モデルを作成し、ストアエネルギー推定モデルに統合した. これにより TSS 制御によるストアエネルギーも算出可能となる. 本モデルを使用することで、アプリケーションの要求により様々に異なる条件下におけるストアエネルギーを推定・比較し、各条件に適したストア手法の選択及び NVM の設計探索を容易にする.

### 2. 関連研究

TSS 制御によるストアエネルギーを推定するためには、 1度目のストア動作終了時に何個の NVFF がストアに成功し、残りの何個の NVFF に対して再ストアすべきかを知る必要がある. しかし、MTJ のスイッチング遅延時間は確率的な量であり、値を推定するための複雑な物理シミュレーションに基づく解析モデルが提案されている.

Zhang らは、数日要するマイクロ磁気シミュレーションの結果として得られたスイッチング遅延時間の分布は、ストア電流の大きさに応じて正規分布あるいは指数分布の確率分布関数に従うと仮定した解析モデルを導いた [7]. Vincent らは、Zhang らのモデルでは表現できない中間的な電流領域におけるスイッチング遅延時間をガンマ分布を用いてモデル化した [8]. 中間的な電流領域においてはスイッチング遅延時間の確率分布は正規分布より左に歪んだ形状となり、さらに低電流領域では指数分布に類似するが、ガンマ分布を用いることですべての電流領域でモデル化できることが示された。De Rose らは、磁化が空間的に非一様であることを考慮したマイクロ磁気シミュレーションと回路シミュレーションを組み合わせて得られた結果に対して歪正規分布の確率分布関数で近似した [9].

上記の先行研究においては、いずれもシミュレーション結果に基づく解析モデルであり、実測結果との比較は行われていない.本研究では、実際に CGRA のメモリとして実装された 2,400 個の NVFF をチップ上で観察した結果を基に解析モデルを導くため、精度が実測結果に裏付けられたより実用性の高いモデルを得ることが期待できる.

#### 3. 背景

本章では背景として本研究の対象とする VR-NVFF と NVCMA/MC のアーキテクチャの概要に触れた後, NVC-MA/MC において NVFF を制御する仕組み, またそれを生かしたストアエネルギー削減手法である TSS 制御につ

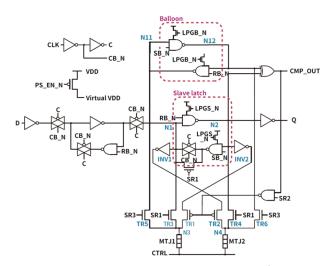

図 2 Verify-and-Retriable NVFF 回路

いて述べる.

#### 3.1 Verify-and-Retriable Non-volatile Flip-Flop

STT-MRAM ベース FF の欠点であるストアエネルギー 削減のため改良された NVFF の 1 つ [1] は、FF のデータ が書き換わる都度 MTJ へのストアを行うのではなく、PG 直前などの必要な時のみストアを行う制御機構でストア回 数を削減した.Selective Storing NVFF[2] は、現在 MTJ が保持するデータとストアするデータが異なる場合にのみ 選択的にストアを行う Data Aware Store 機能によりさらにエネルギーを削減した.

VR-NVFF(図 2)は,MTJのスイッチング遅延時間のばらつきを考慮してさらにストアエネルギー削減を図っている [4]. 一般的なマスタースレーブ型 FF にバルーンラッチ及び 2 つの MTJ を付加した構成により Verify 機能を提供する点が特徴である.Verify 動作では,MTJのデータをバルーンラッチへ読み出し,XOR ゲートを用いてスレーブラッチのデータと比較する.このとき,MTJ とスレーブラッチの値が等しければ XOR ゲート出力 CMP\_OUTは "0" になる.そして CMP\_OUT によってトランジスタ TR1 及び TR2 は強制的にオフとなって MTJ への電流が遮断されることで無駄な電力消費を回避する.

VR-NVFF の制御は、8 つの NVFF 制御線と PG 制御線及びクロックゲーティング制御線の計 10 本の信号線により行うが、NVCMA/MC ではこれらの制御線を 3.3 で説明する  $\mu$  コントローラの専用命令によって制御する.

#### 3.2 NVCMA/MC アーキテクチャの概要

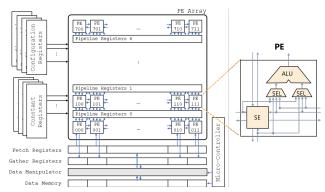

NVCMA/MCは、超低消費電力 CGRA である CMA アーキテクチャ [10] を基に、すべてのメモリ要素を NVFF で置換したエッジ用アクセラレータである。 4つの異なるコンフィグレーションデータを切り替えて実行するマルチコンテキスト機能も備えている。図 3 にアーキテクチャを示

図 3 NVCMA/MC のアーキテクチャと PE 内部の簡略図

す. Straight Forward CGRA の一種であり、RISC タイプの ISA を提供する  $\mu$  コントローラでデータフローを制御して、Processing Element(PE)アレイでの演算を実行する。各 PE の演算やデータパスの再構成はタスク単位で静的に行い、また PE 内にレジスタファイルを持たずクロック分配が不要な構造であるため動的電力が低く抑えられる.

NVCMA/MC は 5 万個以上の NVFF を内蔵し、表 1 に示すように、パワードメイン(PD)及びストアドメイン(SD)という 2 つの分類によって NVFF を分割して制御する。 PD は PG を行う単位であり、PD ごとに独立に電源を制御できる。 24 個の SD は NVFF 制御を行う単位である。 Store 動作や Verify 動作などの NVFF 制御は、次節で説明する  $\mu$  コントローラの専用命令により SD ごと一斉に行う。 SD あたりの NVFF 数は 800~4416 個と様々である。

表 1 NVCMA/MC のパワードメインとストアドメイン

| ,     |                                                                       |                                                                                                        |

|-------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| ストア   | 説明                                                                    | NVFF 数                                                                                                 |

| ドメイン  |                                                                       |                                                                                                        |

| 0-1   | μ コントローラの命令メモリ                                                        | 4096                                                                                                   |

| 2-4   | コンテキスト 0                                                              | 7111                                                                                                   |

| 5-7   | コンテキスト 1                                                              | 7111                                                                                                   |

| 8-10  | コンテキスト 2                                                              | 7111                                                                                                   |

| 11-14 | コンテキスト 3                                                              | 7111                                                                                                   |

| 15-18 | データメモリ バンク 0                                                          | 10272                                                                                                  |

| 19-23 | データメモリ バンク 1                                                          | 11616                                                                                                  |

|       | ドメイン       0-1       2-4       5-7       8-10       11-14       15-18 | ドメイン  0-1 μコントローラの命令メモリ  2-4 コンテキスト 0  5-7 コンテキスト 1  8-10 コンテキスト 2  11-14 コンテキスト 3  15-18 データメモリ バンク 0 |

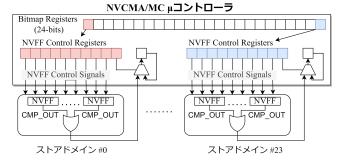

#### 3.3 NVFF 制御命令

VR-NVFF の制御には $\mu$  コントローラの NVC (NV Control) 命令を使用する. 図 4 に NVC 命令によって NVFF を制御する概略図を示す. 24 ビットのビットマップレジスタを使って制御する SD を指定し, NVC 命令により NVFF 制御信号に対応するレジスタに 0 または 1 を書き込むことで, NVFF を SD 単位で制御する. Verify 動作や Store 動作も複数の NVC 命令の組み合わせにより実現される.

#### 3.4 Two-step Store 制御によるストアエネルギー削減

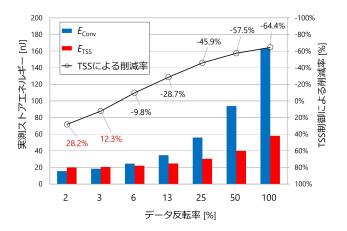

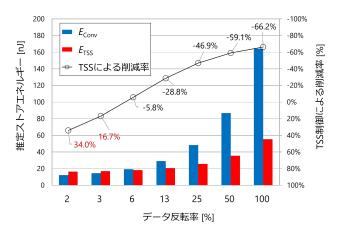

TSS 制御においては,1回目のストア時間は短く設定(ショートストア)し,2回目のストアは十分に長い時間を設定(ロングストア)する.従来手法では1回のロングストアのみを行う.文献 [5] では,ショートストア時間  $T_{\rm short}=35\,\mathrm{ns}$ ,ロングストア時間  $T_{\rm long}=140\,\mathrm{ns}$  と設定した時 TSS 制御の合計ストアエネルギーが最小化され,従来手法に対して最大 65%の削減となる一方,条件によっては従来手法が優れるケースがあることが示された.実チップ(#77)で動作周波数  $f=28\,\mathrm{MHz}$ ,動作電圧  $V_{\rm DD}=1.15\,\mathrm{V}$  において SD15(NVFF 数は 2,400 個)のストアエネルギーを実測した結果を図 5 に示す.横軸のデータ反転率は,SDあたりのストアを行う NVFF 数を意味する.確かに従来手法と TSS 制御のいずれが省エネルギーになるかはデータ反転率に依存することがわかる.

ここで、動作周波数、動作電圧、ストア時間、SDの分割方法等の条件を変更した場合にいずれの手法が優れているのかという疑問が生じる。電力効率を追求するためにNVFFを採用するデバイスの設計探索ではストアエネルギーは重要な要素だが、あらゆる条件でチップ試作・測定することは非効率的である。次章では実装済みチップの測定データを基に、様々な条件におけるストアエネルギーを推定するためのモデルを提案する。

図 4  $\mu$  コントローラによる SD 単位の NVFF 制御

図 5 実測による従来手法と TSS 制御ストアエネルギー及び TSS 制御によるエネルギー削減率

## 4. ストアエネルギー推定モデルの提案

本章では異なる動作電圧,ストア時間,ストア手法におけるストアエネルギーの推定モデル式を提案し,実測値との比較してその有用性について議論する.

#### 4.1 ストアエネルギー推定モデル

式 (1) にロングストアを 1 回だけ行う従来手法によるストアエネルギー  $E_{\text{Conv}}$  と TSS 制御によるストアエネルギー  $E_{\text{TSS}}$  の推定モデル式を示す.

$$E_{\text{Conv}} = E_{\text{verify}} + E_{\text{long\_1st}} + E_{\text{base\_Conv}}$$

$$E_{\text{TSS}} = E_{\text{verify}} + E_{\text{short\_1st}}$$

$$+ E_{\text{verify}} + E_{\text{long\_2nd}} + E_{\text{base\_TSS}}$$

$$(1)$$

このとき  $E_{\text{base\_Conv}}$  及び  $E_{\text{base\_TSS}}$  は式 (2),  $E_{\text{verify}}$  は式 (4),  $E_{\text{long\_1st}}$ ,  $E_{\text{short\_1st}}$  及び  $E_{\text{long\_2nd}}$  は式 (5) で表される.

$$E_{\text{base}_{-}\{\text{Conv},\text{TSS}\}} = E_{\mu} + E_{\text{leak}}$$

$$= (P_{\mu} + P_{\text{leak}}) \times T_{\{\text{Conv},\text{TSS}\}}$$

(2)

$E_{\mathrm{base\_Conv}}$  及び  $E_{\mathrm{base\_TSS}}$  は, $\mu$  コントローラの動作に要する動的エネルギー  $E_{\mu}$  及び NVCMA/MC の静的エネルギー  $E_{\mathrm{leak}}$  の和であり,その電力はストア手法によらず一定である. $T_{\mathrm{Conv}}$  及び  $T_{\mathrm{TSS}}$  は各ストア制御に必要なクロック数(それぞれ 18 と 23)とクロック周期の積である.ここで,一般に動的電流  $I_{\mathrm{dynamic}}$  は,スイッチング電流  $I_{\mathrm{sw}}$  及び貫通電流  $I_{\mathrm{sc}}$  の和であり,本提案では式(3)の形でモデル化する.

$$I_{\text{dynamic}} = I_{\text{sw}} + I_{\text{sc}}$$

$$= k_{\text{sw}} V_{\text{DD}} + (k_{\text{sc}} V_{\text{DD}} - b)$$

$$= k V_{\text{DD}} - B$$

(3)

ここで、 $k_{\rm sw}$ 、 $k_{\rm sc}$ 、k 及び B は定数である.貫通電流は CMOS トランジスタのドレイン電流として考えることが でき [11]、ゲート電圧が一定以上の時その I-V 特性は切片 が負の一次関数で近似可能である [12]. さらに、スイッチング時の貫通電流は時間に対して線形に変化すると仮定する [13] ことにより、式 (3) のとおり平均の貫通電流は  $V_{\rm DD}$  に対して負の切片を持つ線形の式として近似可能である.

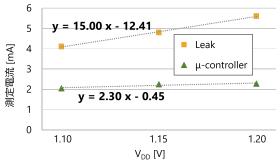

$\mu$  コントローラでの NOP 命令実行時における動的電流  $I_{\mu}$  の測定結果を図 6 (a) に示す. 測定時の動作周波数  $f{=}28{\rm MHz}$  とした. この結果から  $V_{\rm DD}$  に対する動的電流は、切片が負である一次式で近似可能であることが確認できた. 従って  $P_{\mu}$  (=  $I_{\mu} \times V_{\rm DD}$ ) は、図 6 (a) の結果  $I_{\mu}=2.30V_{\rm DD}-0.45$  を用いて任意の電源電圧において算出できる. 異なる  $f[{\rm MHz}]$  においても  $\frac{f}{28}$  を掛けることで

算出可能である.  $P_{leak}$  についても,実測結果から切片が負である一次式による近似が可能であるとわかった.

$$E_{\text{verify}} = P_{\text{verify}} \times T_{\text{verify}} \times N_{\text{SD}} \tag{4}$$

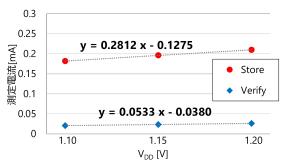

$E_{\text{verify}}$  は、Verify 動作時に MTJ の値を読み出すために消費されるエネルギーである.1 つの NVFF に対する Verify 電力  $P_{\text{verify}}$  は  $P_{\mu}$  と同様に、実測結果(図 6 (b))から求められる. $T_{\text{verify}}$  は Verify に要する時間(2 クロック分)、 $N_{\text{SD}}$  は SD あたりの総 NVFF 数である.

$$E_{\text{long\_1st}} = P_{\text{store}} \times T_{\text{long}} \times N_{\text{store}}$$

$$E_{\text{short\_1st}} = P_{\text{store}} \times T_{\text{short}} \times N_{\text{store}}$$

$$E_{\text{long\_2nd}} = P_{\text{store}} \times T_{\text{long}} \times N_{\text{store}} \times (1 - \frac{PR}{100})$$

(5)

$E_{\mathrm{long\_1st}}$  は 1 度きりのロングストア(従来手法)で MTJ に値を書き込むためのエネルギー, $E_{\mathrm{short\_1st}}$  及び  $E_{\mathrm{long\_2nd}}$  は TSS 制御による 1 度目のショートストアと 2 度目のロングストアでそれぞれ必要なエネルギーである。 $P_{\mathrm{store}}$  は,MTJ に値を書き込むための電力であり,実測結果(図 6 (b))を基にモデル式を作成した。 $N_{\mathrm{store}}$  はストアを行う NVFF 数である。PR は SD 全体でストアが成功したビットの割合を示すストア成功率(Pass Rate)であり,式 (6) で定義される。

$$PR[\%] = \frac{\# of \ successfully \ stored \ NVFFs}{N_{\rm SD}} \times 100 \quad (6)$$

PR はストア時間が長いほど,また動作電圧が高いほど 100%に近づくが,MTJ のスイッチング遅延時間のばらつきのために PR の値を予測することは難しい.次節では,第 2 章で紹介した物理シミュレーションによるアプローチとは異なり,実測に基づく PR の推定モデルを提案する.

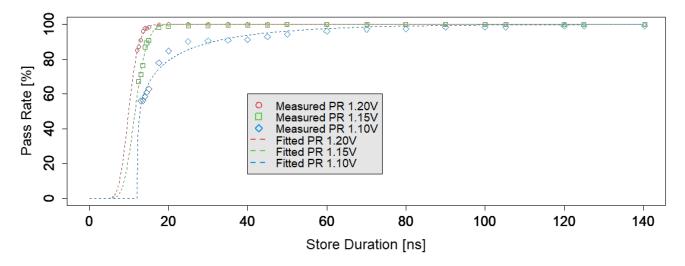

#### 4.2 ストア成功率推定モデル

MTJ のスイッチング遅延時間がある確率分布関数に従うと仮定すると、PR はその累積分布関数に従うことになる。本研究では、 $V_{\rm DD}$ =1.10、1.15、1.20V において様々なストア時間での PR を実測した結果に対して、ガンマ分布の累積分布関数に従うと仮定して最小二乗法によりフィッティングした。図 7 に結果を示す。実測結果は、Vincentらによる物理シミュレーション [8] と同様に  $V_{\rm DD}$  の低下に伴って正規分布的な形状から指数分布的な形状へと遷移しており、ガンマ分布によって実測の PR を概ねトレースできた。これにより各  $V_{\rm DD}$  における任意のストア時間に対する PR を算出することが可能となり、式 (4) を用いた TSS制御ストアエネルギーを推定することができる.

(a) チップ全体の静的電流とμコントローラの動的電流

(b) Verify及びStore動作におけるNVFF1個あたりの消費電流

図 6 実測した各動作電圧  $V_{\rm DD}$  における消費電流とその近似直線(動作周波数  $f=28{

m MHz}$ )

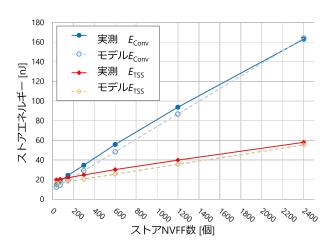

#### 4.3 実測ストアエネルギーとの比較結果

図 8 に各ストア手法でのストアエネルギーの実測値と提案モデル式による推定値を示す。算出条件は図 5 の測定条件と同様に f=28MHz, VDD=1.15V, NSD=2,400, TShort=35ns, Tlong=140ns とした。表 2 に両者の誤差と誤差率を示す。データ反転率が低いとき,エネルギーの絶対値が小さいため誤差率が 20%程度にまで大きくなるが,誤差は 8nJ 未満に収まった。

表 2 推定モデルによる算出結果と実測値との比較

| データ反転率 | 誤差 [nJ] |       | 誤差率 [%] |      |

|--------|---------|-------|---------|------|

| [%]    | Conv.   | TSS   | Conv.   | TSS  |

| 2      | -3.21   | -3.40 | 21.0    | 17.2 |

| 3      | -3.74   | -3.54 | 20.4    | 17.2 |

| 6      | -5.08   | -3.83 | 20.8    | 17.4 |

| 13     | -5.64   | -4.13 | 16.2    | 16.7 |

| 25     | -7.55   | -4.80 | 13.5    | 15.9 |

| 50     | -6.99   | -4.82 | 7.4     | 12.1 |

| 100    | -0.13   | -3.13 | 0.1     | 5.4  |

図 9 はモデル算出値を用いて、図 5 と同様に従来手法と TSS 制御のストアエネルギーを比較した結果である。図 5 と図 9 のグラフは酷似しており、いずれもデータ反転率が 3-6%以上の時に TSS 制御のストアエネルギーが従来手法 を下回る結果を示している。すなわち、実測定を行わずとも推定モデル式によって得られた結果から最適なストア手

図 7 各動作電圧における実測したストア成功率 PR とガンマ分布の累積分布関数による近似曲線

法が選択できるということであり、本提案モデルの一定の 有用性が認められたと言える.

図8 実測及び推定モデルによる算出ストアエネルギー

図 9 推定モデルによる従来手法と TSS 制御ストアエネル ギー及び TSS 制御によるエネルギー削減率

#### 5. まとめ

MTJ ベースの NVFF を採用した CGRA アクセラレータ NVCMA/MC のストアエネルギーを算出するモデル式を提案した。また、確率的な量である MTJ のスイッチング遅延時間をガンマ分布で近似することによって、異なる動作電圧に対する MTJ のストア成功率を解析的に算出する手法を採用した。これにより、動作電圧、動作周波数、データ反転率などのアプリケーションごとに異なる条件において、TSS 制御を含む異なるストア手法によるストアエネルギーを推定し比較することが可能となった。また、SDあたりの NVFF 数という実際にはアーキテクチャの設計変更が必要なパラーメータも変数として入力できるため、NVFF を用いたメモリの設計探索に活用できる。モデルによる推定エネルギーは実測結果と比較して十分な類似性を持ち、データ反転率ごとのストア手法の選択において、実測結果を同様の判断を導くことができることを示した。

今後は、動作電圧やストア時間などが異なる条件においても同様の評価を行い、提案モデルの実用性をより広く評価する。また、NVCMA/MCが備えるエラー訂正機能を利用したストア手法や、他の改良型 NVFF を使用した場合等より多くの選択肢に対するストアエネルギーを推定・比較できるよう拡張するとともに、実際のアプリケーション実行時の評価を行えるようサイクルアキュレートシミュレータ CubeSim[14] への統合を目指す.

#### 参考文献

Yamamoto, S., Shuto, Y. and Sugahara, S.: Nonvolatile delay flip-flop using spin-transistor architecture with spin transfer torque MTJs for power-gating systems, *Electronics letters*, Vol. 47, No. 18, pp. 1027–1029 (2011).

- IPSJ SIG Technical Report

- [2] Kudo, M. and Usami, K.: MTJ Based Non-Volatile Flip Flop to Prevent Useless Store Operation, ITC-CSCC: International Technical Conference on Circuits Systems, Computers and Communications, pp. 515–518 (2015).

- [3] Kudo, M. and Usami, K.: Nonvolatile power gating with MTJ based nonvolatile flip-flops for a microprocessor, 2017 IEEE 6th Non-Volatile Memory Systems and Applications Symposium (NVMSA), IEEE, pp. 1–6 (2017).

- [4] Usami, K., Akaike, J., Akiba, S., Kudo, M., Amano, H., Ikezoe, T., Hiraga, K., Shuto, Y. and Yagami, K.: Energy Efficient Write Verify and Retry Scheme for MTJ Based Flip-Flop and Application, 2018 IEEE 7th Non-Volatile Memory Systems and Applications Symposium (NVMSA), IEEE, pp. 91–98 (2018).

- [5] Kamei, A., Kojima, T., Amano, H., Yokoyama, D., Miyauchi, H., Usami, K., Hiraga, K., Suzuki, K. and Bessho, K.: Energy saving in a multi-context coarse grained reconfigurable array with non-volatile flip-flops, Proceedings of MCSoC 2021 (2021).

- [6] Devolder, T., Hayakawa, J., Ito, K., Takahashi, H., Ikeda, S., Crozat, P., Zerounian, N., Kim, J.-V., Chappert, C. and Ohno, H.: Single-shot time-resolved measurements of nanosecond-scale spin-transfer induced switching: Stochastic versus deterministic aspects, *Phys-ical review letters*, Vol. 100, No. 5, p. 057206 (2008).

- [7] Zhang, Y., Zhao, W., Prenat, G., Devolder, T., Klein, J., Chappert, C., Dieny, B. and Ravelosona, D.: Electrical Modeling of Stochastic Spin Transfer Torque Writing in Magnetic Tunnel Junctions for Memory and Logic Applications, *IEEE Transactions on Magnetics*, Vol. 49, No. 7, pp. 4375–4378 (online), DOI: 10.1109/T-MAG.2013.2242257 (2013).

- [8] Vincent, A. F., Locatelli, N., Klein, J., Zhao, W. S., Galdin-Retailleau, S. and Querlioz, D.: Analytical Macrospin Modeling of the Stochastic Switching Time of Spin-Transfer Torque Devices, *IEEE Transactions on Electron Devices*, Vol. 62, No. 1, pp. 164–170 (online), DOI: 10.1109/TED.2014.2372475 (2015).

- [9] De Rose, R., Lanuzza, M., Crupi, F., Siracusano, G., Tomasello, R., Finocchio, G., Carpentieri, M. and Alioto, M.: A Variation-Aware Timing Modeling Approach for Write Operation in Hybrid CMOS/STT-MTJ Circuits, IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 65, No. 3, pp. 1086–095 (online), DOI: 10.1109/TCSI.2017.2762431 (2018).

- [10] Ozaki, N., Yasuda, Y., Izawa, M., Saito, Y., Ikebuchi, D., Amano, H., Nakamura, H., Usami, K., Namiki, M. and Kondo, M.: Cool Mega-Arrays: Ultralow-Power Reconfigurable Accelerator Chips, *IEEE Micro*, Vol. 31, No. 6, pp. 6–18 (online), DOI: 10.1109/MM.2011.94 (2011).

- [11] Veendrick, H. J.: Short-circuit dissipation of static CMOS circuitry and its impact on the design of buffer circuits, *IEEE Journal of Solid-State Circuits*, Vol. 19, No. 4, pp. 468–473 (1984).

- [12] Harris, D. and Weste, N.: Cmos vlsi design, ed: Pearson Education, Inc (2010).

- [13] Hirata, A., Onodera, H. and Tamaru, K.: Estimation of short-circuit power dissipation and its influence on propagation delay for static CMOS gates, 1996 IEEE International Symposium on Circuits and Systems. Circuits and Systems Connecting the World. ISCAS 96, Vol. 4, IEEE, pp. 751–754 (1996).

- [14] 小島拓也,池添赳治,天野英晴: 3 次元積層 SiP を用いたマルチコアシステムのためのサイクルアキュレートシミュレータ CubeSim の開発,電子情報通信学会論文誌

D, Vol. 104, No. 4, pp. 228–241 (2021).