3K-08

# PC-FPGA 複合クラスタによる HD 動画像の変換 —PC 1 台・FPGA 1 台構成におけるラプラシアンフィルター

武吉 達哉<sup>†</sup>, 尾崎 亮<sup>†</sup>, 上嶋 明<sup>†</sup>, 小畑 正貴<sup>†</sup> 岡山理科大学工学部情報工学科<sup>‡</sup>

# 1. はじめに

多数の PC をネットワーク接続して並列処理を行うクラスタシステムは価格性能比の優れた高性能計算システムとして注目されている[1][2]. これらの利用形態として、Microsoft の Catapult[3]のような大規模検索エンジンなどがあり、このようなシステムでは低消費電力化を目的として FPGA も一部使われるようになっている。また、このようなシステム上では画像を使うこともしばしばあり、画像処理もおこなわれるが、前述の消費電力の観点からGPU が利用されないこともある。そこで、例えば、HD動画像の変換などをPC、FPGA、GPUが混在するクラスタシステム上で実現できれば、必要に応じて、処理性能、消費電力をバランスして取捨選択することができ、便利であろうと考えられる。

本研究の目的は、以上のような背景における基礎研究として、当研究グループが提案済みの PC-FPGA 複合クラスタ[4]の最も単純な構成に対し、FPGA/GPU を利用した際の HD 動画像のラプラシアン変換時の処理性能や消費電力を明らかにすることにある.

以下、2章では PC-FPGA 複合クラスタの概要を説明する、3章では実験装置について示し、4章でシステム構成について説明する、5章で実験結果を示し、6章でまとめを述べる、

### 2. PC-FPGA 複合クラスタ

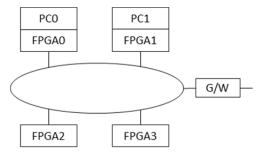

PC-FPGA 複合クラスタの全体構成を図 1 に示す FPGA0 及び FPGA1 はそれぞれ PC0 及び PC1 の拡張スロットに接続された FPGA ボード (以下,内蔵 FPGA という)であり,FPGA2 と FPGA3 は単体で自立した FPGAボード (以下,自立 FPGA という)である.PCには基本的に内蔵 FPGAが存在する.また,自立 FPGA は PC 以外の装置に組み込まれる場合もある.自立 FPGA に必要な機能は FPGA 間ネットワークのための物理層 (LVDSなど)であり.内蔵 FPGA ボードでは,これに加えて PC

HD video image conversion by PC-FPGA Hybrid Cluster -Laplacian filter in constituted of a PC and a FPGA -Takeyoshi Tatsuya<sup>†</sup> Ozaki Ryo<sup>†</sup> Uejima Akira<sup>†</sup> Kohata Masaki<sup>†</sup>

Department of Information and Computer Engineering, Okayama University of Science<sup>†</sup> と接続するためのホストインターフェース (PCI など) が 必要になる. 市販の多くの FPGA ボード (内蔵型, 自立型, 組み込み型) は汎用コネクタを持っており, 基本的に はこれを FPGA 間接続に利用する. PC・内蔵 FPGA のペア, 自立 FPGA, ゲートウェイ (G/W) のそれぞれが構成 単位 (以下, ノードという) となる.

複合クラスタ上に作成可能なユーザアプリケーション(以下、ユーザ機能という)として、PC上でのソフトウェア(以下、ユーザプロセスという)と、FPGA上の回路(以下、ユーザ回路という)がある。ユーザプロセスはPC上の単独プロセスとして実現し、ユーザ回路は動的再構成が行える。内蔵 FPGAと自立 FPGAには、ユーザ回路以外には共通のネットワーク制御回路が実装されている。PC-PC間、PC-FPGA間、FPGA-FPGA間での通信を行うため、ネットワーク上に流れる通信の内容としてはユーザ機能のデータ、コンフィギュレーションデータ、ユーザプロセス起動のためのコマンド・引数などが挙げられ、これらを同一のネットワークで扱うことが可能である。

本研究では、このうちの最も単純な構成として、このうちの一要素、つまり、PCO/FPGAO の要素のみを利用することにする。また、比較用システムとして、FPGAO を GPU に置き換えたものを利用する。このため、GPU を利用した場合と条件を等しくするために、PCO と FPGAO との接続には PCI Express を利用した。

図 1 PC-FPGA 複合クラスタ

## 3. 実験装置

本研究では、PCO として OS に Windows7, CPU に Core i7, メモリを 8GB 搭載した PC を利用した. FPGAO として Xilinx KC705 (FPGA: Xilinx Kintex7) を使用した. また, 比較用システムの GPU には NVIDIA GeForce

GTX 705 を使用した. システムの開発環境として, FPGA 開発は Xilinx Vivado 2014.2, ソフトウェア開発は Microsoft Visual Studio 2013 を使用した. PC 上の PCI Express スロットに FPGA ボードを接続し, PC 上のメモリから DMA 転送を用いて FPGA ボード上の DDR3 メモリに HD 動画像を転送し画像処理を行う.

なお、本研究で使用する FPGA ボードには DDR3 メモリが搭載されており、画像処理における計算用のデータ、計算結果等の格納に利用した.

# 4. システム構成

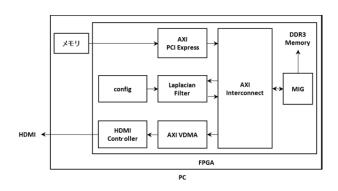

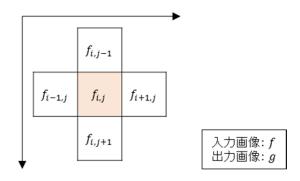

本研究で開発する画像処理システムの全体構成を図 2 に示す。PC 側に PCI Express 用の汎用ドライバをインストールし、C 言語によるプログラムから HD 動画像の送信を行う。AXI PCI Express は AXI と PCI Express を接続するためのコアであり、Xilinx CoreGen によって生成する汎用 PCIe-AXI インタフェースに改造を施し実装している。送信された HD 動画像は、メモリのハードウェア依存を吸収するための AXI インタフェースおよび MIG を介して DDR3 メモリに DMA 転送する。次に DDR3 メモリ上の画像を 1 フレームずつ Laplacian Filter により読み出して画像変換を行い、再び DDR3 メモリに書き戻す。ラプラシアンフィルタには、4 近傍ラプラシアンを利用する。つまり、図 3 のような画素の並びに対して、以下の式(1)を用いて変換後の画素値を計算した。

$$g_{i,j} = f_{i+1,j} + f_{i-1,j} + f_{i,j+1} + f_{i,j-1} - 4f_{i,j}$$

(1)

最後に、変換を施したフレームは MIG、AXI Interconnect を経由して、HDMI Controllerにより HDMI 信号に変換し、液晶モニタに出力する. なお、メモリは4重のリングバッファ構造としており、変換前の書き込み、読み出しフレーム、変換後の読み出し、書き込みフレームをそれぞれ別のメモリ領域に格納している.

図 2 システムの全体構成

図 3 ラプラシアンフィルタ

# 5. 実験結果

電源に消費電力計を接続し、消費電力を測定した. FPGA、GPU 未装着時 (PC0 のみ) の消費電力は 43[W]、FPGA を搭載したシステムでは 54[W]、GPU を搭載したシステムでは 80[W] となり、GPU を搭載したシステムが FPGAを搭載したシステムの約 1.48 倍の消費電力となっていた.

処理性能は FPGA を搭載したシステムでは 24[fps], GPU を搭載したシステムでは 31[fps]であったため, GPU を搭載したシステムが FPGA を搭載したシステムの約 1.3 倍の処理性能であった.

#### 6. まとめ

本研究では PC1台・FPGA1台の単純な構成で実験を行い、FPGAを搭載したシステムが低消費電力であることを確認した.

PC-FPGA 複合クラスタにおいて複数台の FPGA を用いて、GPU と同程度の処理性能を出す場合を想定しても、性能あたりの消費電力は FPGA を搭載したシステムのほうが小さくなると考えられる.

現在はオーバーヘッド等を考慮していない理論値であるため、今後の課題として PC-FPGA 複合クラスタに画像処理システムを実装し、実機での測定を行う必要がある.

### 文献

- [1] 青木圭一, 山際伸一, 和田耕一, 小野雅晃, "Maestro2 クラスタネットワーク向けメッセージパッシングライブラリの開発と評価," 信学論(D), Vol. J89-D, No.5, pp.919-931, May. 2006.

- [2] K. Nagar and J. Bakos, "A Sparse Matrix Personality for the Convey HC-1," Field-Programmable Custom Computing Machines (FCCM), 2011 IEEE 19th Annual International Symposium, pp. 1–8, May. 2011.

- [3] Andrew Putnam et al. "A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services," ISCA, 2014.

- [4] 尾崎 亮, 上嶋 明, 小畑正貴, "PC-FPGA 複合クラスタ の実現と評価," 信学論(D), vol.J96-D, No.5, May. 2013.