C-001

# 分岐予測ミスの偏りとローカル履歴の規則性を利用した分岐予測器の提案

A Branch Predictor Using Miss-prediction Bias and Rule of Local History

大下尊晃

孟林‡

小柳滋<sup>§</sup>

Takaaki Oshita

Lin Meng

Shigeru Oyanagi

#### 1. まえがき

分岐予測は、条件の成立 (Taken)、不成立 (NotTaken)による分岐方向と分岐先アドレスを予測することで制御依存を回避し、精度の高い予測を行うことで性能を向上させる.しかし、分岐予測ミスが起きた場合は性能が低下してしまう問題がある.これは、分岐予測ミスペナルティと呼ばれている.近年、プロセッサは高性能化に伴い、パイプライン段数や命令発行幅も増加しており、それにより分岐予測ミスペナルティも増加している.

予測ミスが発生する原因として、異なる分岐命令が同じPattern History Table (PHT)のINDEXに分岐結果を登録しているために生じる破壊的競合が挙げられる。本研究では、既存予測器を分析することにより判明した2つの特徴を利用する。1つ目の特徴は、予測ミスが一部の分岐命令で多発しており偏りが存在するという事、2つ目の特徴は、分岐命令のローカル履歴には部分的に規則性が存在するという事である。これらの特徴に基づいた分岐予測機構を従来の分岐予測器に追加し、破壊的競合を緩和することが目的である。具体的には、まず動的に予測ミスが集中している分岐命令を発見し、その分岐命令アドレスのローカル履歴から規則性を見つけ出し、それを用いて予測を行うことで分岐予測の精度向上を目指す。

# 2. 関連研究

分岐予測ミスペナルティを減少させるために様々な分岐予測器が提案されている。多くの分岐予測器は、単体予測器をベースにして、そこに分岐命令の特性を利用したハードウェア機構を追加することにより破壊的競合の緩和を実現している。

代表的な単体予測器としては、Bimodal 予測器やGshare 予測器がある. 本項では、これらの単体予測器に分岐命令の特性を利用したハードウェア機構を追加した分岐予測器である Bimode 予測器と Bimode-Plus 予測器について説明する.

# 2.1 Bimode 予測器

Bimode 予測器は分岐命令には偏りがあるという事実を利用している. 具体的には,分岐方向が Taken に偏った分岐命令と,NotTaken に偏った分岐命令が存在するということである.これらの偏りが逆方向である分岐命令が同一の PHT エントリを使用するとき破壊的競合が

多発する.この予測器は,Taken 用と R Not Taken 用に R つの R Gshare 予測器を用いることにより,破壊的競合を緩和することを目指している.最終的な予測は,R つの R Gshare 予測器の予測結果を R Choice PHT を用いて選択することで行う.

#### 2.2 Bimode-Plus 予測器

Bimode-Plus 予測器は、Bimode 予測器を更に強力にしたものである。具体的には、常に Taken、もしくは Not-Taken であるという極端な偏りのある分岐命令が存在する。この分岐命令の極端な偏りの特性を利用し予測を行うというものである。Bimode-Plus 予測器は Bimode 予測器に加えて、Bias Table の中に Taken flag と Not-Taken flag を用意し、極端な偏りのある分岐命令を検出する機構を持つ。検出された極端な偏りのある分岐命令は Bimode 予測器を用いずに予測し、それ以外の分岐命令を Bimode 予測器を用いて行うという手法で、破壊的競合の緩和を目指している。

# 3. 予測ミスの偏り

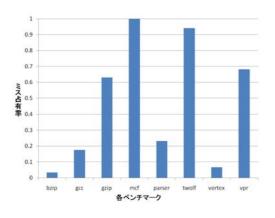

本章では,Bimode-Plus 予測器を解析することで予測ミスがどの程度偏っているかを示す.予測器のハードウェア量は  $32~\mathrm{KB}$ ,ベンチマークには SPECint2000 から bzip,gcc,gzip,mcf,parser,twolf,vpr,vortex を使用し,1 億命令実行する.そして,予測ミスが多発する上位  $16~\mathrm{I}$  個の分岐命令を抽出し,これらの予測ミスが全体の予測ミスに占める割合を調査する.その結果を,図  $1~\mathrm{I}$  に示す.横軸が各ベンチマーク名を,縦軸が最も多く予測ミスが発生する上位  $16~\mathrm{I}$  個の分岐命令の予測ミスが,全ミス数に占める割合を表している.図  $1~\mathrm{L}$  より,vpr では約 68%,twolf では約 94%,mcf では 100%に近い値を占めていることがわかる.これにより,予測ミスに偏りがあるという事実が確認できる.

# 4. ローカル履歴の規則性

本章では、予測ミスの多発する分岐命令のローカル履 歴の中に規則性があるという仮説の根拠を示す.

前章で予測ミスの偏りが特に多かった $\mathrm{mcf}$ ,  $\mathrm{twolf}$ ,  $\mathrm{vpr}$ で,予測ミス数が最も多い分岐命令のローカル履歴を参照し,その中で4 bit の規則性が見られる部分を数例挙げ,それがが全体に占める割合を示す。実際には全ての規則性部分が全体に占める割合は表 1 のものより遥かに多い。2 つだけでも,合計占有率は $\mathrm{mcf}$ で70.5%,  $\mathrm{twolf}$ で81.7%,  $\mathrm{mcf}$  で65.9%と高い数値を示している。

$<sup>^\</sup>dagger$ 立命館大学大学院理工学研究科, Graduate School of Science and Engineering, Ritsumeikan University

<sup>&</sup>lt;sup>‡</sup>立命館大学理工学部, College of Science and Technology, Ritsumeikan University

<sup>§</sup>立命館大学情報理工学部, College of Information Science and Engineering, Ritsumeikan University

図 1: 各ベンチマークの予測ミスの偏る分岐命令の予測 ミス占有率 (上位 16 個まで)

表 1: 規則性部分がローカル履歴に占める割合

|       | 規則性  | 占有率   |

|-------|------|-------|

| mcf   | 1110 | 46.1% |

|       | 0110 | 24.4% |

| twolf | 1111 | 50.1% |

|       | 1011 | 31.6% |

| vpr   | 1111 | 52.8% |

|       | 1010 | 13.1% |

Taken = 1, NotTaken = 0

#### 5. 提案手法

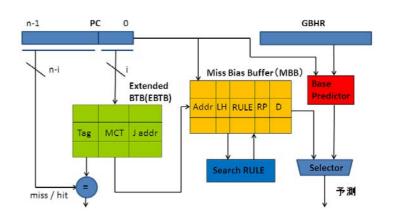

我々は、従来予測器に予測ミスの偏りとローカル履歴から発見した規則性を利用するハードウェア機構を追加した分岐予測器を提案する. 図2が、その提案手法を図で表したものである. Base Predictor が従来予測器となる.

予測の流れとしては、Tag, MCT(Miss Counter), Jaddr (分岐先のアドレス)で構成される Extended BTB (EBTB)を利用して、動的に予測ミスが集中している分岐命令を検出する. 具体的には、検出された分岐命令のコミット時に飽和カウンタの MCT(Miss Counter)を用いて Base Predictor の予測ミス数をインクリメントし、予め設定した閾値を超えることでミスの多発する分岐命令を検出する仕組みとなっている.

次に、Addr、LH、RULE、RP、D で構成される MBB (Miss Bias Buffer)を使用する. MBB は、予測ミスの多発する分岐命令の情報を格納するもので、Addr は分岐命令アドレス、LH は分岐命令のローカル履歴、RULE はローカル履歴から発見した規則性、RP(Rule Pointer)はRULEの現在位置、D(Digit)はRULEの桁数を示す.

EBTB で検出された分岐命令のアドレスを MBB へ登録した後,対応する分岐命令のコミット時に MBB の更新が行われて LH でローカル履歴が更新される. そのローカル履歴から Search RULE を使い規則性を発見する. 規

図 2: 提案手法のブロック図

則性の発見方法としては、ビットシフト演算を利用している。ローカル履歴を右にシフトさせたものとの XORをとった計算結果に桁数分の mask をとった結果が、0 ならば規則性が有りと判断し、それ以外はなしと判断するというものである。例えば、ローカル履歴が 001001001 の時、001 の 3 bit の時にルール有りと判断され、001 の繰り返しであると判断され、規則性:001 が生成される。最後に、得た規則性を MBB の RULE に格納し、RP で規則性の現在位置を確認しながら最終的な予測を行う。

この提案手法のメリットとしては、追加部分のハードウェア量が小さいため、コンパクトに実装できるというものがある。 具体的には,MCT が 4 bit のため EBTB に追加するメモリ量は RAM で 1 KB である。そして,MBB は Addr,LH,RULE が 32 bit で,RP と D が 5 bit で合計は 106 bit となり,エントリ数を 8 とすると,MBB 全体で 0.106 KB の CAM となる.

# 6. おわりに

現状では、SimpleScalar ツールキットを用いて、前章で紹介した提案手法の実装中である。実験結果は、後日報告する。

# 参考文献

- [1] 西岡 拓生, 孟 林, 小柳 滋, "分岐予測の成否パターンを用いた信頼性評価手法", SACSIS 2010, pp.87-88, May. 2010.

- [2] 仲沢由香里, 山名早人, "予測カウンタの偏向を利用 したハイブリッド分岐予測器", 早稲田大学院修士論 文, Feb. 2005.

- [3] 二ノ宮康之, 阿部公輝, "パーセプトロン分岐予測器 を用いた予測信頼性の動的判定に基づく電力削減", SACSIS 2009, pp.327-334, May. 2009.

- [4] 孟 林, 小柳 滋, "分岐予測ミスの偏りを利用した分岐 予測器の提案", 情報処理学会論文誌, to appear.