### 4J-3

# CoreSymphony P605 のフロントエンドの実装

# 坂口 嘉一 <sup>†</sup> 永塚 智之 <sup>†</sup> 吉瀬 謙二 <sup>†</sup> 東京工業大学 大学院情報理工学研究科 <sup>†</sup>

#### 1 はじめに

1つのチップに複数のコアを集積するチップマルチプロセッサ (CMP) が主流になっている. CMP は複数のスレッドを同時に実行することで,高い性能を達成する.しかし,アムダールの法則に示されるように,CMPにおいてもシングルスレッド性能は重要である.そこでCMPにおいて,我々は高いシングルスレッド性能を得るため,CoreSymphony[1][2] アーキテクチャを提案している.

我々は CoreSymphony アーキテクチャを適用したプロセッサ ( CoreSymphony P605 ) の FPGA に実装を目指している . FPGA に実装することで , ハードウェア量の評価に加え , 高速なシミュレーション環境として利用できる . 本項では , FPGA 向け実装のフロントエンド部分についての評価を行う .

# 2 CoreSymphony のフロントエンド構成

CoreSymphony アーキテクチャ(以下 CoreSymphony)では、複数個のコアが協調し、仮想的な発行幅の広い1つのコアとしてプログラムを実行可能である.

CoreSymphony におけるフロントエンドの特徴として,次に3つが挙げられる.(1)各コアが独立した命令の協調フェッチ.(2)命令を複数のコアに分散する命令ステアリング.(3)コアをまたぐ依存を考慮したレジスタリネーミング.

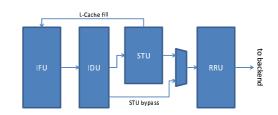

図 1 に CoreSymphony のフロントエンドの概略を示す.フロントエンドは,命令をフェッチする命令フェッチユニット (IFU),命令をデコードする命令デコードユニット (IDU),命令ステアリングを行うステアリングユニット (STU),レジスタリネーミングを行うレジスタリネーミングユニット (RRU)の4つのモジュールから構成される.

先に挙げた特徴の内,(1)は IFUが,(2)は STUが,(3)については RRUが担っている.以下では,この3つのモジュールについて述べる.

#### 2.1 命令フェッチユニット (IFU)

命令の協調フェッチを実現するため,IFU は通常の命令キャッシュ(conv.I-cache) に加え,ローカル命令キャッシュ(L-cache) を備えている.L-cache はトレースキャッシュの一種であり,フェッチブロック(FB)と呼ばれる命令トレース単位でラインを割り当てる.1 つのラインには,FB に含まれる命令の内,自コアにステアリングされたものと FB の制御情報が格納される.

CoreSymphony の命令フェッチは , L-cache のエントリ構築フェーズと L-cache からフェッチする協調フェッチフェーズに分けられる .

フェッチ時に L-cache にミスした場合 , エントリ構築 フェーズに遷移する . conv.I-cache から FB 全体をフェッチし , デコードとステアリングを行う . その後 , 自コア にステアリングされた命令と FB の制御情報を L-cache に格納する .

Implementation of CoreSymphony P605 frontend Yoshito Sakaguchi $^{\dagger}$ , Tomoyuki Nagatsuka $^{\dagger}$ , Kenji Kise $^{\dagger}$ †Tokyo Institute of Technology Graduate School of Information Science and Engineering

図 1: CoreSymphony アーキテクチャのフロントエンド の概略 . 4 つのモジュールからなる

L-cache にヒットした場合,協調フェッチが行われる. L-cache に格納されている命令はステアリング済であるため,命令はデコード後,STUをバイパスしRRUに送られる.協調フェッチの場合,自コアにステアリングされた命令のみをフェッチするため,フロントエンドの実質的なスループットが増大する.

### 2.2 ステアリングユニット (STU)

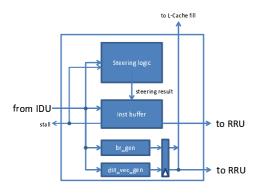

図 2 に , STU の概略を示す . CoreSymphony における命令ステアリングとは , 命令を実行するコアを決定する操作である . ステアリングは FB 単位で行う . ステアリングアルゴリズムにはリーフノードステアリング [1] を用いる .

また,STU ではステアリングと並行して FB の制御情報の生成も行う.制御情報には,FB が結果を生成する論理レジスタの番号や,トレース中の分岐に関する情報などが含まれる.

リーフノードステアリングは FB 内の命令を逆順に解析するため, FB に含まれる全命令が STU に到達するまで, ステアリング結果が得られない. そのため, STU は結果が得られるまで命令を蓄えるバッファが設けられている. ステアリング結果が得られた後, 自コアにステアリングされた命令をバッファから取り出し, 次のステージに送る.

IFU で L-cache から読みだされた命令は STU をバイパスする.そのため,STU でステアリングが行われている間に L-cache にヒットすると,命令の追い越しが発生する可能性がある.この状況を防ぐため,STU でステアリングが行われている間に,L-cache から読みだされた命令が IDU に到達した場合,IFU と IDU をストールさせる.

#### 2.3 レジスタリネームユニット (RRU)

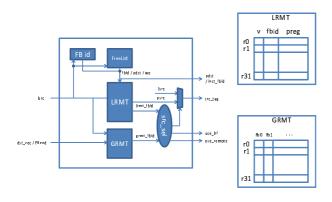

図 3 に RRU の概略を示す . RRU では , 命令の依存関係を解決する . CoreSymphony においてオペランドの供給元には , 物理レジスタファイル (PRF) , 論理レジスタファイル (LRF) , 他のコア (remote) の 3 種類が存在する . RRU において供給元を求め , ソースレジスタをリネームするタグを得る .

複数のコアで分散してプログラムを実行するため,コアを跨いだ依存が生じ得る.このような依存関係を追跡しつつ,ハードウェア規模を削減するため,CoreSymphonyでは 2way リネーミング [1] と呼ばれる手法で,レジスタをリネームする.

2way リネーミングでは, コア内の依存を表す ltag と

図 2: STeering Unit . ステアリングロジック, 命令バッファ, FB 制御情報生成部に分かれる.

図 3: Register Renaming Unit と GRMT および LRMT

フェッチブロック間の依存を表す  $\operatorname{gtag}$  の 2 種類のタグを用いて,依存関係を表現する  $\operatorname{ltag}$  は,自コアの物理レジスタ番号であり, $\operatorname{gtag}$  は論理レジスタ番号とその結果を生成する FB の番号を連結したものである  $\operatorname{LRMT}$  と  $\operatorname{GRMT}$  と呼ばれるテーブルで管理される  $\operatorname{LRMT}$  は  $\operatorname{ltag}$  に加え,そのレジスタに書き込む命令の FB 番号も記録される .

ソースレジスタのリネーム時には,LRMT と GRMT 両方を読みだす.いずれかのエントリが有効な場合,それぞれの FB 番号を比較し,GRMT から読みだした FB 番号の方が若い場合には,gtag にリネームされ,他のコアから値の供給を受ける  $(use\_remote)$  とマークされるそうでない場合は ltag にリネームされる.

LRMT と GRMT 両方のエントリが無効な場合, ソースレジスタは, リネームされず (論理レジスタ番号をとする) LRF から値を読みだす (use\_lrf) とマークされる. バックエンドの命令ウィンドウでは, タグと 2 種のマークを使用し,命令発行をスケジュールする.

#### 3 評価

ここでは,フロントエンドのハードウェア規模および動作周波数を評価する.実装は Xilinx 社の評価ボード  $\mathrm{ML}605$  に行う.論理合成には ISE 13.2 を使用する. conv.I-cache はダイレクトマップで,容量は  $4\mathrm{KB}$ ,ラインサイズは 2,L-cache はダイレクトマップで,256 エントリ( $1024\mathrm{word}$  分)とした.

#### 3.1 ハードウェア量

表 1 に論理合成の結果得られた , リソース占有量を示す . フロントエンド全体 (frontend) および , IFU, IDU, STU, RRU 毎のリソース占有量に加え , L-cache, conv.I-cache ステアリングロジック (leaf-node), STU 内の命令

表 1: モジュール別リソース占有量

| モジュール        | FF   | LUT  | BRAM |

|--------------|------|------|------|

| IFU          | 762  | 1366 | 33   |

| conv.I-cache | 71   | 100  | 3    |

| IFU.L-cache  | 359  | 647  | 18   |

| IDU          | 275  | 162  | 0    |

| STU          | 1232 | 2669 | 8    |

| leaf-node    | 855  | 2194 | 0    |

| inst-buf     | 63   | 279  | 8    |

| RRU          | 1244 | 4207 | 0    |

| grmt         | 268  | 823  | 0    |

| lrmt         | 382  | 1465 | 0    |

| frontend     | 3827 | 8791 | 0    |

| conventional | 4877 | 9335 | 31   |

バッファ(inst-buf), GRMT, LRMT についても占有量を求めた.

比較のため、2命令発行のアウトオブオーダコア(conventional)のリソース使用量を示す、これはパイプライン全体に命令、データキャッシュ(それぞれ4KB,ダイレクマップ)を含めた値である。

表から、CoreSymphonyのフロントエンドのみで、conventionalに相当するリソースを消費していることがわかる.conventionalには存在しないSTUおよび、複雑化したリネーム機構による増分が大きい.このオーバーヘッドは許容できるものではなく、ハードウェア量の削減が必要といえる.

# 3.2 動作速度

論理合成の結果によると,モジュール内での最長遅延は7.907ns(約126MHz)であった.L-cacheからのフェッチがクリティカルパスになっている.

conventional (コア全体)の動作周波数は約 $95 \mathrm{MHz}$ であるので,フロントエンドのモジュールが,今後クリティカルパスになる可能性は低いと考えられる.

#### 4 まとめ

CoreSymphony アーキテクチャのフロントエンド部分を論理合成し、ハードウェア規模を評価した、その結果、動作周波数に悪影響を与える可能性は低いと分かった、一方、ハードウェアの増加量が多く削減が必要といえる、今後は、バックエンドの実装を進め、コア全体の動作を目指す予定である、

謝辞 本研究の一部は科学研究費補助金(課題番号:22700046 若手研究(B))による.

# 参考文献

- [1] 若杉他.調可能スーパースカラ CoreSymphony 情報 処理学会論文誌コンピューティングシステム, Vol.3, No.3, pp. 67-87 (September 2010)

- [2] Nagatsuka et al. CoreSymphony: An Efficient Reconfigurable Multi-core Architecture international Workshop on Highly-Efficient Accelerators and Reconfigurable Technologies (HEART2011), pp. 29-34 (June 2011)