# シリアル伝送への混入雑音を除去する多数決回路の特性評価 Performance Analysis of the Majority Voting Circuit for Serial Transfer Noise Reduction

田村 修†

Osamu Tamura

## 1. はじめに

PC と周辺機器,あるいは組込み機器と周辺デバイスとの通信においては、多相化、多重化を行わない簡易な有線通信が多用される。シリアル化したデータビット列(NRZ符号)を接地基準に対し片側電圧振幅のまま送受信するものは、ディジタル変調方式としてはベースバンド OOK(On-Off Keying)方式に分類される[1]. その基本動作はシフトレジスタから二値信号を送出し、受信側でサンプリングしてシフトレジスタに格納し復号するものである.

低速度域の通信に使われる調歩同期式のインターフェース実装の多くにはオーバーサンプリングによる多数決回路が内蔵され、二値化後の受信データから雑音パルスを除去している[2]. この回路動作の雑音依存性を理論解析および実験によって示す.

## 2. 二値伝送路のビット誤り

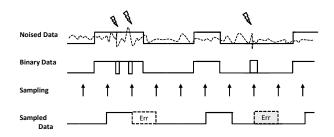

送出された二値の符号系列は伝送路での減衰および混入維音により波形に歪が生じ、受信側での復号に誤りを生じる.ベースバンド OOK においては受信信号に対し、帯域制限フィルタを通さずに振幅中央付近を閾値とする二値化を行うことが多い.このときデータに重畳された雑音成分によって、符号ビット内に部分的な反転状態が生じる.これがサンプリング点に重なれば、復号時の符号誤りあるいは位相ゆらぎ(ジッタ)となる(図 1). 雑音パルスを含む二値信号を一定の間隔でサンプリングしてシフトレジスタに取り込む場合、サンプリング点が雑音パルスと重なる確率は、単位時間あたりの雑音パルス幅の総和の占める割合に等しい.これはまた、平均の雑音パルス幅と単位時間あたりの雑音パルス発生回数の積に相当する. 雑音除去においては、雑音パルス時間の総量、もしくはサンプリング点にかかる雑音パルスを減らす工夫が必要となる.

通信システムの伝送能力の評価方法のひとつに、伝送ビット数に対する誤りビット数の割合(ビット誤り率: BER)がある。これは伝送ビット総数における誤って受信されたビット数の割合であり、単位時間あたりの反転ビット時間の割合である。BER 値が小さいほど優れた伝送特性となり、例えば有線での実用的な通信においては一般に BER  $10^5$ 以下が必要とされている。雑音の多い伝送路ほど BER 値を十分に下げ、符号訂正や再送の負担を減らすことが求められる。

伝送路に生じるデータ毀損を除去する能力は、伝送路上の信号に任意の BER となる雑音信号を合成し、受信側の雑音低減回路を通過後の BER 値と比較することにより評価する. BER の減少比が雑音低減回路での減衰率となる.

# 3. 二値伝送路の雑音モデル

ここでは伝送路への混入雑音によって、二値化後の信号 の論理レベルが部分的に毀損し反転する状況での雑音モデ ルについて述べる.

伝送路に生じる雑音は、発生間隔や持続時間の規則性の有無で大別される.ランダムな雑音とは、雑音の発生がそれ以前の雑音発生状況に依存しない無記憶性のものであり、熱雑音などガウス性のものと電源スイッチ開閉など突発的に生じるインパルス性のものがある.これらを複合したMiddleton Class-A モデルが狭帯域無線通信などの解析に使われている[3].また、電動機やエンジンなどから発生する電磁パルスなど周期性、連続性があるバースト雑音は、マルコフ過程を考慮したモデルを用いて解析されることも多い[4].バースト性雑音は制約があるランダム性雑音に近似できる側面がある.

ランダム雑音を含む信号を二値化すれば、判定閾値を超える雑音が加わった区間が反転した二値信号が得られる.インパルス雑音は Middleton Class-A モデルでは分散が大きいガウス分布とされるが、ガウス分布の裾部分で閾値越えとなる区間の生起間隔が指数分布に近似され得ることは数値シミュレーションで確認できる.また空電雑音の包絡線を任意レベルでスライスして得られるパルスの幅が、指数関数で近似されることは文献[5] に示されている.よってランダム雑音を重畳したデータが二値化されて出現する雑音パルスにおいても、ポアソン到着かつ幅が指数分布のランダム性を仮定することは妥当であると考えられる.

ポアソン到着,指数分布の確率密度関数はいずれも式(1)で表され,これを積分した分布関数は式(2)となる.

$$f_{(x)} = \lambda e^{-\lambda x} \tag{1}$$

$$F_{(x)} = 1 - e^{-\lambda x}$$

$(x \ge 0)$  (2)

式(1) の期待値は  $1/\lambda$  であり、これはパルス到着の平均間隔あるいは平均パルス幅となる.

図 1 雑音による二値化信号の部分反転 Fig.1 Partial bit toggling on noised binary signal

<sup>†</sup>有限会社リカージョン, Recursion Co., Ltd.

<sup>†</sup>金沢工業大学, Kanazawa Institute of Technology

# 4. オーバーサンプリングによる多数決回路

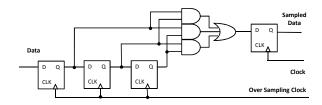

オーバーサンプリングによる多数決回路を図 2 に示す. データビット伝送速度の 8,16 倍などのクロック周波数でサンプリングし,3 連続サンプルの多数決値を出力する回路である.サンプル間隔に満たない雑音パルスの多くは阻止されるが、次のパルスが続けてサンプル点にかかれば短いパルスであっても通過する.2 サンプル点で一致すればサンプル間隔の幅のパルスが出力される.

本回路は入力 3 値が D-FF で固定されて多数決となるため全体として 3 サンプル時間の遅延が生じるが、出力を取り込むシフトレジスタのクロックエッジがオーバーサンプリングのクロックと一致するならば初段の D-FF は不要となる.

# 5. ビット誤り率の導出

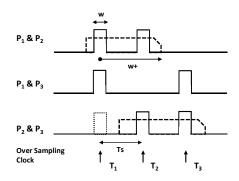

多数決回路の特性を, 雑音パルスが回路を通り抜ける確率として導出する. オーバーサンプリングによる 3 連続サンプル点の 2 箇所に雑音パルスが重なる確率を求める(図3).

発生する雑音パルスがサンプル点  $T_n$  を内包する確率を $P_n$  とおき、またパルスが  $T_n$  を内包する条件のもとに同しもしくは次のパルスが  $T_{n+1}$  または  $T_{n+2}$  を内包する確率を $T_{m/n}$  とする、雑音パルスが二つのサンプル点 n, m を内包する確率  $P_{nm}$  は式(3)となる.

$$\begin{cases} P_{11} = P_1 \cdot P_{2/1} \\ P_{13} = P_1 \cdot P_{3/1} \\ P_{23} = (1 - P_1) \cdot P_2 \cdot P_{3/2} \end{cases}$$

(3)

また,  $P_2 \cdot P_{3/2} = P_1 \cdot P_{2/1}$  であるから

$$P = P_{11} + P_{13} + P_{23}$$

=  $P_1 \{ (2 - P_1) \cdot P_{2/1} + P_{3/1} \}$  (4)

ここで雑音パルスの平均到着間隔を Tp (=1/ $\lambda$ ), 平均パルス幅を w, また, サンプル間隔を Ts とする. このとき

$$P_1 = w/Tp \tag{5}$$

である.また,ポアソン到着において連続パルスが二つのサンプル点に係る確率は,最初のパルス到着から(Ts-w)時間経過の後,w時間内につぎのパルスが到着する条件付き確率であるから,式(6)が得られる.

$$P_{(Ts-w < X \le Ts|X > Ts-w)} = \frac{\int_{Ts-w}^{Ts} f(\tau) d\tau}{1 - F(Ts-w)} = 1 - e^{-w/Tp} \quad (6)$$

図 2 オーバーサンプリングによる多数決回路 Fig.2 The oversampled majority voting circuit

図 3 多数決回路による雑音パルスの残存確率 Fig.3 Winning probability of the majority voting circuit

これはある時点でのランダムパルスの発生確率が直前のパルスからの経過時間(Ts)に無関係であること、つまりパルスの発生間隔が無記憶性であることを意味する[6].

単一のパルス幅で 2 サンプル点を内包する確率も,指数分布の無記憶性に基づいて求める(図 3 点線). あるサンプル点以前に生じたパルスがつぎのサンプル点まで持続する確率は,最初のサンプル点を起点として幅が Ts 以上となる確率であるから,式(7)を得る.

$$P_{(w+>Ts)} = 1 - F_{(x)} = e^{-\lambda x} = e^{-Ts/w}$$

(7)

式(6),(7) より

$$P_{2/1} = (1 - e^{-w/Tp}) + e^{-Ts/w}$$

(8)

$$P_{3/1} = (1 - e^{-w/Tp}) \tag{9}$$

となる. ここで雑音密度を A とし

$$A = \frac{w}{Tp}, \qquad S = \frac{Ts}{w} \tag{10}$$

と置けば式(4),(5),(8),(9)より

$$P = A\{(3-A)(1-e^{-A}) + (2-A)e^{-S}\}$$

(11)

$\mathbf{w} \ll Tp$  とすれば  $\mathbf{A} \ll \mathbf{1}$  であるから式(12) が得られる.

$$P \cong A(3A + 2e^{-S}) \tag{12}$$

指数の項は、雑音パルスの平均幅が広がるもしくはサンプル間隔が狭まって複数のサンプル点に跨り易くなるほど通り抜けの確率が高まることを表している.

また、サンプル間隔がパルス幅より十分に大きいのであれば、 $\mathbf{w} \ll Ts$  として式(13)に近似される.

$$P \cong 3A^2 \tag{13}$$

雑音密度 A は単位時間あたりのビット反転時間に相当し、 雑音混入信号を二値化して直接にシフトレジスタ入力した 場合の BER である. 多数決回路を通すことにより BER は 減少するが、この度合いがもとの BER 値に依存すること から、雑音が多い状況では雑音低減効果が低いことが示さ れている. 例えば A が 1% なら出力の BER は 0.03% とな るが、10% なら 3% への改善となる.

#### 6. 回路特性のシミュレーション

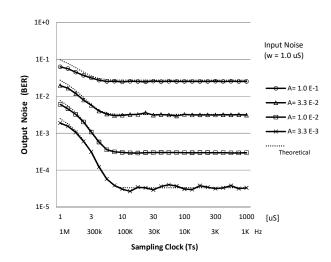

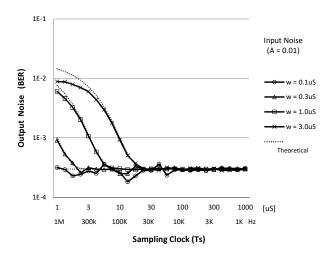

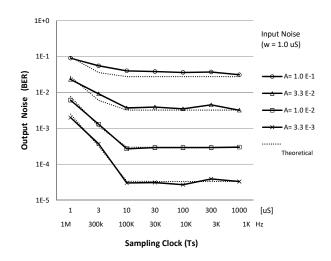

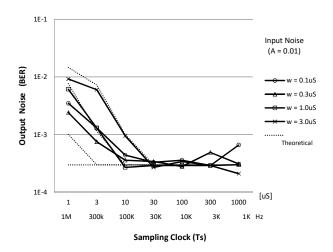

雑音パルスの到着間隔および幅を指数分布となる乱数によって生成し、オーバーサンプリングによる多数決回路を 通過するパルスの割合をシミュレートした.

逐次生成した雑音パルスの発生時刻と幅のなかに定間隔のサンプリング点が含まれるか判定し、多数決回路の入力とする。多数決回路を通過するパルスの数を集計し、サンプリングクロック数との比率、つまりは雑音除去後の BER 値が導出される。結果は図 4 および 5 のとおり式(11) (図中の点線) によく一致した結果が得られた。サンプル間隔 Ts が短い領域での誤差は、シミュレーションや実機評価では近接し過ぎたパルスが重ならないよう間隔を補正したことに起因する可能性がある。

なお、ここでは伝送データを 0 値とし雑音パルスのみを 多数決回路に入力してシミュレートした.

図 4 雑音密度と雑音残存率 (シミュレーション) Fig.4 Simulated BER by noise density

図 5 雑音パルス幅と雑音残存率 (シミュレーション) Fig.5 Simulated BER by noise pulse width

#### 7. 実機による特性評価

実際の回路を用いて多数決回路の雑音除去特性を計測した.数理的な解析の妥当性を確認するとともに,現実の回路動作におけるパルス応答時間の非対称性なども評価する.

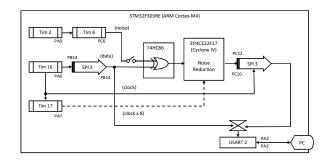

実装した評価システムは、疑似乱数系列で生成したデータをマイクロコントローラ内蔵の SPI で送出し、乱数生成した雑音パルスを合成した後に多数決回路を通し、別の SPI で受信して誤り率を計測する。確率分布に沿った乱数 生成に浮動小数点演算や数学関数を要するため、FPU 内蔵のマイクロコントローラ ARM Cortex-M4 を 72MHz 駆動し、内蔵の周辺機能を活用した(図 6). 周辺機能の制御のほとんどを DMAC が担うため、CPU 負荷は低く抑えられている.

まず、疑似一様乱数によるテストパターンを生成しシリアル送出する. さまざまなビットパターンのデータを偏りなく生成するため、Xor-shift 法による 2<sup>32</sup>-1 周期の疑似一様乱数生成器(PRBS)をプログラムした. この 16bit データをマイクロコントローラ内蔵の SPI により NRZ 符号としてシリアル送出する. SPIクロックは 125Hz-125kHzをタイマで生成し SPI に外部供給する. 送受クロックをタイマから供給することや雑音低減回路の遅延を考慮して、送受信には個別の SPI を使用した. SPI の入力段は、シュミットトリガ経由でセットアップ時間 3nS、ホールド時間4.5nSのシフトレジスタに接続されている.

雑音パルスの設定では BER 値およびパルスの平均幅 (100nS-3.0uS) を指定し、パルスの平均間隔を求める. 乱数をもとに指数分布となる間隔と幅を算出し、高機能タイマの連結駆動によってパルスを生成する. なお、パルス幅の指定範囲は、産業機器の耐性試験に用いられる値を参考に実装した.

生成した NRZ 符号と雑音パルスはマイクロコントローラ外部で XOR 合成する. この部分は FPGA に含めず標準ゲートロジック 74HC86 による独立した回路として動作タイミングの再現性を確保した(出力上昇および下降時間は10nS 未満).

評価対象となる雑音低減回路は FPGA により構成する. 雑音合成されたデータ信号とオーバーサンプリングのクロック信号を入力とし、多数決回路を通してデータ信号を出力する. ここでは 3 入力 2 一致の多数決回路を Altera Cyclone IV に実装した. 駆動には、テストパターン送出クロックに連動する 8 倍クロックをマイクロコントローラから供給した.

図 6 誤り率評価システム Fig.6 The Error Rate Evaluation System

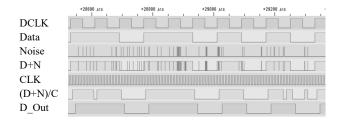

図 7 データ信号への雑音パルスの合成と除去 Fig.7 Waveforms of noise composed/reduced data

動作中の波形例を図7に示す.符号系列に合成した雑音パルスの多くが、オーバーサンプリング後に多数決回路を通すことで削減されている.

実機評価による雑音残存率は概ねシミュレーションと同様であるが、雑音パルス幅についてはデータ速度が遅い領域でエラー検出に時間を要し、ばらつきが多い結果となった(図8および9).

図 8 雑音密度と雑音残存率(実機評価) Fig.8 Measured BER by noise density

図 9 雑音パルス幅と雑音残存率 (実機評価) Fig.9 Measured BER by noise pulse width

## 8. まとめ

ベースバンド OOK 通信で雑音除去に用いられるオーバーサンプリングによる多数決回路について、ランダム雑音における動作特性を解析し評価した。まずポアソン過程に基づいて雑音パルスの残存率を確率的に求め、雑音密度が高いもしくは平均パルス幅が長いと雑音除去能力が低下することを示した。つぎに実際の回路動作を模したシミュレーションを行い、さらには実際のハードウェアによっても同様の結果が得られることを確認した。

本研究は外部クロック同期式通信の雑音軽減機構を検討する過程で分析を行ったものである. 現在, 完全一致で出力値を更新する多段型フィルタについて評価を進めている. 今後は 特性の異なるランダム雑音を複合した場合やバースト性の雑音についても雑音低減回路の特性を数理的に解析し実証する予定である.

# 文 献

- [1] 宮崎誠一,マイクロコンピュータ・データ伝送の基礎と実際,、CQ出版,東京,1984.

- [2] Atmel, "8-bit AVR Microcontroller with 2K Bytes In-System Programmable Flash ATtiny2313/V," Microchip Datasheet, , Rev.2543M, October 2010.

- [3] Thokozani Shongwe, A. J. Han Vinck, and Hendrik C. Ferreira, "A Study on Impulse Noise and its Models, "SAIEE Africa Research Journal, Vol.106, Issue 3, pp.119-131, September 2015.

- [4] 笹岡秀一, "ディジタル伝送路誤り系列モデルの調査,"電波研究所季報, Vol.32, no.162, pp.47-53, March 1986.

- [5] 仲井猛敏, "Poisson 雑音過程におけるパルス幅分布 理論,"電気通信学会雑誌, Vol.47, no.3, pp.289-293, October 1963.

- [6] 吉岡良雄,電気系の確率とその応用,,森北出版, 東京,1987.